概述

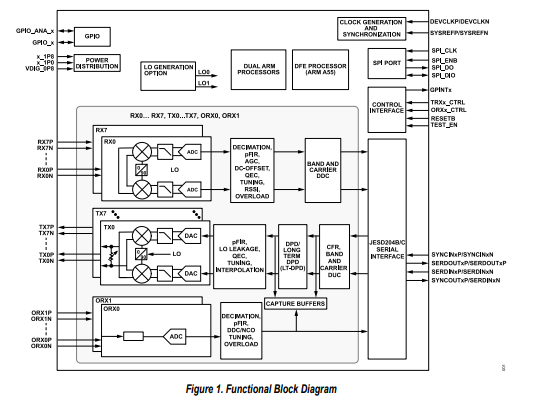

ADRV9040是一款高度集成的片上系统(SoC)射频(RF)捷变收发器,配有集成式数字前端(DFE)。SoC包含8个收发器、2个用于监测发射器通道的观测接收器、8个接收器、集成LO和时钟合成器,以及数字信号处理功能。SoC满足蜂窝基础设施应用(包括小型蜂窝基站无线电、宏3G/4G/5G系统和大规模MIMO基站)所需的高射频性能和低功耗。

数据表:*附件:ADRV9040具有DFE、400MHz iBW射频收发器的8T8R SoC技术手册.pdf

Rx和Tx信号路径采用零中频(ZIF)架构,提供适合连续和非连续多载波基站应用的宽带宽和动态范围。ZIF架构具有低功耗+射频和带宽灵活等优点。由于没有混叠和带外图像,因而不需要抗混叠和图像滤波器。这样就减小了系统尺寸和成本,同时支持与频带无关的解决方案。

该器件还包括两个宽带宽观测路径接收器子系统,用于监测发射器输出。该SoC子系统包括自动和手动衰减控制、直流失调校正、正交误差校正 (QEC) 以及数字滤波功能。此外,还集成了提供一系列数字控制选项的GPIO。

双LO功能、额外的LO分频器和宽带宽操作支持多频段功能。这样就在可调谐范围内有4个单独的频带曲线1,从而尽可能提高用例灵活性。

SoC具有完全集成的数字前端(DFE)功能,包括载波数字上/下变频(CDUC和CDDC)、削峰(CFR)、数字预失真(DPD)、闭环增益控制(CLGC)和电压驻波比(VSWR)监控。

ADRV9040的CDUC功能对目标频带内的单独分量载波进行滤波和放置。CDDC功能具有8个并行路径,对每个载波进行单独处理,再通过串行数据接口发送。

CDUC和CDDC降低了非连续载波配置中的SERDES接口数据速率。与基于FPGA的等效实现方案相比,这种集成设计还降低了功耗。

ADRV9040的CFR引擎降低了输入信号的峰均比(PAR),支持实现更高效率的传输线路升级,同时降低了基带处理器的处理负荷。

SoC还包含完全集成的DPD引擎,用于功率放大器(PA)线性化。DPD支持高效功率放大器,可减少基站无线电的功耗,以及与基带处理器接口所需的SERDES通道数量。DPD引擎包含一个长期专用的DPD (LT-DPD)模块,可为GaN PA提供支持。ADRV9040利用其LT-DPD模块解决了GaN PA的电荷捕获特性;因此改善了辐射和EVM性能。SoC包括一个ARM Cortex-A55四核处理器,可独立提供DPD、CLGC和VSWR监控功能。专用处理器与DPD引擎一起提供行业出色的DPD性能。

串行数据接口包括八个串行器通道和八个解串器通道。该接口支持JESD204B和JESD204C标准,支持固定和浮点数据格式。浮点格式使内部自动增益控制(AGC)对基带处理器可见。

ADRV9040可直接由0.8V、1.0V和1.8V稳压器供电,并通过一个标准SPI串行端口进行控制。全面的节电模式可尽量降低正常使用时的功耗。该器件采用27mm × 20mm、736引脚球栅阵列封装。

特性

- 8个差分发送器(Tx)

- 8个差分接收器(Rx)

- 2个观察接收器(ORx)

- 单频段和多频段(N x 2T2R/4T4R)能力

- 可调范围^1^内4个波段轮廓

- 调谐范围:650 MHz至6000 MHz

- 400MHz iBW DPD支持

- 通过硬件加速电荷捕捉纠正算法实现GaN PA支持

- 支持JESD204B/JESD204C数字接口

- 适用于所有LO和基带时钟的多芯片相位同步

- 完全集成的N部射频频率合成器

- 简化系统散热解决方案

- 所有区块实现13W功耗^2^

- 110°C最高结温,工作温度最高达125°^3^

- 完全集成的DFE(DPD、CDUC、CDDC、CFR)引擎,免除FPGA的需要,SERDES通道速率减半

- DPD自适应引擎,实现功率放大器的线性化

- CDUC/CDDC——每个Tx/Rx通路最多8个分量载波(CC)

- 多级CFR引擎

- 完全集成的时钟频率合成器

应用

- 3G/4G/5G TDD/FDD小型蜂窝、大规模MIMO和宏基站

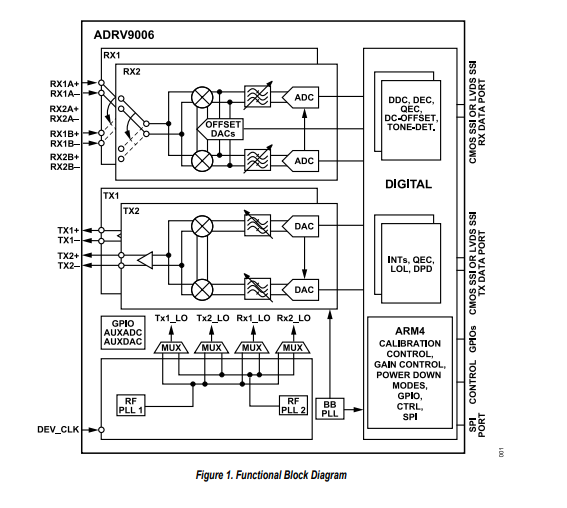

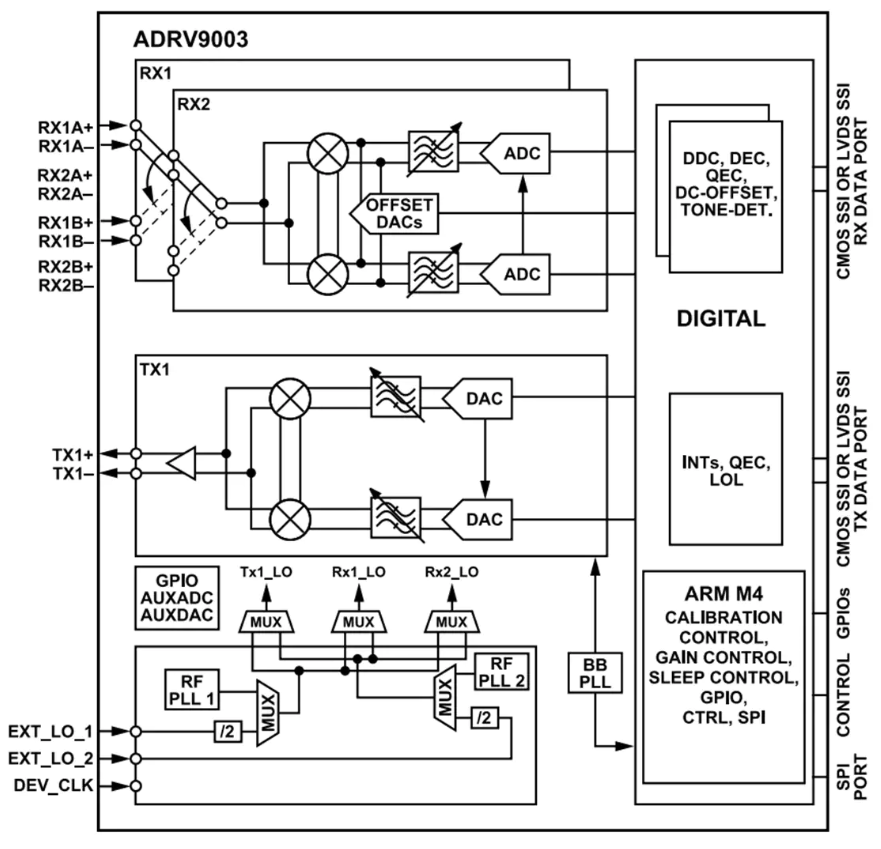

功能框图

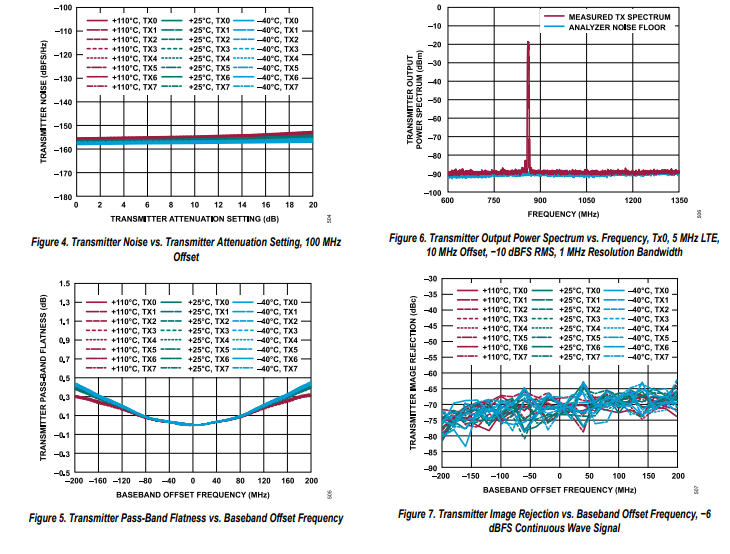

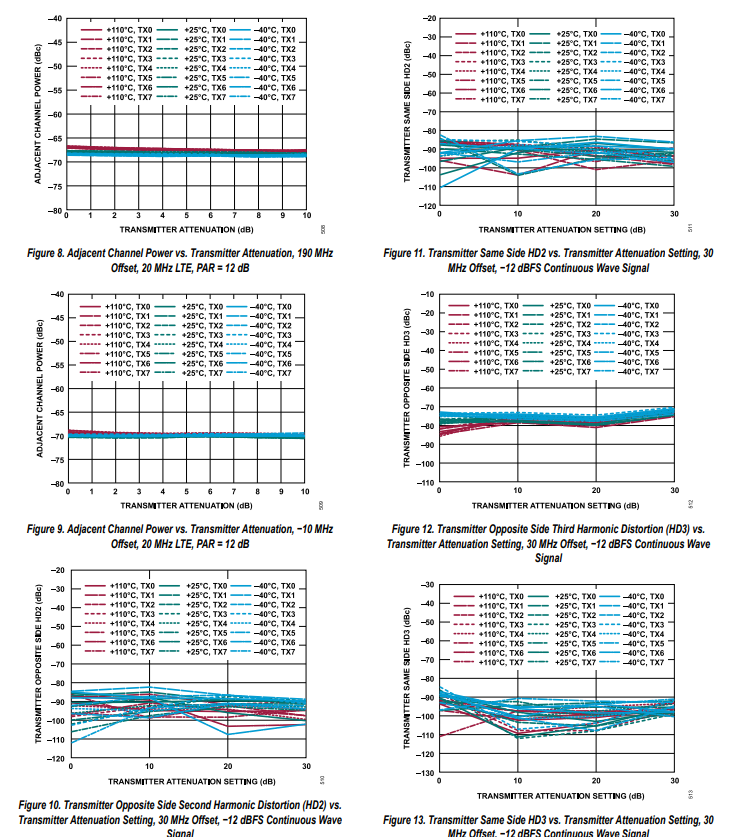

典型性能特性

850兆赫兹频段

温度设置指的是芯片温度。除非另有说明,所有本振(LO)频率均设置为850兆赫兹 。除非另有说明,观测接收机测量采用5898.24兆赫兹的采样频率。对于衰减设置高于20分贝的接收机,其线性度性能测量受限。

概述

ADRV9040是一款高度集成的射频收发器,能够针对各种应用进行配置。该器件集成了射频、混频信号和数字模块所需的所有发射器、射频接收器和观测接收器功能,可在单芯片中实现。它符合3GPP 3G4G/5G蜂窝标准,适用于时分双工(TDD)模式。

一个观测接收器通道监测发射器输出,并提供跟踪校正功能,如直流失调、正交误差和增益平衡。该观测接收器通道可在各种温度和输入信号条件下进行测量。固件随器件一同提供,可实现初始化和校准功能,无需用户干预。此外,该器件还包括测试模式,允许系统设计人员在调试和优化无线电配置时使用。

ADRV9040包含八个高速串行接口(SERDES)链路,用于发射机和观测接收器通道之间的四对高速链路共享。

发射器

ADRV9040包含四个独立的发射机通道。每个发射机通道提供数字处理、混频信号和射频模块,以实现直接转换系统,同时共享一个通用频率合成器。SERDES链路输出的数字数据通过一个数字处理模块,该模块包括可编程半带滤波器、插值级和射频滤波器,以及可编程FIR滤波器,其变量间隔采样率可达24倍。

数字输出连接到数模转换器(DAC),DAC采样率为244.140625 MSPS或389.3616 MHz。在同相(I)和正交(Q)通道中,在基带混频器信号链中执行数字校正。

混频转换后,I和Q信号经过滤波,以消除采样伪影,并馈送到上变频混频器。每个发射机提供一个宽衰减调整范围,以帮助设计人员优化信号与噪声比(SNR)。

接收器

ADRV9040包含四个独立的接收器通道。每个通道包含接收射频信号并将其转换为数字数据所需的所有模块,该数字数据由基带处理器进行后续处理。每个接收器提供I和Q混频器,以将接收到的信号下变频至基带进行数字化。

有两种增益控制选项,如下所示:

- 用户可以使用其基带处理器实现自己的增益控制算法,采用手动增益控制模式。

- 用户可以使用片上AGC(自动增益控制)。

通过将每个增益控制设置映射到特定的衰减级别,在接收信号路径中优化性能。此外,每个通道独立执行信号功率测量功能。直流失调跟踪和所有通道的连续测量用于自动校准。

接收器包括模数转换器(ADC)和可调节采样率,可从先进先出(FIFO)缓冲器接收信号。这些设置可以通过串行端口接口(SPI)进行配置。

抽取滤波器由数字滤波器块实现。通过改变数字滤波器块的系数来调整抽取率,以产生所需的输出数据速率。所有接收器输出都连接到SERDES模块,在那里进行格式化和串行化,以便传输到基带处理器。

观测接收器

ADRV9040提供独立的观测接收器输入。与接收器通道不同,观测接收器通道采用直接采样。射频ADC消除了对本地振荡器(LO)的需求,该本地振荡器通常具有缓冲级。该通道包含一个可编程衰减器,在模拟域中提供约16 dB的衰减。

参考时钟输入

ADRV9040需要连接到器件的两个不同时钟。时钟输入必须在61.44 MHz和491.52 MHz之间,因为该信号会生成射频本地振荡器(LO)和内部采样时钟。

合成器

ADRV9040包含多个分数N分频锁相环(PLL),用于生成信号路径的射频本地振荡器(LO)和所有内部时钟源。该组PLL包括两个射频PLL、两个SERDES PLL、一个内部时钟PLL和一个系统时钟PLL。每个PLL都可独立控制,因此无需外部合成器来设置频率。

射频合成器

两个射频合成器使用分数N分频PLL生成多个接收器和发射器通道的射频本地振荡器(LO)。分数N分频压控振荡器(PLL)结合了四芯内部电压控制振荡器(VCO)和环路滤波器,能够生成低相位噪声信号,而无需外部组件。多个器件上的射频本地振荡器(LO)可以进行相位同步,以支持有源天线系统和波束成形应用。

SERDES合成器

SERDES合成器使用单芯VCO分数N分频PLL来生成SERDES物理层所需的时钟速率。

-

soc

+关注

关注

38文章

4406浏览量

223186 -

RF

+关注

关注

65文章

3176浏览量

169188 -

射频收发器

+关注

关注

4文章

264浏览量

25878

发布评论请先 登录

RadioVerse生态系统中的宽带收发器分享!

ADRV9002射频收发器英文手册

74AVC8T245-Q100具有可配置电压转换的8位双电源转换收发器规格书

74AVC8T245具有可配置电压转换的8位双电源转换收发器规格书

ADRV9040具有DFE、400MHz iBW射频收发器的8T8R SoC技术手册

ADRV9040具有DFE、400MHz iBW射频收发器的8T8R SoC技术手册

评论