文章来源:学习那些事

原文作者:前路漫漫

本文介绍了半导体封装中的装片。

装片概述

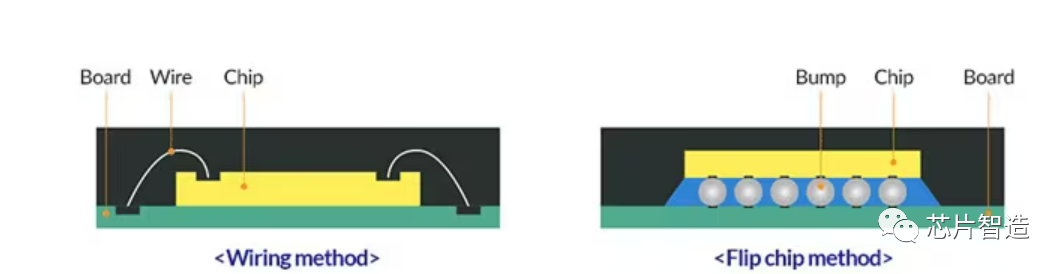

装片(Die Bond)作为半导体封装关键工序,指通过导电或绝缘连接方式,将裸芯片精准固定至基板或引线框架载体的工艺过程。该工序兼具机械固定与电气互联双重功能,需在确保芯片定位精度的同时,为后续键合、塑封等工艺创造条件。

装片质量双维度标准

1.产品性能要求

机械可靠性:芯片与载体连接需承受≥50MPa剪切强度,确保封装应力下无位移

热/电传输性:热阻AVBE≤0.5℃/W,接触电阻Vc≤50mΩ,满足功率器件散热需求;

工艺适配性:焊料层厚度控制在20-50μm,平整度误差<±5μm,保障键合精度。

2.工艺执行规范

芯片状态:杜绝沾污(颗粒度<0.5μm),裂纹(线宽>10μm 需判废),倒装等12类缺陷

载体标准:引线框架氧化层厚度<5nm,基板翘曲度<0.1%

焊料质量:空洞率<5%(超声检测标准),结球高度控制在焊料层厚度 ±15% 范围内。

3.理想焊料材料特性

高固溶度:在硅/锗基芯片中溶解度>1.2at.%,降低欧姆接触势垒

低蒸气压:300℃时<10^-5 Pa,避免高温制程中材料损耗

匹配熔点:Sn-Pb系焊料熔点(183℃)需低于Al-Si共晶温度(577℃)

力学适配:热膨胀系数与芯片(3ppm/℃),基板(6ppm/℃)差异<20%,抑制热应力

主流装片技术

1.胶联装片工艺

导电胶:含银/铜纳米颗粒,填充量60-80,固化后体电阻率<10^-3Ω·cm

绝缘胶:环氧树脂基,介电常数ε<3.5,适用于信号隔离场景

工艺优势:室温固化(80-120℃)兼容热敏芯片,贴片精度±10μm,适合高密度封装

2.焊料装片技术

典型材料:Sn63Pb37共晶合金(熔点183℃),含Bi改性版本可降至138℃

工艺要点:回流焊峰值温度(210-230℃)需精准控制,避免 IMC 层(金属间化合物)过厚(>3μm)导致脆性失效

3.共晶装片工艺

原理机制:利用Au-Si(3.2at.%Si)在363℃形成共晶反应,实现原子级冶金结合

性能优势:热阻低至 0.2℃/W,剪切强度>80MPa,广泛应用于高功率激光器封装

4.银烧结技术

纳米材料体系:银颗粒粒径<100nm,通过压力(5-20MPa)与低温(200-250℃)实现烧结

技术突破:导热率达200W/mK,电导率10^7 S/m,满足SiC模块175℃长期服役需求

胶联装片

1.导电胶核心构成与作用机制

导电胶作为胶联装片的核心材料,本质是由基体树脂与导电填料构成的复合体系。其工作原理基于 “渗流理论”:当导电填料(如银粉)含量超过临界体积分数(通常 60%-80%)时,粒子间相互接触形成连续导电通路,从而实现芯片与载体间的电气连接。基体树脂不仅提供黏附力固定导电粒子,还需具备良好的流动性以确保填充性,并在固化后形成稳定的机械支撑结构。

2.基体树脂分类与特性

环氧树脂系:以双酚A型(E-51)和双酚F型最为常用。双酚A型环氧树脂环氧值0.48-0.54eq/100g,凝胶时间(120℃)约15-20分,适用于中低温固化工艺;双酚F型因分子结构更紧凑,黏度可低至1500-3000cps,特别适合高精度点胶制程。

聚酰亚胺系:玻璃化转变温度(Tg)超250℃,耐温性能优异,但需高温(300℃以上)亚胺化反应,限制其在热敏器件中的应用

有机硅系:低应力(模量<1GPa),高绝缘(体积电阻率>10^15Ω?cm),常用于MEMS器件封装,但导电性相对较弱

3.导电填料关键参数

银粉形态差异:球状银粉(粒径1-5μm):比表面积小,氧化速率<0.01%/ 年,接触电阻稳定。树枝状银粉(枝晶长度10-20μm):填充效率高,可减少树脂用量,但需控制团聚现象。鳞片型银粉(径厚比50-100):形成片状搭接网络,适用于各向异性导电胶(ACA)。

表面处理技术:通过化学镀镍(Ni)或抗氧化剂包覆,可将银粉在 85℃/85% RH 环境下的氧化增重率从5%降至0.5%以下

4.绝缘型填料特性

氧化硅(SiO?):热导率1.2-1.5W/mK,硬度HV800-1000,填充量40%时热阻可降低30%

聚四氟乙烯(PTFE):介电常数ε=2.1,损耗角正切tanδ<0.0002,适用于高频信号隔离

(1).树脂筛选标准:

流动性:旋转黏度(Brookfield,25℃)需控制在 2000-5000cps,确保点胶精度(最小胶点直径<100μm)

纯度:氯离子含量<50ppm,避免腐蚀芯片电极

固化特性:凝胶时间与开放时间需匹配贴装节拍,如在线式生产要求开放时间>2小时

(2).固化剂体系对比

胺类固化剂:脂肪胺(如二乙烯三胺)固化速度快(120℃/10min),但放热峰高易导致应力集中

酸酐类固化剂:六氢苯酐体系Tg可达180摄氏度,适用于高可靠性封装,但需添加促进剂(如苄基二甲胺)

咪唑类潜伏性固化剂:2-乙基-4-甲基咪唑在 25℃下储存 6 个月活性保留率>90%,中温(100-120℃)30分钟即可完全固化

(3).工艺实施要点与应用场景

存储与使用规范:市售10-25g注射器包装需要-40℃冷冻存储,解冻遵循"缓升原则"(25℃环境静置4小时),避免冷凝水混入

开封后建议在24小时内使用完毕,剩余胶液需氮气保护密封

(4).银粉特性与导电胶性能关联性

银粉选型需重点考量粒子形态与粒径参数,二者直接影响导电胶的电- 热传输性能。依据渗流理论,粒子形态选择遵循 “最大化接触面积” 原则,常见形态包括球状、鳞片状、枝状及杆状四类,其接触效能排序为:枝状>鳞片状≈杆状>球状。其中,鳞片状与枝状银粉因展平效应常归为片状体系。

按粒径分类,银粉可划分为微晶级(<0.1μm),微球级(0.1-2μm)及片状级(>2μm)。片状银粉进一步细分 2-4μm、5-8μm、8-10μm 及>10μm 多档规格。粒径与导电性呈负相关:大粒径银粉(如>10μm)因单位体积内导电通路稀疏,导致电阻率上升;而小粒径片状银粉(2-4μm)因高比表面积,更易形成致密导电网络。

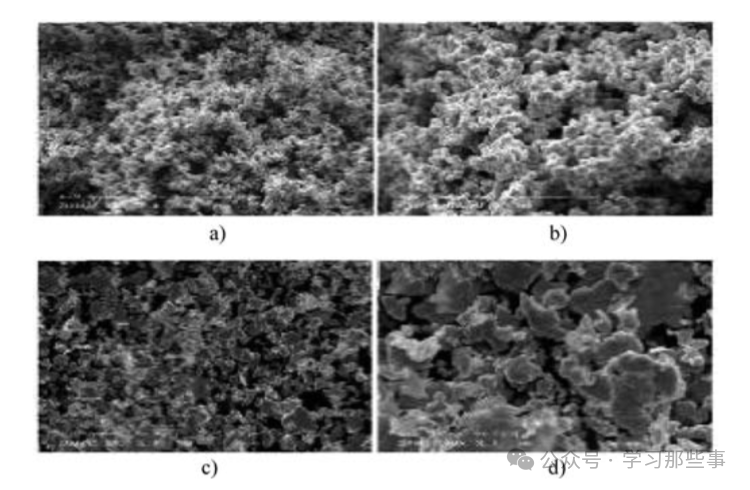

银粉形状电镜图

如上图所示,图a、b 中的球状银粉呈类球形絮状堆积,因表面电荷作用形成团聚体,实测比表面积达3-5m?/g,但颗粒间点接触占比超70%;图c、d 的片状银粉呈现不规则延展结构,典型尺寸为4-6μm,其层叠搭接形成的面接触比例提升至85%以上,更符合导电通路构建需求。

5.填充量对性能的量化影响

银粉体积分数与导电性能呈非线性关系:60%填充量时,体积电阻率>2.5×10??Ω?cm,未形成连续导电网络;75%填充量时,电阻率骤降至 1×10??Ω?cm;80%填充量时,电阻率达 2×10??Ω?cm,进入 10??Ω?cm 数量级。同步测试显示,填充量>75%后,拉伸剪切强度突破 20MPa,但流动性下降显著。

6.应用技术瓶颈与解决方案

电导率局限:常规导电胶电阻率(10??-10??Ω?cm)难以满足功率器件(需<5×10??Ω?cm)的低阻散热需求

适配性差异:黏接强度受基板材质(FR-4、陶瓷)与芯片表面处理工艺显著影响,如陶瓷基板的黏附力仅为FR-4基板的60%

固化效率问题:环氧树脂体系常规固化需 120℃/30min。为了解决这一问题,国内外的科研工作者做了以下的努力:增加树脂网络的固化收缩率,用短的二羧酸链去除金属填充物表面的润滑剂,用醛类去除金属填充物表面的金属氧化物,采用纳米级的填充粒子等

黏结强度低:细间距(<50μm)封装中,黏接层需承受>50MPa 冲击应力,目前通过纳米银(粒径<50nm)掺杂可提升模量30%

考虑到黏结成型主要依赖环氧树脂的交联反应实现,有必要先对环氧树脂的基础概念做简要梳理。环氧树脂的核心结构单元是环氧环——由两个碳原子与一个氧原子构成的三元环状结构。凡分子中包含此类环氧环的化合物,均归类为环氧化合物(Epoxide)。

环氧树脂

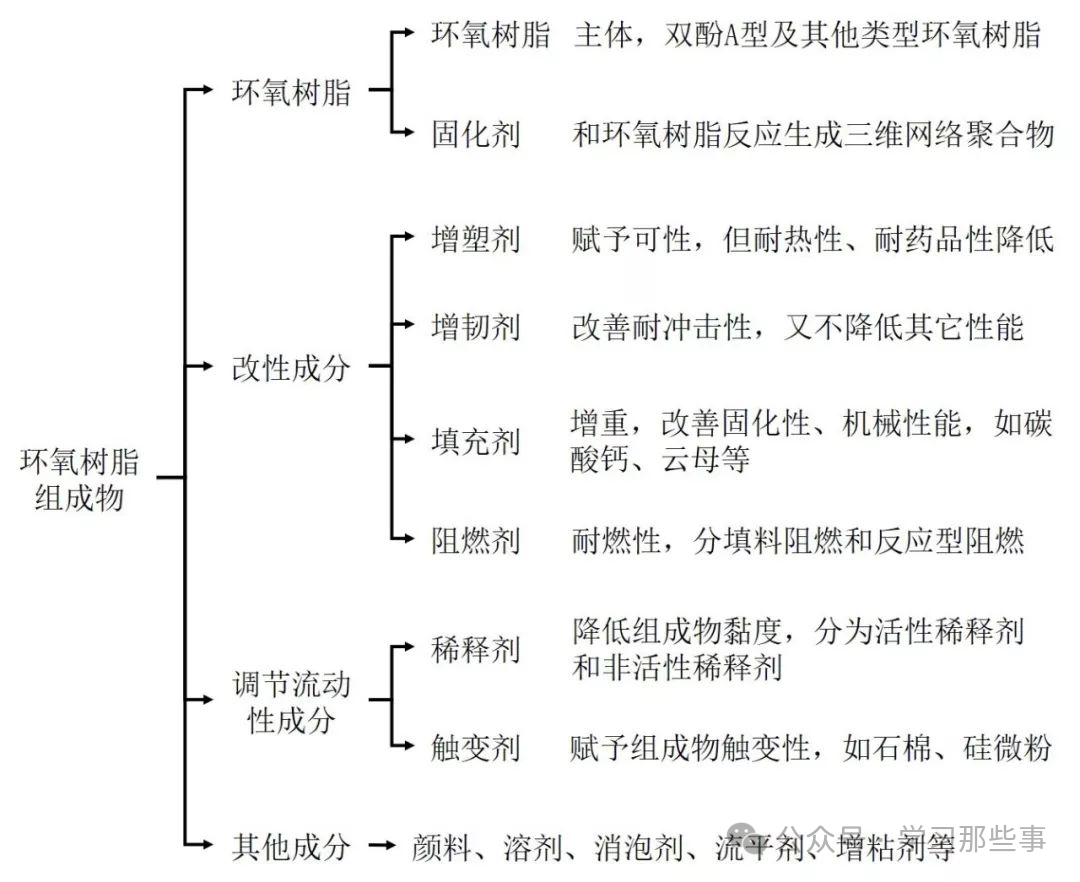

环氧树脂以分子链含≥2个环氧基团为特征,经固化剂引发开环聚合形成三维网状结构。作为热固性高分子材料,其产品涵盖低聚物预聚体与小分子单体,广泛应用于水利工程、电子封装等七大领域。环氧树脂组成如图:

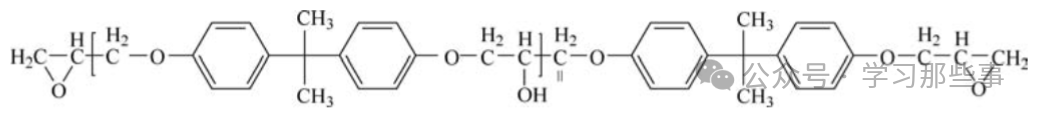

双酚A环氧树脂凭借成本与性能平衡优势占据65%市场份额。其氢化改性产物(如氢化双酚A环氧树脂)因消除苯环结构,耐候性提升3倍(QUV老化测试1000h黄变指数<5),尤其适用于户外封装场景。未固化环氧树脂呈液态或半固态(黏度范围500-5000cps),需与胺类/酸酐类固化剂按化学计量比混合。以咪唑类潜伏性固化剂为例,80℃活化后与环氧基团发生亲核加成反应,经2-3小时形成玻璃化转变温度(Tg)达150℃的交联网络。双酚A环氧树脂结构图:

环氧树脂基导电胶技术演进:通过引入石墨烯纳米片(横向尺寸1-5μm,层数<10)构建“银-石墨烯”协同导电网络,可使填料总含量降低15%,同时实现电导率提升40%(从1×10?? Ω·cm至1.4×10??Ω·cm)。实验数据显示,当石墨烯质量分数为0.5%时,导热系数从1.2W/mK增至1.8W/mK。针对功率器件(工作温度>125℃)与IC封装(线宽<50μm)的差异化需求,需定制化设计胶黏剂。功率模块需满足热阻<0.5℃/W、剪切强度>30MPa,适配高银填充量(≥85%)+硅微粉导热填料;IC封装要求绝缘电阻>10?? Ω、低应力模量,依赖纳米级填料分散与柔性增韧剂配合。

胶联装片工艺体系

标准工艺流程包括基板预处理,通过等离子清洗将接触角从65°降至20°以去除氧化物;采用非接触喷射技术实现胶点体积±5%精度的精密点胶;利用真空吸嘴达成±10μm定位精度的芯片贴装,最后经阶梯升温曲线(60℃/30min→120℃/60min)完成固化。行业实践表明,优化后装片良率可从92%提升至98.5%,热阻降低28%。

-

半导体

+关注

关注

335文章

29039浏览量

240317 -

封装

+关注

关注

128文章

8743浏览量

145750 -

工艺

+关注

关注

4文章

690浏览量

29535

原文标题:芯片粘片介绍

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体封装中的装片工艺介绍

半导体封装中的装片工艺介绍

评论