概述

MAX9321B是一种低扭曲、差分接收器/驱动器,设计用于时钟和数据分配。差分输入经过调整后,可以允许单端输入,只需将片上VBB电源接到一个输入端作为参考电压即可。

MAX9321B具有超低传输延迟(172ps)、20ps的器件至器件扭曲以及最大24mA的电源电流等特性,使其尤其适合于时钟缓冲或中继。为与差分PECL和LVPECL信号接口,该器件工作于+3.0V至+5.5V的电源电压,能够实现在3.3V或5.0V标称电压系统中,进行高性能的时钟或数据分配。而对于差分ECL和LVECL工作方式,该器件工作于-3.0V至-5.5V的电源电压。

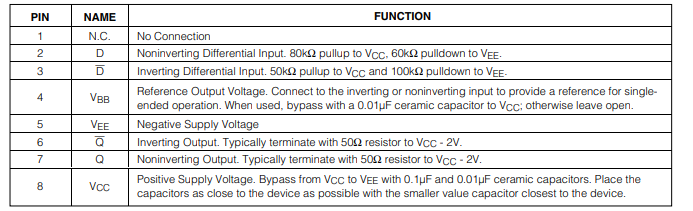

MAX9321B提供工业标准的8引脚SO和TSSOP封装。

数据表:*附件:MAX9321B差分PECL ECL LVPECL LVECL接收器 驱动器技术手册.pdf

应用

- 低抖动数据中继器

- 精密时钟缓冲器

特性

- 改进的MC10EP16D代用产品

- +3.0V至+5.5V差分PECL/LVPECL工作方式

- -3.0V至-5.5V差分ECL/LVECL工作方式

- 17mA的低电源电流

- 20ps的器件至器件扭曲

- 172ps的传输延迟

- 3GHz时最小输出300mV

- 输入开路时,输出为低电平

2kV的ESD保护(人体模型)

- 用于单端输入的片上基准电压

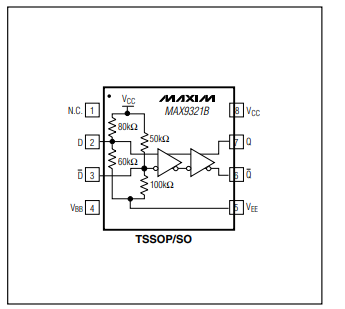

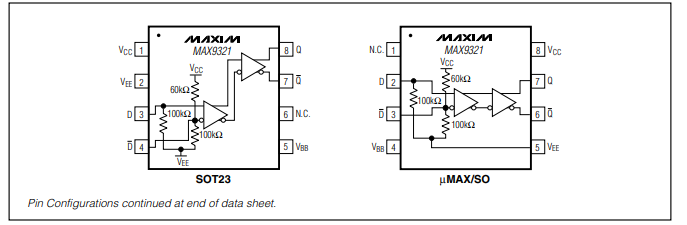

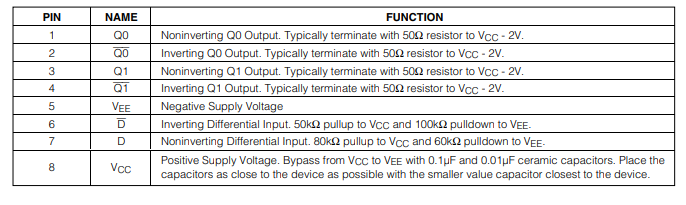

引脚图

详细说明

MAX9321B低偏斜差分接收器/驱动器专为差分时钟和数据分配而设计,适用于PECL/LVPECL信号接口。该器件在+3.0V至+5.5V电源范围内工作,可实现高性能时钟和数据分配,系统电源标称值为3.3V或5V。对于差分ECL/LVECL工作模式,该器件采用-3.0V至-5.5V电源供电。

输入

差分输入可配置为接受单端输入。这是通过连接片内参考电压VBB来实现的,以此作为参考。例如,将差分输入转换为非反相单端输入时,需将VBB连接到D?,并将单端输入连接到D。而将其转换为反相单端输入时,则需将VBB连接到D,并将单端输入连接到D? 。

使用VBB参考输出时,需用一个0.01μF陶瓷电容将其旁路到VCC。如果不使用VBB参考,也可使用其他源,如0.5mA电流源。但同一器件上的输入只能使用VBB作为参考。

差分输入从D到D? 的最大电压为3.0V。此限制也适用于差分输入与单端输入之间的电压差。

差分输入具有偏置电阻,当输入开路时,会将输出驱动为差分低电平。反相输入端由50kΩ上拉至VCC和100kΩ下拉至VEE的电阻进行偏置。非反相输入端由60kΩ上拉至VCC和60kΩ下拉至VEE的电阻进行偏置。

差分输入的高低电压(VIH_D和VIL_D )以及差分输入电压(VIH_D - VIL_D )的规格需同时满足(VIL_D不能高于VIH_D )。

输出

输出电平参考VCC和VEE ,具体取决于PECL/LVPECL或ECL/VECL的电平。使用VCC连接到正电源、VEE连接到GND的PECL/LVPECL时,输出为ECL/VECL;当VCC连接到GND、VEE连接到负电源时,输出为ECL/VECL。

至少为VBB ±100mV的单端输入,或至少为±100mV的差分输入,会在“电气特性”表中规定的电压电平下切换输出。

应用信息

电源旁路 :用表面贴装的0.1μF和0.01μF高频陶瓷电容将VCC旁路到VEE,尽可能靠近器件放置,0.1μF电容靠近器件,使用多个接地过孔实现低电感。使用VBB参考输出时,用0.01μF陶瓷电容将其旁路到VCC(如果不使用VBB参考,该电容可省略)。

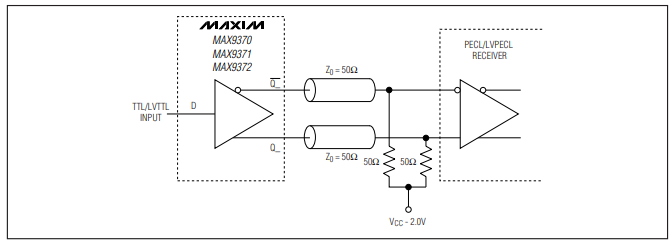

走线 :输入和输出走线特性会影响MAX9321B的性能。将差分输入或输出的每条信号走线的特性阻抗匹配为50Ω。尽量减少过孔数量,以防止阻抗不连续。通过保持550Ω特性阻抗来减少反射,这可通过连接器和走线实现。

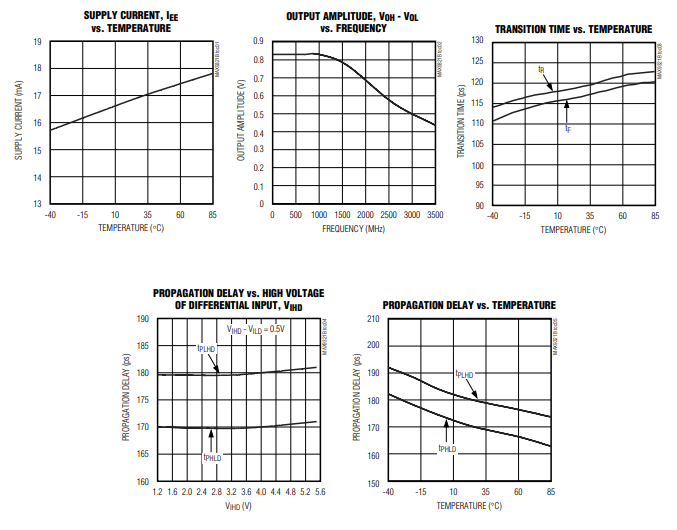

典型操作特性

-

时钟

+关注

关注

11文章

1903浏览量

133365 -

差分接收器

+关注

关注

1文章

12浏览量

8856 -

差分驱动器

+关注

关注

0文章

65浏览量

15572

发布评论请先 登录

ecl差分接入的0.8v摆幅是否可以驱动ad10242,lvpecl电平是否可以满足标准?

MAX9312, MAX9314 双路、1:5差分LVPEC

双差分驱动器和接收器 SN7534050 SN7534051 数据表

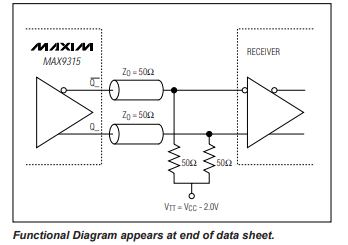

MAX9315 1:5差分LVPECL/LVECL/HSTL时钟和数据驱动器技术手册

MAX9321B差分PECL/ECL/LVPECL/LVECL接收器/驱动器技术手册

MAX9321B差分PECL/ECL/LVPECL/LVECL接收器/驱动器技术手册

评论