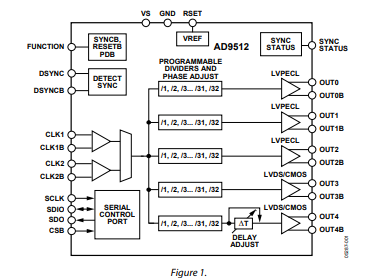

概述

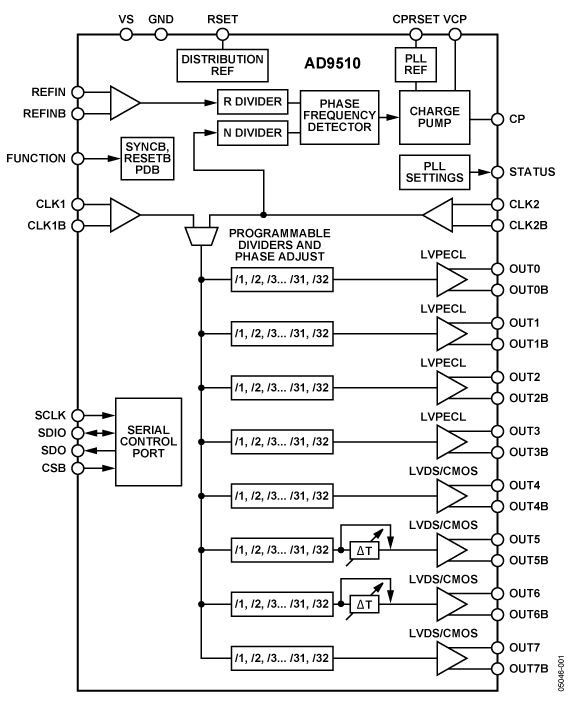

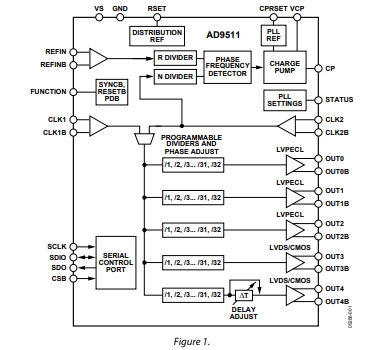

AD9510提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。4路独立的LVPECL时钟输出和4路LVDS时钟输出工作频率分别为1.2 GHz和800 MHz。可选的CMOS时钟输出工作频率为250 MHz。

数据表:*附件:AD9510 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出技术手册.pdf

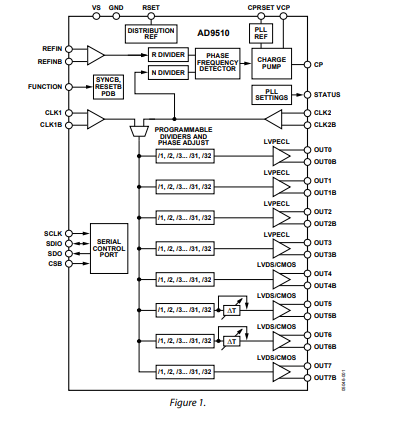

PLL部分由可编程参考分频器(R)、低噪声鉴频鉴相器(PFD)、精密电荷泵(CP)和可编程反馈分频器(N)组成。将外部VCXO或VCO连接到CLK2和CLK2B引脚时,最高达1.6 GHz的PLL输出频率可以与输入参考REFIN同步。

时钟分配部分提供LVPECL输出和可编程为LVDS或CMOS的输出。每路输出都有一个可编程分频器,可以旁路该分频器或者设置最高32的整数分频比。

用户可以通过各分频器改变一路时钟输出相对于其它时钟输出的相位,这种相位选择功能可用于时序粗调。某些输出还提供可编程延迟特性,具有最长10 ns的用户可选满量程延迟值。该精调延迟模块通过一个5位字进行编程,提供32个可用的延迟时间供用户选择。

AD9510非常适合数据转换器时钟应用,利用亚皮秒抖动编码信号,可实现优质的转换器性能。

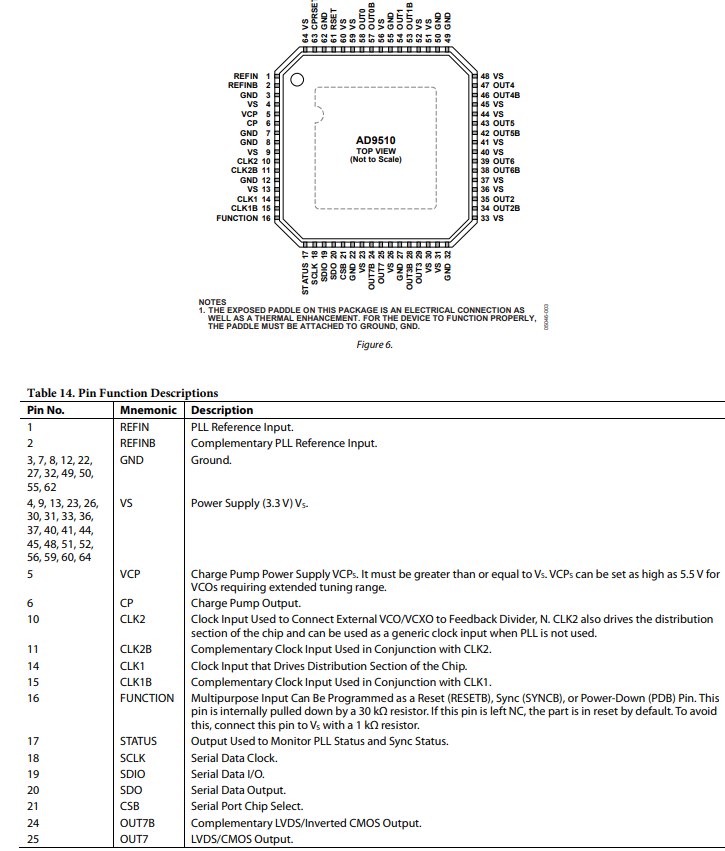

AD9510提供64引脚LFCSP封装,额定温度范围为-40°C至+85°C,可以采用3.3 V单电源供电。如果用户希望扩展外部VCO的电压范围,可以利用最高达5.5V的电荷泵电源VCP。

应用

特性

- 低相位噪声锁相环内核

- 最高250 MHz的基准输入频率

- 可编程双模预分频器

- 可编程电荷泵(CP)电流

- 独立的CP电源(VCPS)可扩展调整范围

- 两路1.6 GHz差分时钟输入

- 8个可编程分频器,1至32整数分频比

- 用于输出到输出延迟粗调的相位选择

- 4路独立的1.2 GHz LVPECL输出

- 加性输出抖动:225 fs rms

- 4路独立的800 MHz低压差模信号

- (LVDS)或250 MHz互补金属氧化物半导体

- (CMOS)时钟输出

- 加性输出抖动:275 fs rms

- 2路LVDS/CMOS输出提供精密延迟调整功能

- 串行控制端口

- 节省空间的64引脚LFCSP封装

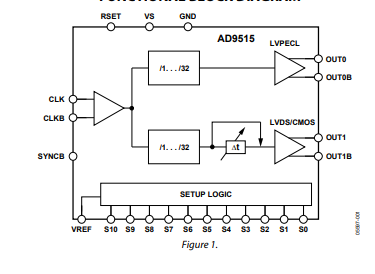

框图

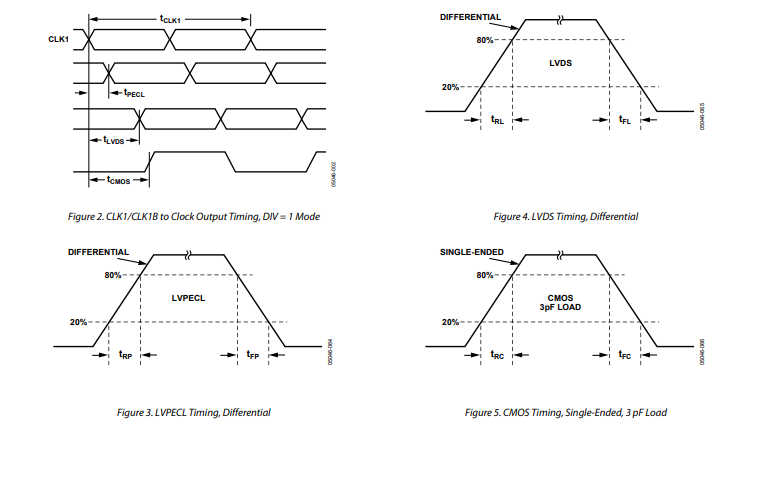

时序图

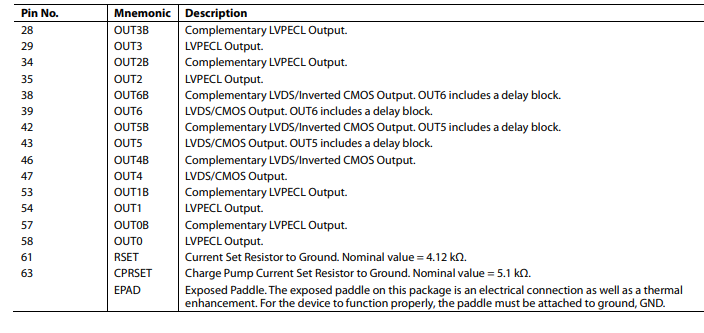

引脚配置描述

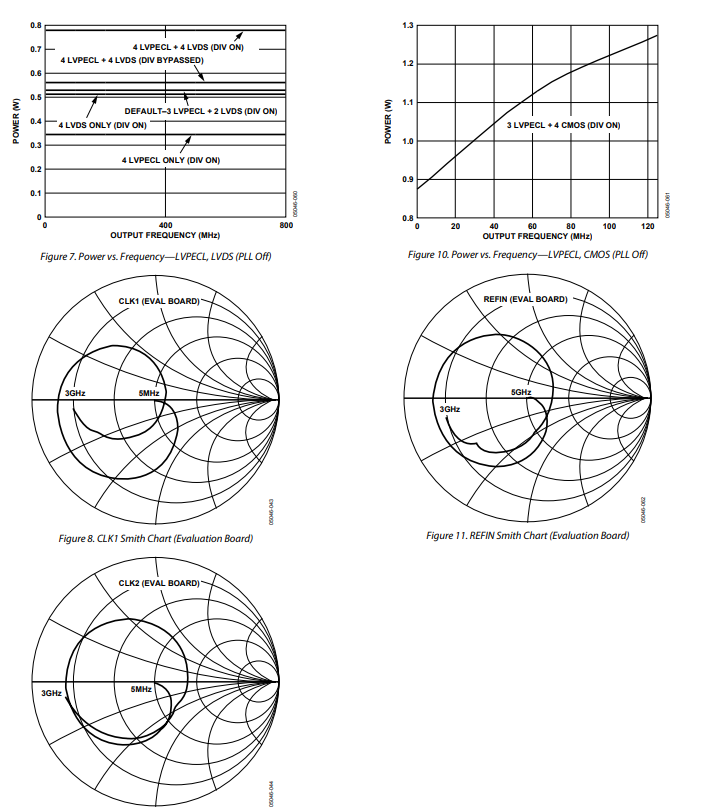

典型性能特征

术语

相位抖动与相位噪声

理想正弦波的相位在每个周期内会从 0 度到 360 度连续且均匀地变化。然而,实际信号的相位会随时间偏离理想的相位变化,这种随时间的相位变化偏差量被称为相位抖动。虽然导致相位抖动的原因有很多,但一个主要因素是随机噪声,其在统计上呈高斯(正态)分布。

这种相位抖动会使正弦波在频域中的能量扩散,产生连续的功率谱。该功率谱通常以相对于正弦波(载波)在给定频率偏移下的 dBc/Hz 为单位进行表示,其数值是在 1Hz 带宽内与载波功率的比值(以 dB 为单位)。每次测量时,载波频率的偏移量也会给出。

对特定频率区间(例如 10kHz 到 10MHz)内的总功率进行积分也具有意义,这被称为该频率偏移区间上的积分相位噪声,它与该偏移区间内相位噪声导致的时间抖动密切相关。

相位噪声对模数转换器(ADC)、数模转换器(DAC)和射频(RF)混频器有确定性影响,会降低这些转换器和混频器可实现的动态范围,不过影响方式有所不同。

时间抖动

相位噪声是频域现象,而在时域中,同样的效应表现为时间抖动。观察正弦波时,会发现其过零点的时间发生变化。对于方波,时间抖动表现为信号电平跳变沿相对于理想(规则)跳变时刻的位移。在这两种情况下,与理想时间的偏差就是时间抖动。由于这些变化具有随机性质,时间抖动通常以秒的均方根(rms)值或高斯分布的 1 个标准差来表示。

数模转换器(DAC)或模数转换器(ADC)采样时钟的时间抖动会降低转换器的信噪比(SNR)和动态范围。抖动尽可能低的采样时钟能使给定转换器发挥出最高性能。

附加相位噪声

附加相位噪声是指可归因于被测设备或子系统的相位噪声量。测量时,必须减去任何外部振荡器或时钟源的相位噪声,这样就能预测该设备对总系统相位噪声的影响程度。当与各种自身也会产生相位噪声的振荡器和时钟源配合使用时,在很多情况下,某个元件的相位噪声会主导系统相位噪声。

附加时间抖动

附加时间抖动是指可归因于被测设备或子系统的时间抖动量。测量时,必须减去任何外部振荡器或时钟源的时间抖动,这样就能预测该设备对总系统时间抖动的影响程度。当与各种自身也会产生时间抖动的振荡器和时钟源配合使用时,在很多情况下,外部振荡器和时钟源的时间抖动会主导系统时间抖动。

-

pll

+关注

关注

6文章

891浏览量

136546 -

时钟

+关注

关注

11文章

1903浏览量

133362 -

数据转换器

+关注

关注

1文章

375浏览量

29171

发布评论请先 登录

请问AD9510时钟怎么配置

AD9510关于PLL锁定频率的寄存器配置?

1.2千兆赫时钟分配IC锁相环核心分频器延迟调整八输出AD9510数据表

AD9510 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出

AD9512:1.2 GHz时钟分配IC,1.6 GHz输入,分频器,延迟调整,五输出数据表

AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

AD9511 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,5路输出技术手册

AD9512 1.2 GHz时钟分配IC、2路1.6 GHz输入、分频器、延迟调整、5路输出技术手册

AD9510 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出技术手册

AD9510 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出技术手册

评论