概述

AD9540支持多种功能,包括信号合成和低抖动时钟发生,适合各种应用。该器件内置高性能PLL电路,包括灵活的200 MHz鉴频鉴相器和数字控制电荷泵电流。它还可以使低抖动、655 MHz CML模式(PECL兼容)输出驱动器具有可编程压摆率。器件支持最高2.7 GHz的外部VCO速率。片上400 MSPS DDS提供及精密的调谐分辨率和相位编程能力。信息通过一个串行I/O端口载入AD9540中,该端口的器件写入速度为25Mb/s。还可以对AD9540分频器模块进行编程,支持扩频时钟模式。

AD9540的额定工作温度范围为-40℃至+85℃扩展汽车应用温度范围。

数据表:*附件:AD9540低抖动、基于DDS的时钟发生器和频率合成器技术手册.pdf

应用

特性

- 出色的内在抖动性能

- 200 MHz鉴频鉴相器输入

- 655 MHz可编程输入分频器用于鉴频鉴相器(÷M,N) {M,N =1..16}(可旁路)

- 可编程RF分频器(÷R) {R = 1、2、4、8}(可旁路)

- 8个可编程相位/频率配置文件

- 400 MSPS内部DDS时钟速度

- 48位频率调谐字分辨率

- 14位可编程相位偏移

- 器件采用1.8 V电源供电

- I/O、CML驱动器和电荷泵输出采用3.3 V电源供电

- 软件控制关断功能

- 48引脚LFCSP封装

- 可编程电荷泵电流(最高达4 mA)

- 检测到双模式PLL锁定

- 符合PECL标准的655 MHz CML模式输出驱动器

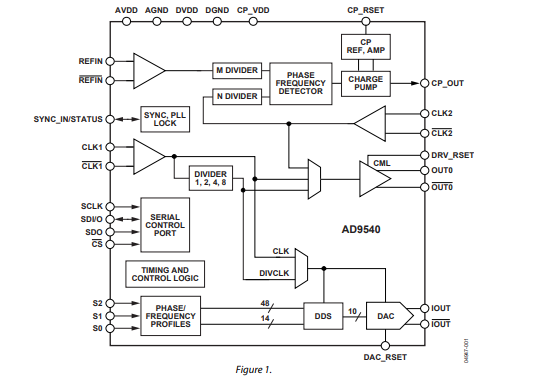

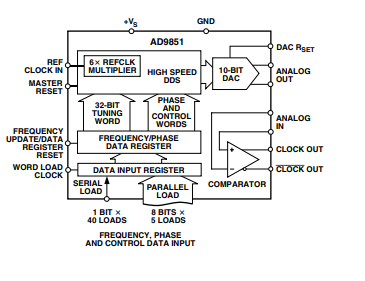

框图

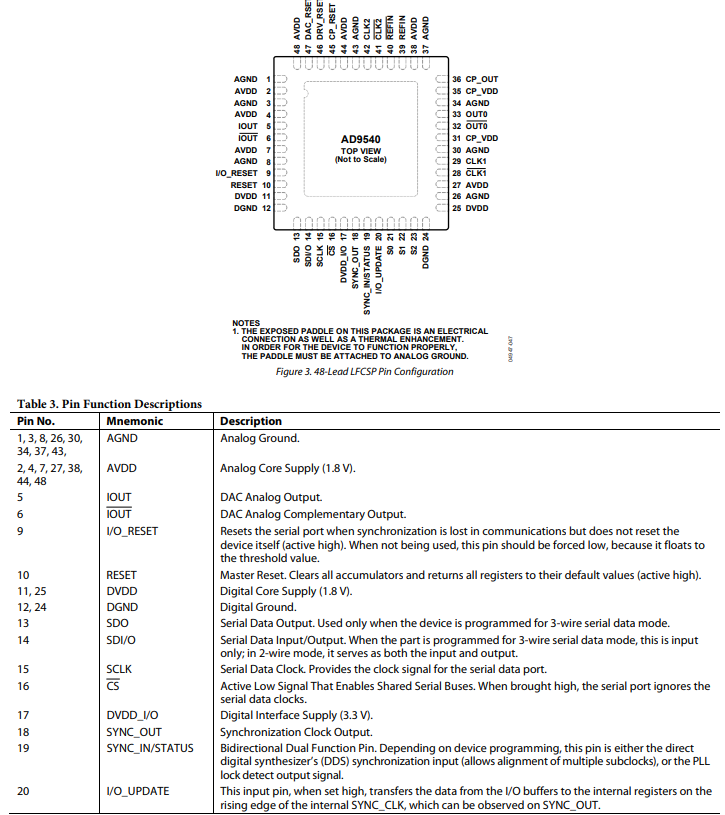

引脚配置描述

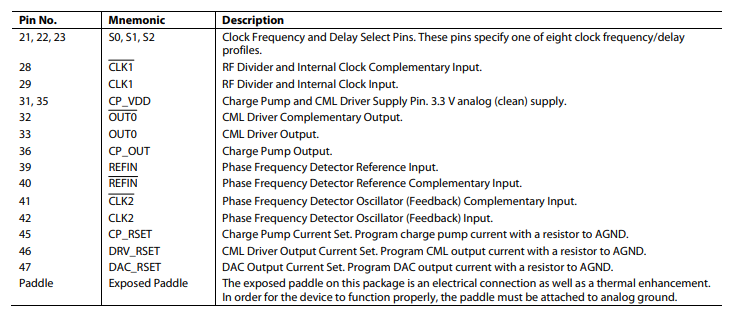

典型性能特征

应用电路说明

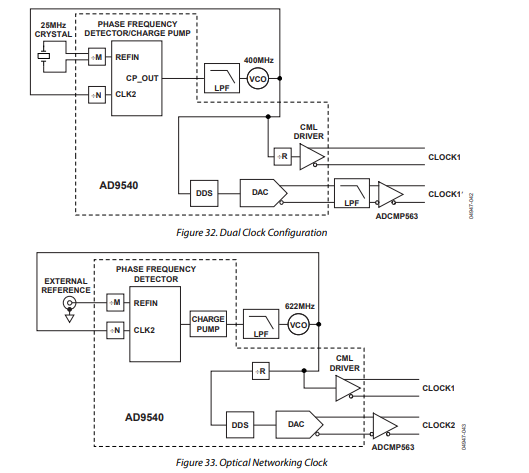

双时钟配置

在此电路中,M = 1,N = 16,R = 4。直接数字合成器(DDS)的调谐字也为1/4,这样CLOCK1'的频率就等于CLOCK1的频率。DDS中的相位调整功能为CLOCK1'相对于CLOCK1提供14位可编程上升沿延迟能力(见图32)。

光网络时钟

这是将AD9540配置为光网络时钟的情况。该环路可用于为OC12生成622 MHz时钟。DDS可编程输出8 kHz信号,作为子系统中其他电路的基准(见图33)。

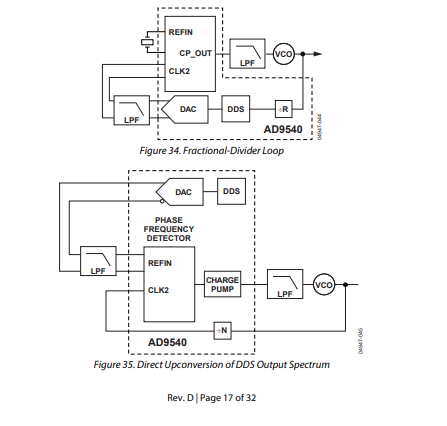

分数分频器环路

该环路在反馈路径中提供DDS的精确(48位)分数频率除法功能以及DDS的频率扫描功能。对DDS进行编程,可实现从24 MHz到25 MHz的扫描,压控振荡器(VCO)的输出从2.7 GHz扫描到2.6 GHz。此情况下的参考源是一个简单的晶体(见图34)。

直接上变频

AD9540被配置为使用DDS作为锁相环(PLL)的精确参考源。由于VCO频率小于655 MHz,它可以直接输入到鉴频鉴相器的反馈端。

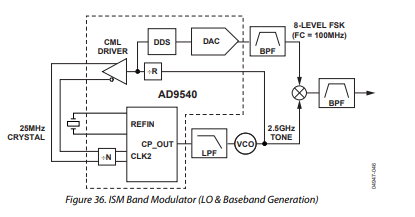

本振和基带调制生成

利用AD9540的PLL部分生成本振(LO),DDS部分生成调制后的基带,此电路使用外部混频器在射频工业、科学和医学(ISM)频段实现一些简单的调制(见图36)。

-

频率合成器

+关注

关注

5文章

297浏览量

32889 -

pll

+关注

关注

6文章

891浏览量

136566 -

时钟发生器

+关注

关注

1文章

227浏览量

69247 -

AD9540

+关注

关注

0文章

3浏览量

8424

发布评论请先 登录

AD9914BCPZ直接数字频率合成器

基于DDS的频率合成器设计介绍

什么是频率合成器

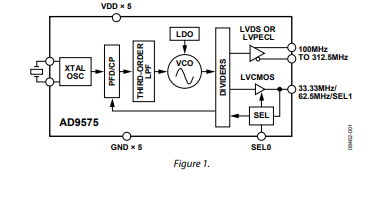

时钟发生器AD9577资料分享

DDS频率合成器和信号发生器是同一个概念吧?

AD9850 DDS 频率合成器的原理及应用

AD9540 低抖动、基于DDS的时钟发生器和频率合成器

AD9540低抖动、基于DDS的时钟发生器和频率合成器技术手册

AD9540低抖动、基于DDS的时钟发生器和频率合成器技术手册

评论