概述

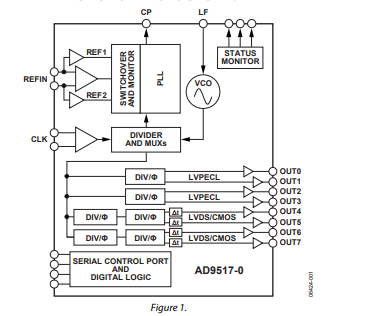

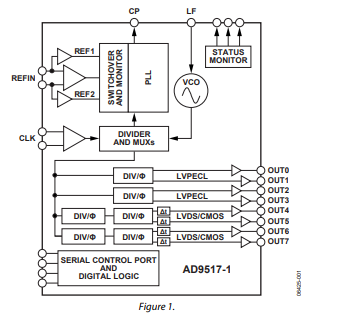

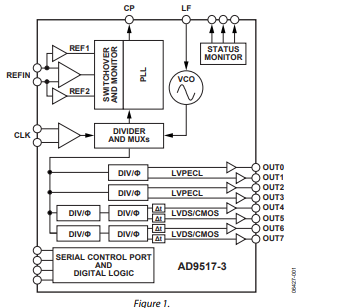

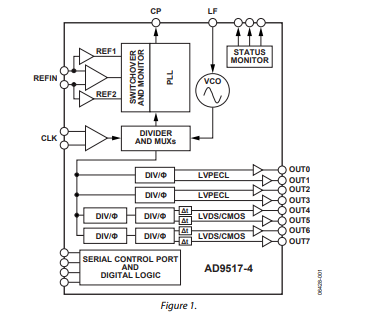

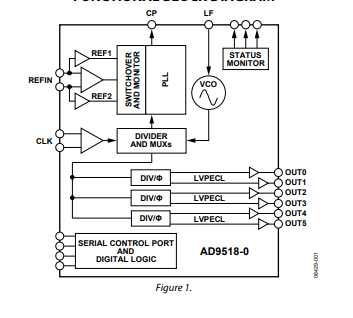

AD9517-0^1^提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成PLL和VCO。片内VCO的调谐频率范围为2.55 GHz至2.95 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

数据表:*附件:AD9517-0 12路输出时钟发生器,集成2.8GHz VCO技术手册.pdf

AD9517-0具有出色的低抖动和相位噪声特性,可极大地提升数据转换器的性能,并且也有利于其他相位噪声和抖动要求严苛的应用。

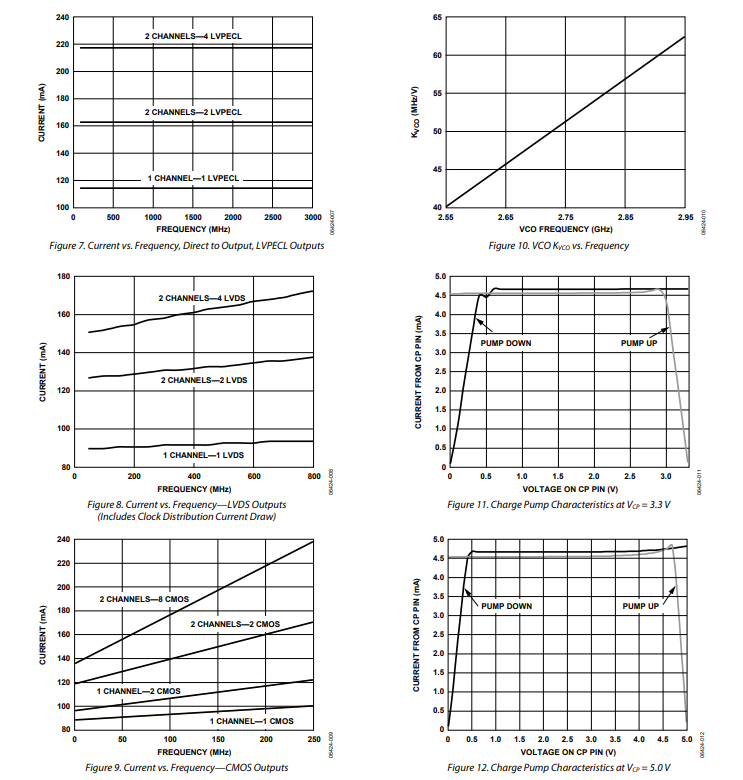

AD9517-0具有四路LVPECL输出(分为两对)和四路LVDS输出(分为两对)。可以将每路LVDS输出重新配置为两路CMOS输出。LVPECL输出的工作频率达1.6 GHz,LVDS输出的工作频率达800 MHz,CMOS输出的工作频率达250 MHz。

对于需要额外输出的应用,可使用AD9520和AD9522,二者具有晶振基准电压输入、零延迟或用于启动时自动配置的EEPROM。此外,AD9516和AD9518特性与AD9517相似,但输出组合不同。

每对输出均有分频器,其分频比和粗调延迟(或相位)均可以设置。LVPECL输出的分频范围为1至32。LVDS/CMOS输出的分频范围最高可达1024。

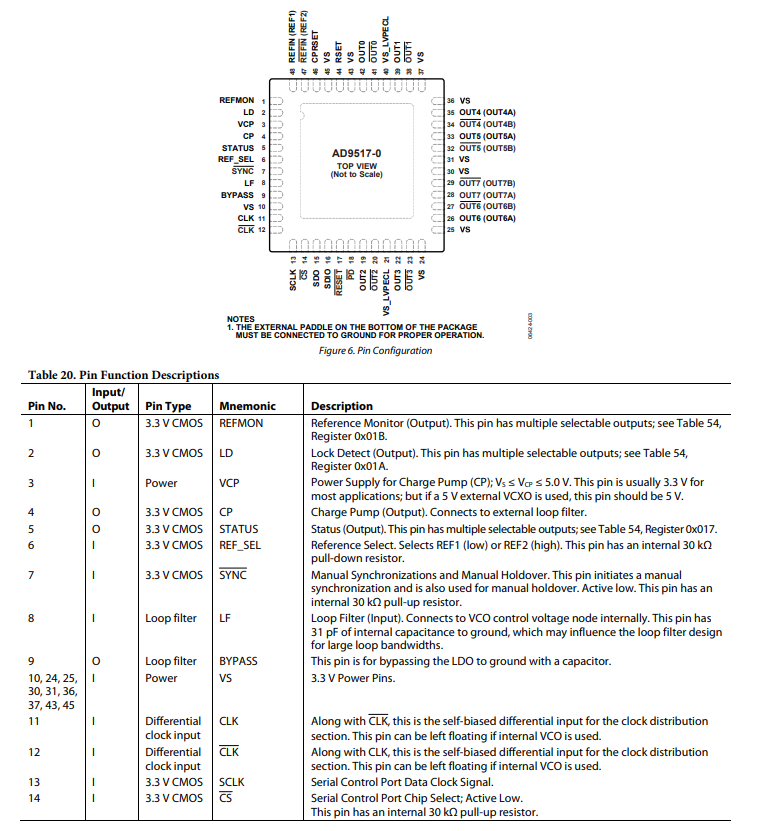

AD9517-0提供48引脚LFCSP封装,可以采用3.3 V单电源供电。将电荷泵电源(VCP)与5V电压相连时,可以使用外部VCO,它需要更宽的电压范围。独立的LVPECL电源可以为2.5 V至3.3 V(标称值)。

AD9517-0的额定工作温度范围为–40°C至+85°C工业温度范围。

应用

- 低抖动、低相位噪声时钟分配

- 10/40/100 Gb/s网络线路卡,包括SONET、同步以太网、OTU2/3/4

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

特性

- 低相位噪声锁相环(PLL)

片内VCO的调谐频率范围为2.55 GHz至2.95 GHz - 可选外部VCO/VCXO,最高达2.4 GHz

- 1路差分或2路单端参考输入

- 参考监控功能

- 自动恢复和手动参考

切换/保持模式 - 2对1.6 GHz LVPECL输出

每对输出共用1至32分频器和粗调相位延迟

加性输出抖动:225 fs均方根值

通道间偏斜成对输出小于10 ps - 支持最高250 MHz的LVPECL、LVDS或CMOS基准

- 可编程PFD路径延迟

- 可选数字或模拟锁定检测

- 2对800 MHz LVDS时钟输出

每对输出共用两个1至32级联分频器和粗调相位延迟

加性输出抖动:275 fs均方根值

可以精调每路LVDS输出的延迟(Δt) - 可以将每路LVDS输出重新配置为两路250MHz CMOS输出

- 上电时所有输出自动同步

- 提供手动输出同步

- 欲了解更多特性,请参考数据手册

框图

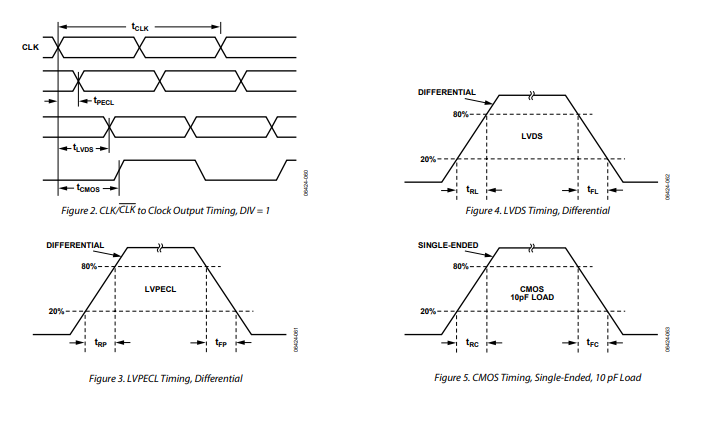

时序图

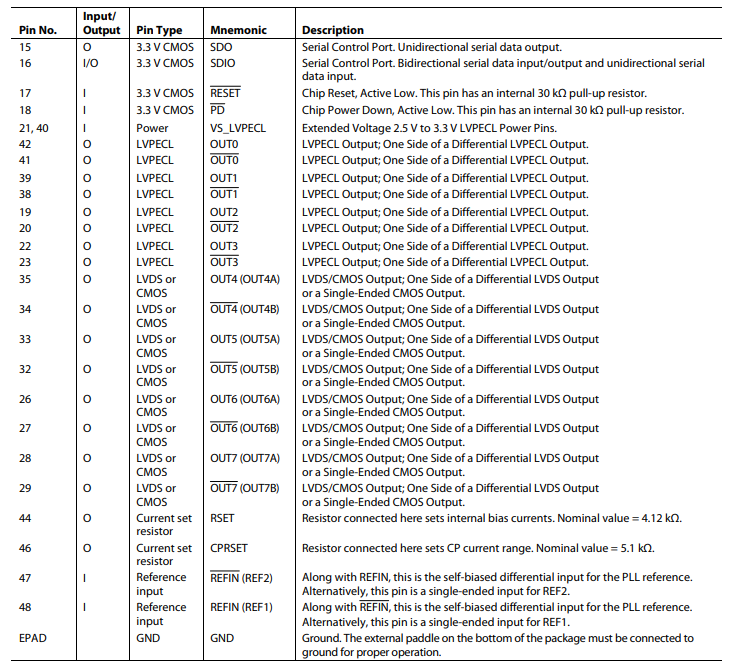

引脚配置描述

典型性能特征

数字锁检测(DLD)

通过DLD功能选择合适的输出引脚,可使能DLD功能。DLD功能可通过LD、STATUS和REMON引脚使用。DLD电路在PLL锁定时,监测每个引脚上的电压上升沿时间差。当输入频率低于指定值(锁定阈值)时,会指示锁定状态。锁定状态的超出通过超出指定值(解锁阈值)来指示。需注意,解锁阈值比锁定阈值更宽泛,这允许在不触发监测电路的情况下出现相位误差超出锁定窗口的情况。

锁检测窗口定时取决于以下三个设置:数字锁检测窗口(寄存器0x0184)、反冲延迟(通过设置位Register0x0170设置,见表2)和锁检测计数器(寄存器0x0185)。检测到锁定时,会持续产生一个与锁检测窗口时间差成比例的脉冲,直到时间差大于解锁阈值。DLD电路持续指示锁定状态,直到时间差大于解锁阈值。锁定前的PFD频率必须大于解锁阈值。锁定所需的连续PFD周期数可通过寄存器0x0185编程设置。

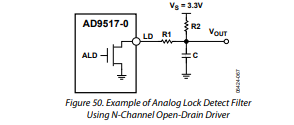

模拟锁检测(ALD)

AD9517提供一种ALD功能,可选择用于LD引脚。ALD有以下两种版本:

- N - 通道开漏锁检测 :此信号需要一个上拉电阻至正电源电压Vcc。输出正常为高电平,锁存在时输出低电平,通过最小占空比周期指示。

- P - 通道开漏锁检测 :此信号需要一个下拉电阻至GND。输出正常为低电平,锁存在时输出高电平,通过高电平占空比周期指示。

模拟锁检测功能需要一个R - C滤波器,以提供指示锁定/解锁的逻辑电平。

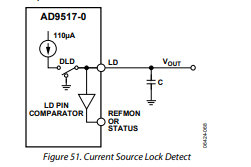

电流源数字锁检测(DLD)

在PLL锁定序列期间,DLD信号正常会在最终稳定前切换一定次数。当PLL完全锁定时,在某些应用中可能希望禁用DLD功能。可通过将PLL置于睡眠锁定状态来实现此功能,仅使用输入电流源锁检测功能

此功能在将LD引脚控制寄存器(Register 0x01A5)的输出设置为0时启用。

电流源锁检测功能在VDD为110 μA时,可防止接地电流检测。当DLD为低电平时,指示检测到接地电流。

如果在LD引脚连接一个电容器,它会以确定的速率充电,该速率在DLD为低电平时被禁用,但在DLD为高电平时几乎瞬间放电。

监测电容器的电压(即LD引脚的电压),只有在DLD拉高且锁检测未颤动时,才有可能获得逻辑高电平。

通过选择合适尺寸的电容器,可以延迟锁检测指示,直到PLL稳定锁定且锁检测不再颤动。

电容器上的电压可通过连接到LD引脚的外部比较器进行检测。不过,还有一个内部LD引脚比较器,可通过REMON引脚控制(寄存器0x0180)或STATUS引脚控制(寄存器0x0172),以实现高电平信号。它也可通过SYNCREF引脚控制(寄存器0x0181)。内部LD引脚比较器的触发点和滞后情况列于表16中。

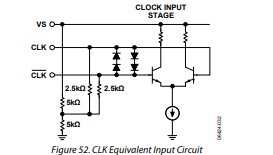

外部VCO/时钟输入(CLK/CLK)

CLK是一个差分时钟输入,可用于驱动AD9517时钟分配部分。此输入可接受高达2.4 GHz的频率。引脚内部经过直流偏置,输入信号应通过交流耦合。

CLK/CLK输入可用作仅分配功能的VCO(PLL关闭),或作为外部VCO/时钟的反馈输入,用于将外部VCO与PLL的输出频率对齐。

-

pll

+关注

关注

6文章

891浏览量

136701 -

时钟

+关注

关注

11文章

1910浏览量

133495 -

VCO

+关注

关注

13文章

311浏览量

70382 -

ad9517

+关注

关注

0文章

4浏览量

2032

发布评论请先 登录

AD9517-0 12路输出时钟发生器,集成2.8 GHz VCO

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO

AD9522-0:12集成2.8 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

AD9517-0 12路输出时钟发生器,集成2.8GHz VCO技术手册

AD9517-0 12路输出时钟发生器,集成2.8GHz VCO技术手册

评论