1.名词解释:

FPGA:现场可编程门阵列,一般工艺SRAM(易失性),所以要外挂配置芯片。

CPLD:复杂可编程逻辑器件,一般工艺Flash(不易失)。

SOC:片上系统

SOPC:片上可编程系统

2.Verilog语法类:

①Verilog两大数据类型:一类是线网类型,另一类是寄存器类型。

线网类型表示硬件电路元件之间实际存在的物理连线,有很多种:wire、tri、wor等等,当然日常使用wire最多,其他的都没遇到过。

寄存器类型表示一个抽象的数据存储单元,只能在initial或always内部被赋值,并且变量的值将从一条赋值语句保持到下一条赋值语句。有5种:reg、time(64位无符号的时间变量)、integer(32位带符号的整数型变量)、real/realtime(64位带符号的实数型变量)。reg用的最多。

②Verilog建模方式:结构化描述方式、数据流描述方式、行为描述方式、混合描述方式。

结构描述是指通过调用逻辑原件,描述它们之间的连接来建立逻辑电路的verilog HDL模型。这里的逻辑元件包括内置逻辑门、自主研发的已有模块、商业IP模块。

数据流描述是指根据信号之间的逻辑关系,采用持续赋值语句描述逻辑电路的方式。通过观察是否使用assign赋值语句可以判断是否有数据流描述。

行为描述是指只注重实现的算法,不关心具体的硬件实现细节。这与C语言编程非常类似。通过观察是否使用initial 或always语句块可以判断是否有行为描述。

混合描述是指以上几种描述方法都存在的一种描述方式。具体在一个工程中,不可能只是用单独哪一种描述方式,一般都是各种描述方式的混合。

3.VHDL相对于Verilog不能描述的层级?

网上有段话说的是:Verilog在其门级描述的底层,即晶体管开关级的描述方面比VHDL更强一些,所以即使使用VHDL的设计环境,在底层实质上也会由Verilog描述的器件库所支持。

Verilog较为适合系统级、算法级、RTL级、门级、开关级的设计,而对于特大型(千万门级以上)的系统设计,则VHDL更为适合。(VHDL比较严谨,而Verilog可以花式编码)

所以,VHDL不能描述开关级。

4.阻塞与非阻塞的区别:

对于代码:

1 //blocking; 2 begin 3 B = A; 4 C = B + 1; 5 end 6 //non-blocking; 7 begin 8 B <= A; 9 C <= B + 1; 10 end

在always语句内部过程赋值语句有两种,阻塞赋值语句与非阻塞赋值语句。

两者主要区别是完成赋值操作的时间不同,阻塞赋值语句的赋值操作是立即执行的,即执行后一句的时候,前一句的赋值已经完成;而非阻塞赋值语句的赋值操作到结束顺序语句块时才完成赋值操作,即赋值操作完成后,语句块的执行也就结束了。即阻塞是串行执行,非阻塞是并行执行的。对于上述代码,阻塞赋值中相当于C = A + 1;非阻塞赋值中B先前的值被A替代,但C的值是B先前值加1。

5.亚稳态是什么怎么解决亚稳态?

触发器输入端口的数据在时间窗口内发生变化,会导致时序违例。触发器的输出在一段时间内徘徊在一个中间电平,既不是0也不是1。这段时间称为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。

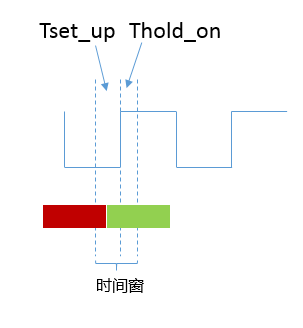

触发器由于物理工艺原因,数据并不是理想化的只要触发沿时刻不变即可。触发器有固定的建立时间,保持时间。

建立时间:在时钟有效沿到来前数据需要稳定的时间。

保持时间:在时钟有效沿之后数据还需要保持不变的时间。

后果:会给设计带来致命的功能故障。

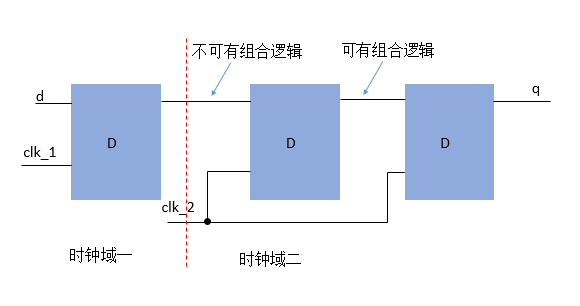

一般来说,信号是在异步信号,跨时钟域,复位电路中产生亚稳态。

解决方式:

1.单比特信号:

①采用同步器同步,低速设计打两拍,高速设计可能需要打三拍。

低速到高速时钟域,低速信号一般能被高速时钟域采到甚至多次。但高速时钟域到低速时钟域就不太好办了:

②闭环解决方案:采用握手反馈信号,这会导致延时开销大。

③开环解决方案:把信号展宽,至少为采样T的1.5倍。这样至少能采到一次。

2.多比特信号:

传递多比特信号,普通同步器就没啥卵用了,因为多比特信号偶发数据变化歪斜,导致采到的不一定是正确数据。

①多比特信号融合:把多比特信号转换为单比特信号,再用同步器同步。

②多周期路径规划:数据不需要同步,至需要同时传递一个同步的使能信号到接收时钟域即可,使能信号没被同步到接收时钟域并被识别之前数据不被采集。即在信号某个沿产生同步脉冲指示信号。

③异步fifo。

6.竞争冒险是什么,怎么解决竞争冒险?

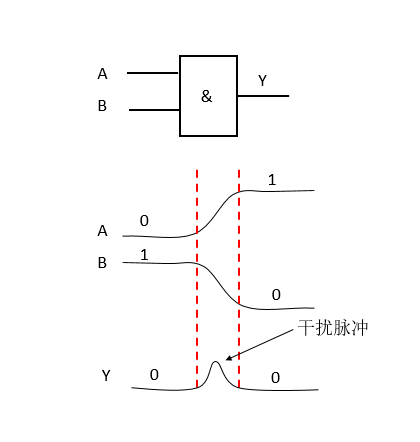

在组合电路中,当输入信号改变状态时,输出端可能出现虚假信号(过渡干扰脉冲),这对电路来说是不利的。

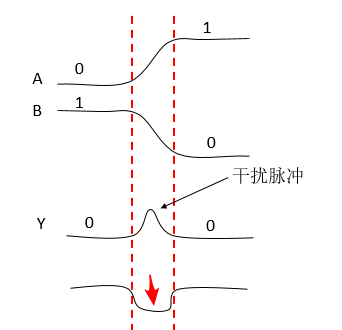

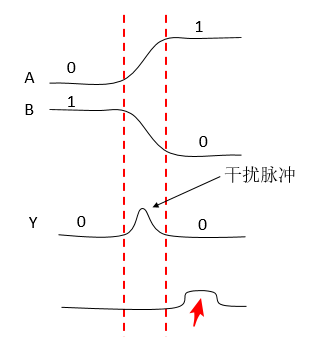

在数字电路中,任何一个门电路只要有两个输入信号同时向相反方向变化(由01变成10,或者相反),其输出端就可能产生干扰脉冲。

信号由于经由不同路径传输达到某一汇合点的时间有先有后的现象,就称之为竞争,英文名Race;由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险,英文名Hazard或者Risk。

有竞争不一定有冒险,但出现了冒险就一定存在竞争。

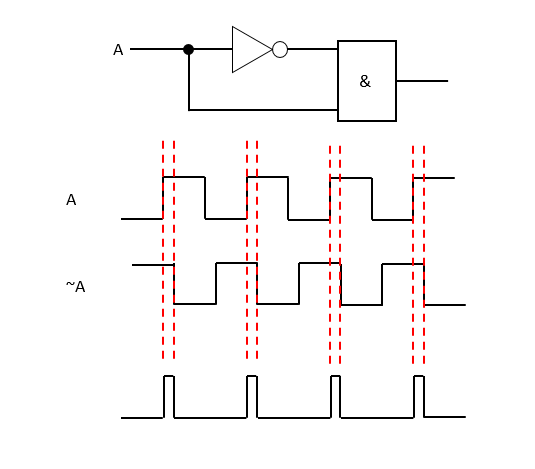

如下图的简单电路,由于门电路的延时,A非相对于A信号会滞后一丢丢(时间由工艺决定),这就会导致输出产生一个干扰脉冲。

更现实一点,对于一个与门:

解决方式:

1.引入封锁脉冲:引入负脉冲,在输入信号发生竞争的时间内,把可能产生的干扰脉冲的门锁住。

封锁脉冲的宽度不应小于过渡时间且与输出信号转换同步。

缺点:脉冲宽度和产生时间有严格要求。

2.引入选通脉冲:在电路状态稳定后,再选通输出。

缺点:脉冲宽度和产生时间有严格要求。

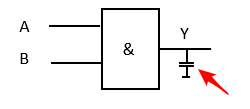

3.引入滤波电容:输出端并接一个不大的滤波电容

缺点:输出波形边沿变坏。

4.修改逻辑设计,增加冗余项:

对于给定的逻辑 Y=AB+?C,当BC都为1的时候,若A值改变,则会发生竞争。所以可以添加冗余项:

Y=AB+?C+BC

分析有无竞争冒险:画出函数的卡诺图,检查有无几何相邻的逻辑项,有则可能产生竞争冒险。

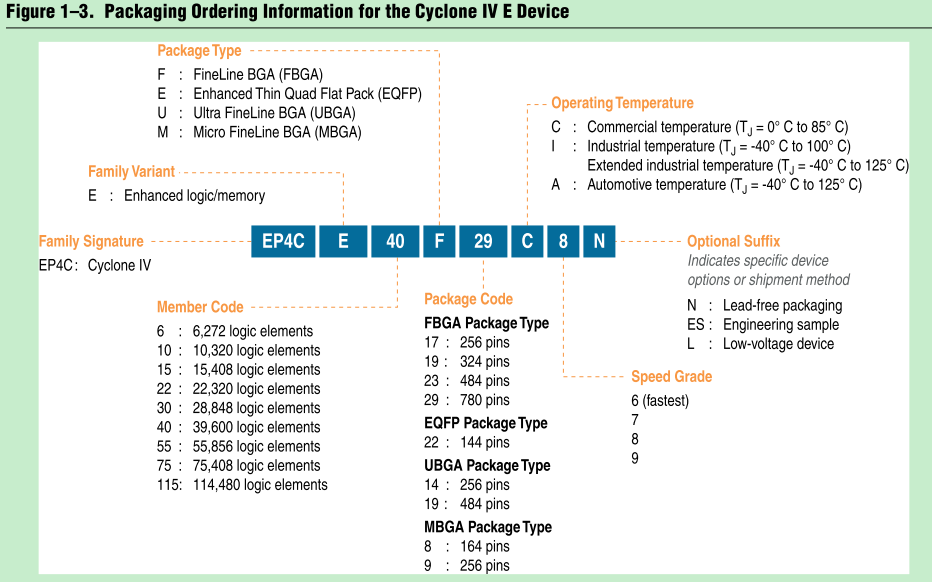

7.你使用的器件名称含义?

-

FPGA

+关注

关注

1646文章

22069浏览量

619709 -

集成电路

+关注

关注

5430文章

12139浏览量

368940 -

Verilog

+关注

关注

29文章

1367浏览量

112417 -

触发器

+关注

关注

14文章

2041浏览量

62230 -

可编程逻辑器件

+关注

关注

5文章

145浏览量

30649

原文标题:FPGA基础

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA学习笔记-入门

FPGA学习笔记-关于FPGA资源

FPGA学习笔记-电源电压

FPGA的学习笔记---FPGA的开发流程

FPGA学习笔记---基本语法

FPGA基础学习笔记--组合逻辑电路-编码器和译码器

FPGA基础学习笔记--组合逻辑电路-算术运算电路

《高级FPGA设计》学习笔记:复位方案

C.P FPGA学习笔记

FPGA学习笔记汇总(7.13更新)

INTEL FPGA学习笔记

FPGA学习笔记:ROM IP核的使用方法

FPGA学习笔记

FPGA学习笔记

评论