文章来源:学习那些事

原文作者:小陈婆婆

本文主要讲解了芯片与应用有关的失效机理。

半导体集成电路失效机理中除了与封装有关的失效机理以外,还有与应用有关的失效机理,分述如下

辐射引起的失效

与铝有关的界面效应

金与铝有关的界面效应

辐射引起的失效

在地球及外层空间环境中,辐射源分为自然(如宇宙射线)和人造(如核反应堆)两类,其对微电子器件的损伤可分为以下三类:

永久损伤:辐射源移除后,器件性能无法恢复,如晶格结构永久性破坏或深能级缺陷形成。

半永久损伤:辐射源移除后,器件性能需较长时间(如数小时至数天)才能部分恢复,通常与浅能级陷阱电荷的缓慢退火有关。

瞬时损伤:辐射源移除后,器件性能立即恢复,如单粒子瞬态(SET)引起的逻辑错误。

辐射对器件的影响主要通过三种形式实现

瞬时辐照:高能粒子(如α粒子)直接电离硅材料,产生瞬时电流脉冲,可能干扰电路逻辑状态。

单粒子辐照:单个重离子(如宇宙射线中的高能粒子)穿过器件敏感区域(如MOS管沟道),引发单粒子翻转(SEU)或单粒子闩锁(SEL)。

总剂量效应:长期累积的低剂量辐射(如γ射线或X射线)导致氧化层中陷阱电荷积累,改变MOS器件阈值电压,最终引发功能失效。

辐射损伤的物理机制

γ射线与X射线:通过光电效应和康普顿散射产生电子-空穴对。在半导体中,电子-空穴对可快速复合;但在氧化层(SiO?)中,部分空穴被深能级陷阱俘获,形成固定正电荷。同时,辐射在Si/SiO?界面引入新界面态,导致MOS器件阈值电压漂移、漏电流增加及跨导退化。

中子辐照:通过晶格碰撞产生原子移位(如硅原子离开晶格位置),形成空位-间隙对缺陷。此类缺陷显著缩短双极器件(如BJT)的载流子寿命,导致电流增益下降,但对多子导电的MOS器件影响较小。然而,MOS器件对总剂量效应和单粒子效应更为敏感,因氧化层电荷积累易导致其阈值电压偏移。

抗辐射加固设计技术

针对宇航级应用,需采用以下措施提升器件抗辐射能力:

抗单粒子设计

电路级:采用三模冗余(TMR)或错误校正码(ECC)屏蔽SEU。

器件级:优化版图布局(如增加敏感节点电容)以吸收单粒子瞬态电荷。

抗总剂量效应设计

工艺优化:采用辐射硬化氧化层(如氮氧化硅)减少陷阱电荷积累。

电路补偿:集成阈值电压监测与动态调整电路。

抗剂量率设计

材料选择:采用高纯度硅或外延层减少辐射感生缺陷。

结构设计:增加保护环或深沟槽隔离以防止寄生器件开启。

系统级加固

屏蔽设计:利用金属或陶瓷封装材料阻挡高能粒子。

冗余与容错:通过模块化设计实现故障隔离与重构。

器件敏感性差异

双极器件:对中子位移损伤敏感,但对总剂量效应耐受性较强。

MOS器件:对总剂量效应和单粒子效应敏感,但抗中子能力优于双极器件。

Bi-CMOS电路:需综合优化双极与MOS部分的抗辐射性能,例如通过隔离技术减少双极部分对MOS的干扰。

与铝有关的界面效应

铝作为微电子器件中常用的互连材料,与二氧化硅(SiO?)及硅(Si)的界面反应是器件失效的重要诱因,尤其在高温、高电流密度或辐射环境下更为显著。

铝与二氧化硅(Al-SiO?)的高温反应

在硅基器件中,SiO?常用作介质层,而铝互连线在高温下会与SiO?发生化学反应:

4Al + 3SiO? → 2Al?O? + 3Si

该反应导致铝层减薄,若SiO?层被完全消耗,铝与硅直接接触,可能引发PN结短路。在功率器件中,结温升高易形成热斑,局部加速Al-SiO?反应,进一步加剧失效风险。

预防措施

优化版图设计:改善热分布,降低热阻,增强散热能力。

复合钝化层:采用SiO?-Al-SiO?或Si?N?-SiO?多层结构,抑制铝与SiO?的直接反应。

双层金属化:使用Ti-Al、W-Al等复合金属替代纯铝,利用阻挡层金属(如Ti)阻隔铝与SiO?的接触。

铝与硅(Al-Si)的界面失效机制

铝与硅的界面反应涉及多种物理过程,可归纳为以下三类:

(1)固溶体形成与渗透坑

铝与硅的天然氧化层(SiO?)反应后,硅原子向铝中扩散并溶解,形成固溶体。

在共晶温度(577℃)下,硅在铝中的溶解度达1.59%(原子比),导致铝膜中出现渗透坑。

失效风险:渗透坑多发生于接触孔边缘(因应力集中和侧向扩散),可能穿透浅结器件的PN结,导致漏电或短路。

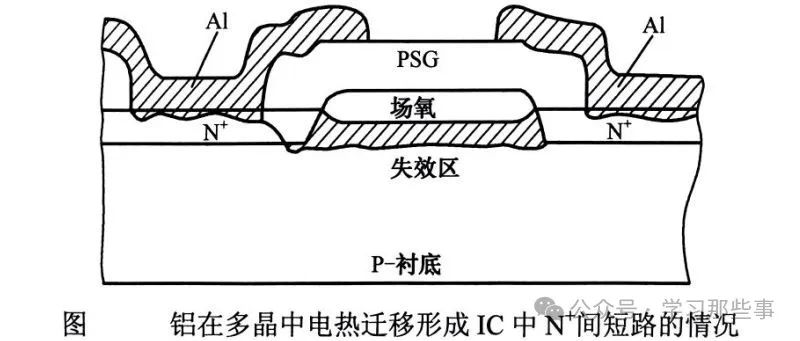

(2)硅的电迁移(Electromigration)

溶解在铝中的硅原子因浓度梯度向外扩散,电流作用下电子动能加速硅原子沿电子流方向迁移,形成质量传递与动量传递。

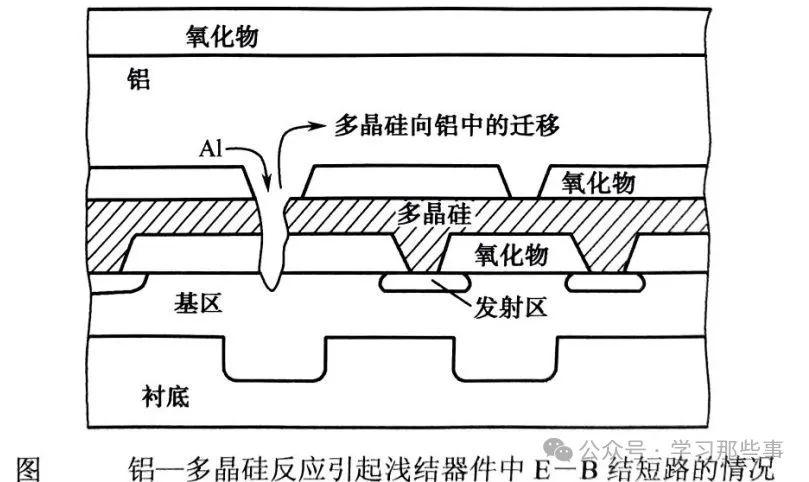

失效风险:硅迁移可导致NPN晶体管基区接触孔短路,或使浅结器件的E-B结退化。

(3)铝的热迁移(Thermomigration)

在高温、高温度梯度及高电流密度区域,铝-硅界面发生电热迁移。铝沿Si/SiO?界面或纵向渗入硅,形成合金钉(Al spike),穿透PN结。

对比其他金属:金(Au)与硅的共晶点仅377℃,其电热迁移率高于铝,需通过阻挡层(如NiCr、Mo)隔离接触。

失效模式:

双极性浅结器件:E-B结退化,反向漏电增加,击穿特性由硬击穿转为软击穿(等效电阻跨接于结两端);

NMOS集成电路:输出端无保护电路,铝在静电或过电应力下沿Si/SiO?界面形成导电通道,导致N+区与P衬底短路(电阻约2kΩ)。

预防措施

(1)材料优化

硅铝合金(Al-Si):含0.1%~0.3%硅的铝合金可抑制硅进一步溶解,同时提高抗电迁移能力和机械强度。

金属硅化物:采用Al-Ti-Si、Al-(Ti/W)-PtSi-Si等多层系统,结合阻挡层金属(如Ti、Mo)阻隔铝与硅的直接接触。

(2)结构改进

多晶硅阻挡层:在铝与硅之间沉积多晶硅膜,抑制界面反应。

多层金属化:使用Ti/Al/TiN等复合结构,降低铝与硅的互扩散。

(3)工艺控制

低温工艺:避免高温步骤(如快速单次热退火),减少铝与硅的固相反应。

电流密度限制:优化电路布局,降低局部电流密度,抑制电迁移与热迁移。

金与铝的界面效应

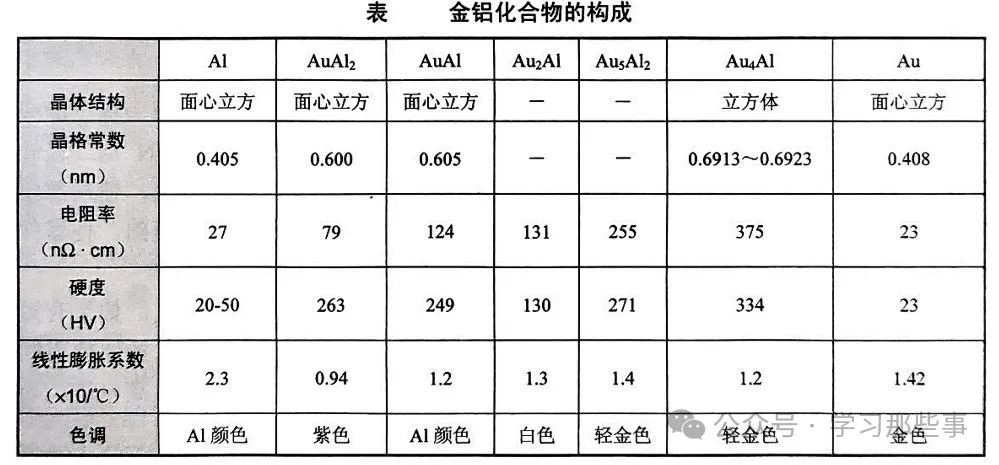

在微电子封装中,金(Au)引线或键合丝与铝(Al)互连线的键合界面(Au-Al)因化学势差异,长期使用或高温(>200℃)存储后,会形成多种金属间化合物(IMCs),导致界面失效。

失效机制

(1)金属间化合物(IMCs)的形成

Au与Al在高温下反应生成多种IMCs,如Au?Al?、Au?Al、Au?Al、AuAl、AuAl?等。这些化合物的晶格常数和热膨胀系数(CTE)与Au、Al差异显著,在键合点内产生应力,导致:

机械性能退化:IMCs(如Au?Al)脆性大,易形成裂纹(白斑),而AuAl?呈紫色(紫斑),进一步降低黏附力。

电性能下降:IMCs的电导率低于纯金属,接触电阻增加,最终引发开路。

(2)柯肯德尔(Kirkendall)效应

在高温(>300℃)下,Au向Al中的扩散速率远高于Al向Au中的扩散速率,导致Al焊盘材料被快速消耗。IMCs(如Au?Al)生长过程中,Al的缺失形成空洞(Kirkendall空洞),空洞扩展至整个键合界面时,Al膜脱落,导致高阻或开路。

(3)化合物生长压力

IMCs的晶格常数大于Au和Al,其生长对键合点施加压力。在温度循环或机械应力下,焊点因压力累积而裂开,加速开路失效。

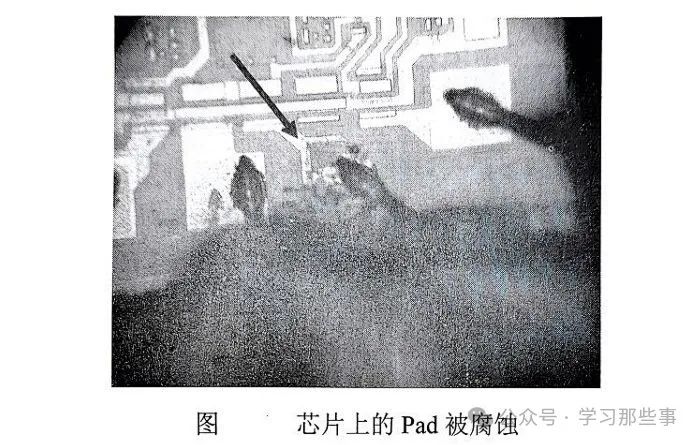

失效表现与诊断

开路失效:键合点电阻急剧升高,但电测试时可能出现时通时断现象(因机械振动或热应力暂时恢复接触)。

高温存储测试:将器件置于200℃以上环境,若开路失效复现,可确认Au-Al界面退化。

影响因素

材料纯度:杂质(如硅、铜)加速IMCs生长。

温度与时间:IMCs生长速率随温度升高呈指数增长,长期存储或高温工作加剧失效。

结构不对称:Al焊盘(厚度约1μm)为有限源,金球为无限源,导致IMCs向Al侧偏析,加速Al消耗。

预防措施

(1)工艺优化

温度控制:键合温度≤300℃,避免高温存储(<200℃)。

时间控制:缩短高温工艺步骤(如键合时间),减少IMCs形成。

(2)材料改进

阻挡层:在Au-Al界面插入扩散阻挡层(如Ni、TiW),抑制IMCs生长。

合金化:采用Al-Si合金(含0.5%~1% Si)提高抗电迁移能力,或改用高熔点金属(如Cu)替代Al。

(3)结构设计

多层金属化:使用Ti/Al/TiN等复合结构,降低Al与Au的直接接触。

键合点优化:增大键合面积,分散应力,减少局部过热。

(4)可靠性测试

加速寿命试验:通过高温存储(250℃)、温度循环(-65℃~150℃)筛选潜在失效器件。

无损检测:利用声学显微镜(SAM)或扫描电子显微镜(SEM)观察键合点空洞和裂纹。

-

芯片

+关注

关注

460文章

52616浏览量

442665 -

集成电路

+关注

关注

5430文章

12139浏览量

368961 -

半导体

+关注

关注

335文章

29026浏览量

240061 -

失效机理

+关注

关注

2文章

29浏览量

11831

原文标题:芯片与应用有关的失效机理

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

射频集成电路半导体和CAD技术讨论

芯片,集成电路,半导体含义

芯片,半导体,集成电路,傻傻分不清楚?

集成电路与半导体

半导体集成电路封装失效机理详解

详解半导体集成电路的失效机理

详解半导体集成电路的失效机理

评论