一前言

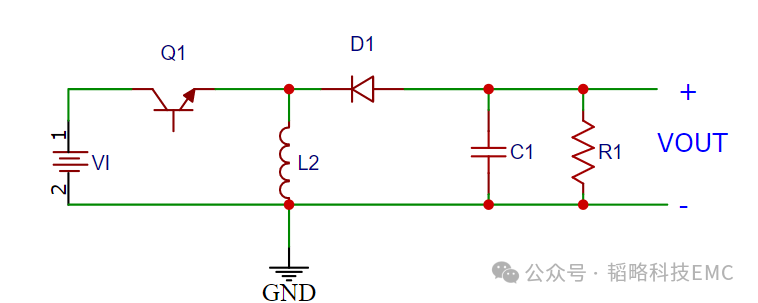

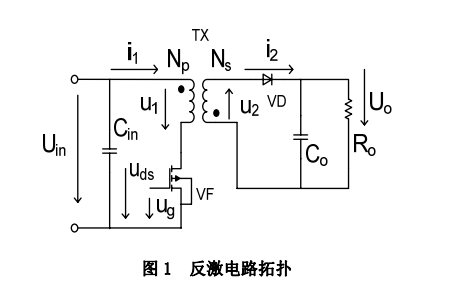

目前市面上机器的电源电路设计,普遍采用buck和boost,或者buck-boost。今天所讲的反激式电路就是基于buck-boost的电路拓扑所演变的,下图是buck-boost的电路拓扑。

反激式电路相对BUCK和boost电路的整改思路有所不同,但是回到本质上,噪声超标还是dv/dt或者di/dt过高的问题,只要找到问题源头,整改措施还是一样。

二前期准备

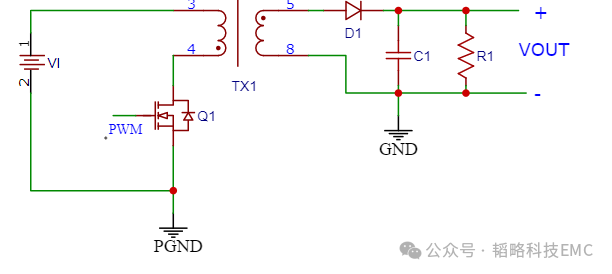

整改前期,我们可以对反激电路工作原理进行理解,这样可以方便我们后续定位噪声源头,对POE供电的反激式电路进行电路分析。以下是反激式电路的电路图,而POE的芯片内部集成MOS管,替代了Q1MOS管。

当Q1导通时输入给初级线圈充电,而次级线圈由于同名端极性相同,续流管D1截止,后端负载由输出电容提供;这也是Flyback名字的由来。当Q1截止时,初级线圈的极性反转,此时次级线圈电压上正下负,续流管Q1导通。对于噪声源来说,大的di/dt和dv/dt 产生的地方:1.变压器TX1;2.MOSFET Q1;3.输出二极管D1。

三案例分析

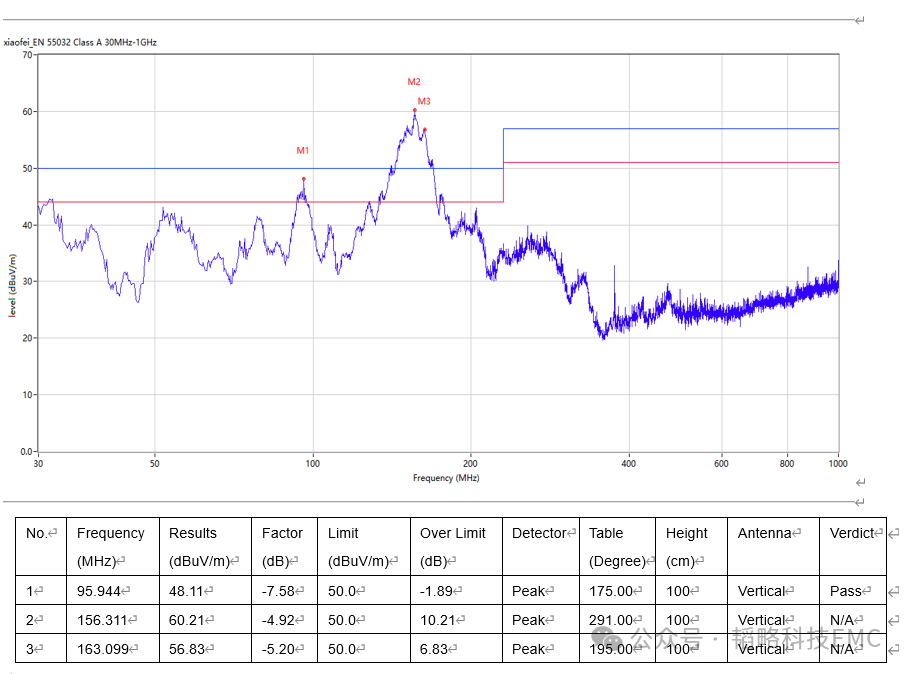

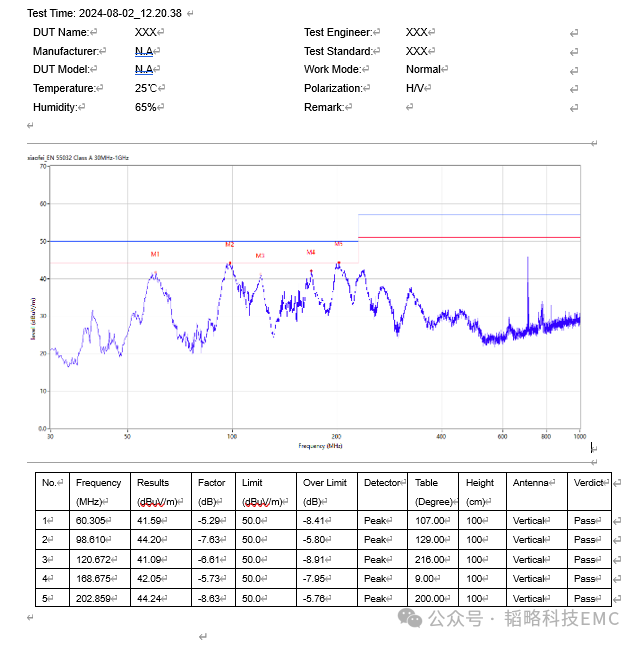

一般采用反激式电路方案,在实际使用过程会遇到雷击或者工作环境恶劣,需要将变压器两端地做隔离来防雷击,这样就会导致噪声走过的路径变大。POE供电的工业摄像头恰好就需要采用这样的方案,由于用在工业上,所以测试等级是EN55032-classA,以下是摸底数据。

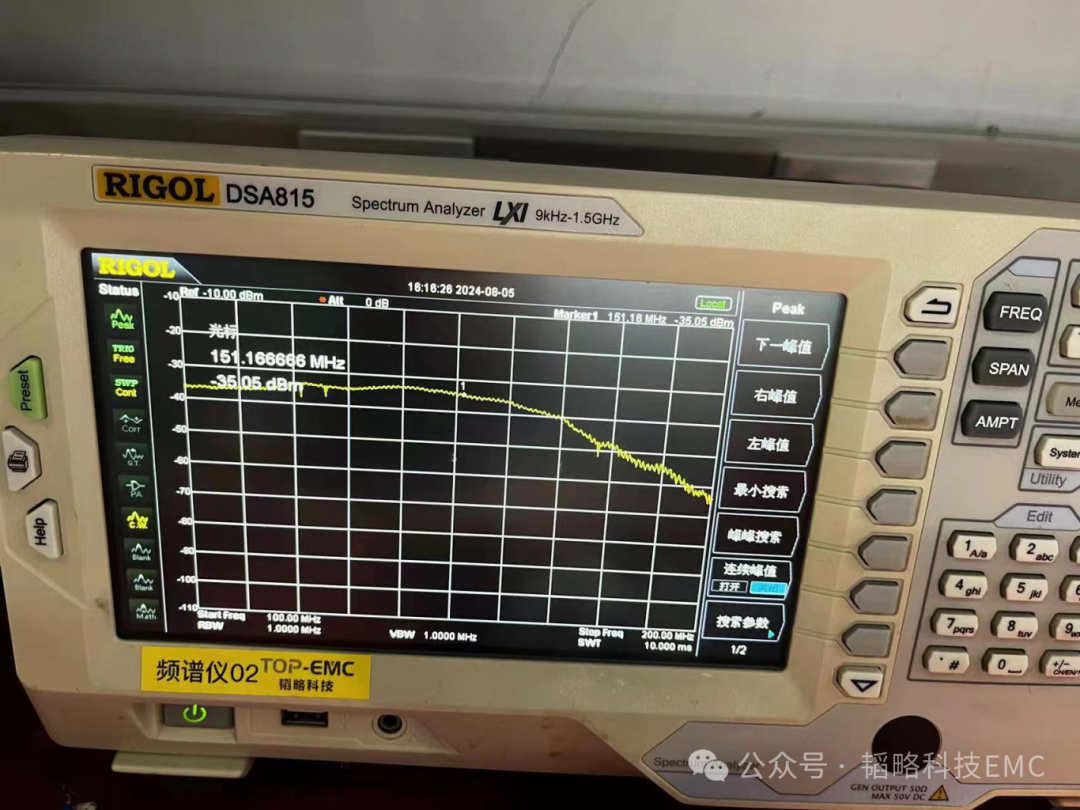

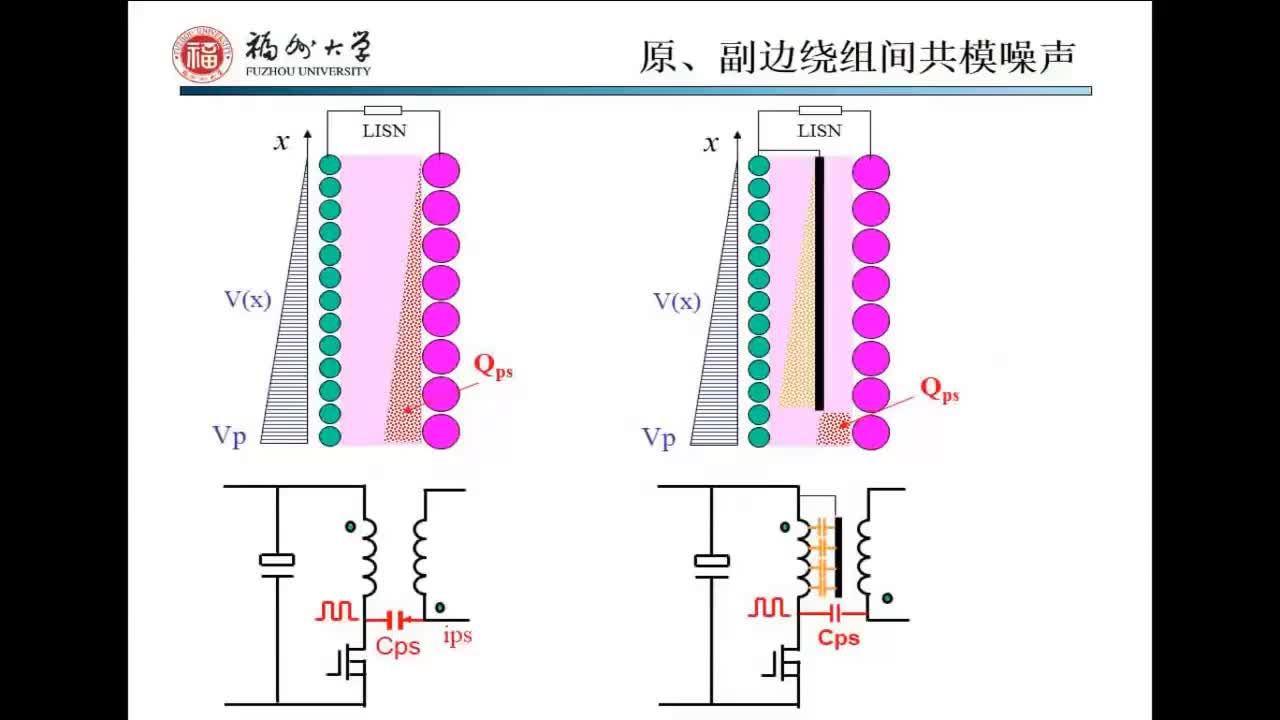

噪声超标呈现包络状,初步判断是电源噪声问题。在近场,通过频谱仪寻找噪声源头,发现在反激式变压器和电源输出端噪声特别高,以下是近场频谱仪噪声扫描图。同时在原理图上,一级电源以后的供电部分由电源管理芯片PMIC供电,电压和电流的突变并没有反激电路的大,同时通过频谱仪,也没有发现对应的噪声频段,因此确定噪声来源是反激式电源造成。

四整改措施

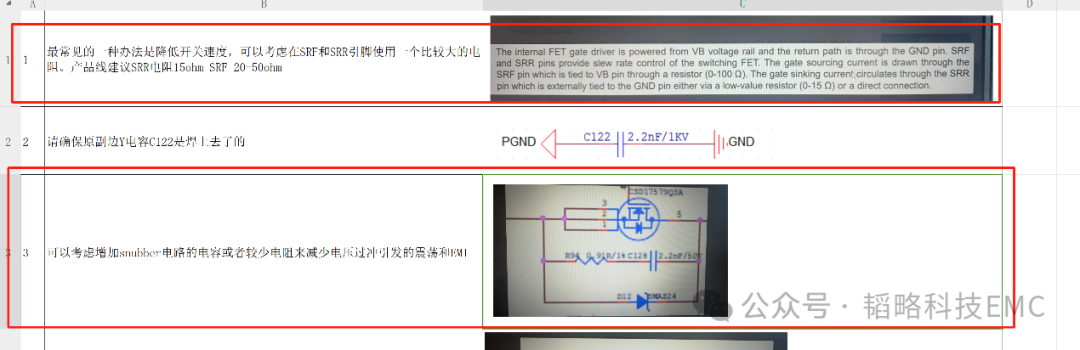

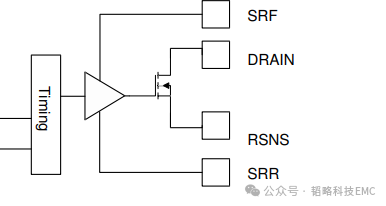

在前期电路设计中我们可以先参考原厂芯片EMI设计,预留抑制EMI的器件位置,后续我们整改就更方便,也有可能不用改板,只需要修改参数。以下是某POE芯片的EMI设计: 1.降低开关速度?让我们看下芯片的内部电路图

1.降低开关速度?让我们看下芯片的内部电路图

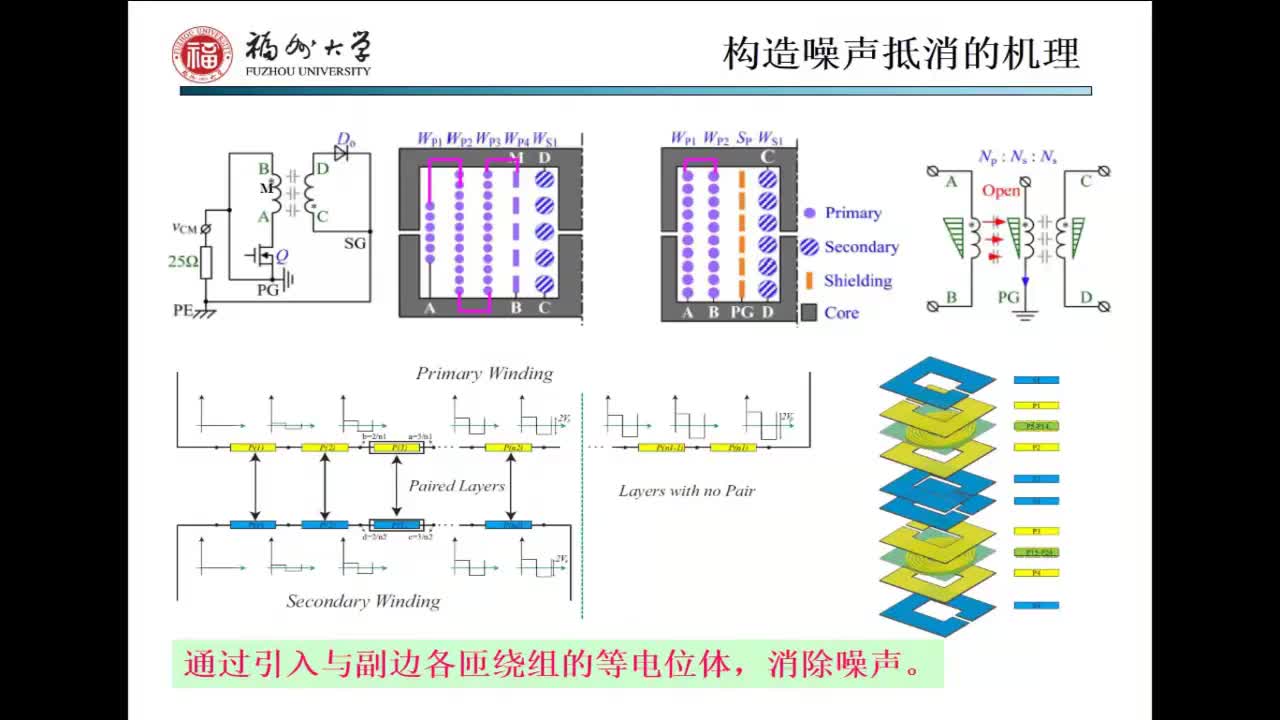

为何将SRF和SRR的电阻调大能抑制EMI呢?原来这两个电阻分别是比较器的上拉和下拉电阻,增大后能使管子充放电时间变长,从而抑制EMI。2.snubber电路又称阻尼电路,通过增加C和R将噪声源的谐振改变,使电路进入过阻尼状态,从而抑制EMI。实际上,该机器前期设计就有上述这两个措施,依旧不能通过测试。因此我做了以下措施,整改措施分为三步:(1)针对150M左右超标频率,对续流管D1输出端对地并1nF电容,通过高频电容将输出回路减小;(2)对变压器进行包屏蔽接前端地,减小噪声对地阻抗;(3)在路径上进行消耗,在输入端加入(TLDCM4745-2-102TF-TA)共模滤波器吸收共模噪声。以下是整改后数据:

五总结

EMC主要分为三要素:1.骚扰源;2.敏感源;3.耦合路径。在骚扰源上,对续流二极管输出端对地并1nF电容,通过高频电容将输出回路减小,对变压器进行屏蔽接地。在耦合路径上,在电源输入端加共模滤波器,对噪声进行消耗。在测试中,敏感源相当于测试天线。在前期电路设计中,可以提前预留抑制EMI的电阻电容,这样能减少后期改板次数,加快量产时间。以上是小编的拙见,有任何错误,欢迎指出。

-

噪声

+关注

关注

13文章

1140浏览量

48241 -

电源电路设计

+关注

关注

1文章

13浏览量

8106 -

emc

+关注

关注

172文章

4190浏览量

187366 -

反激电路

+关注

关注

7文章

46浏览量

22379

发布评论请先 登录

《电子发烧友电子设计周报》聚焦硬科技领域核心价值 第5期:2025.03.24--2025.03.28

反激电路的揭秘:超标噪声的背后秘密

反激电路的揭秘:超标噪声的背后秘密

评论