“解析数模转换器与模数转换器的工作原理——从电阻阶梯网络到Delta-Sigma调制技术。”

微控制器正在“吞噬”整个世界。如今,即使是闪烁LED等最基础的任务,使用微控制器也比用分立元件搭建振荡电路或依赖曾经无处不在的555定时器芯片更便宜、更简单。

然而,在这个日益由软件定义的世界中,0和1并非万能。图像传感器将光强记录为一系列模拟值;播放音乐的扬声器,其振膜需要移动到除了“完全向内”和“完全向外”之外的多种位置。最终,几乎所有复杂的数字电路都需要专门的数模转换器(DAC)和模数转换器(ADC)来连接物理世界。这些转换器通常集成在微控制器的芯片中,但其原理仍值得探究。

简单的数模转换器(DAC)

将数字信号转换为模拟信号的核心在于将一定位长的二进制数映射为量化输出电压范围。例如,一个4位DAC有16种可能的输出电压,其典型行为如下:

0000(0) =0V 0001 (1) =1/15Vdd 0010 (2) =2/15Vdd 0011 (3) =3/15Vdd ...1111(15) = Vdd

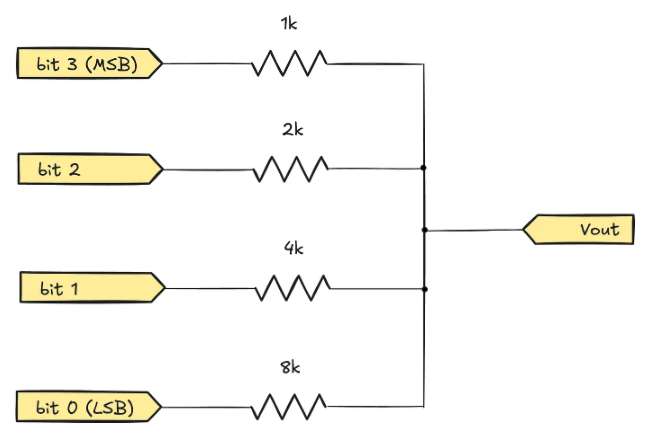

实现此类转换的最简单方法是基于电阻的二进制加权DAC:

显然,当二进制输入为0000时,模拟输出应为0V;反之,若输入为1111,则输出必须达到Vdd。对于中间数值的输入,我们应获得电阻加权平均值,其中每个比特位的影响权重是其高位比特的一半。这种特性与二进制数的工作原理完美契合。

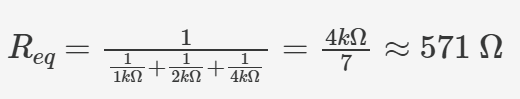

我们可对此进行更严谨的电路分析。以输入值 0001 为例:此时高位三个电阻(比特位#1、#2和#3)并联接地,其等效电阻值为:

而最低有效位(LSB)对应的电阻则连接至 Vdd。整个电路可视为由两个串联电阻构成的Vdd-地分压网络,其输出电压为:

类似地,当输入为 1110(十进制14)时,输出电压Vout ≈ 14/15 Vdd。这与我们期望的线性响应特性完全吻合。

该 DAC 架构的主要缺陷在于所需电阻值很快会变得不切实际。为避免静态电流过大,最高有效位(MSB)对应的电阻值不能过低(1 kΩ是合理的起始值)。但对于16位DAC而言,这意味着最低有效位电阻需达到 1 kΩ × 2?? ≈ 32 MΩ;若实现24位分辨率,则需数吉欧姆(GΩ)量级的电阻。在集成电路晶圆上制造如此高精度的大阻值电阻极具挑战性,若还要求其具备相同的温度系数,则难度更甚。

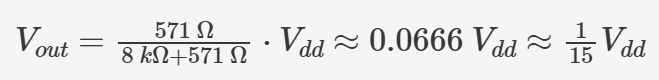

针对这一难题,工程师提出了巧妙的 R-2R 梯形 DAC 架构解决方案:

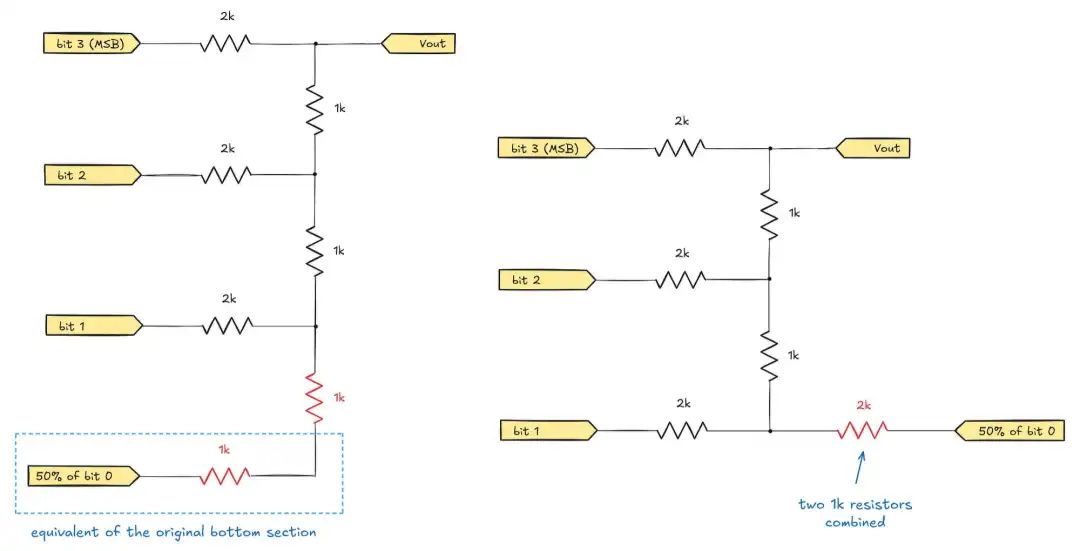

相较于传统架构,这种 R-2R 梯形电路的没那么直观,但其工作原理具有相似性。为解析其设计逻辑,我们从最底层结构入手:即位于比特位#0处的两个水平放置的电阻。这两个电阻向电路其余部分提供等量电流,因此其功能等效于一个连接在合成输入电压上的 1 kΩ电阻。该合成电压的取值逻辑为:当 LSB=0 时等于0V,LSB=1 时等于 Vdd/2。换言之,比特位#0的输入信号在此处被压缩为50%的权重。

通过这种等效替换,我们得到左图所示的简化电路。进一步观察,底层结构中两个串联的1 kΩ电阻(红色标注)可等效为右图中的单个2 kΩ电阻:

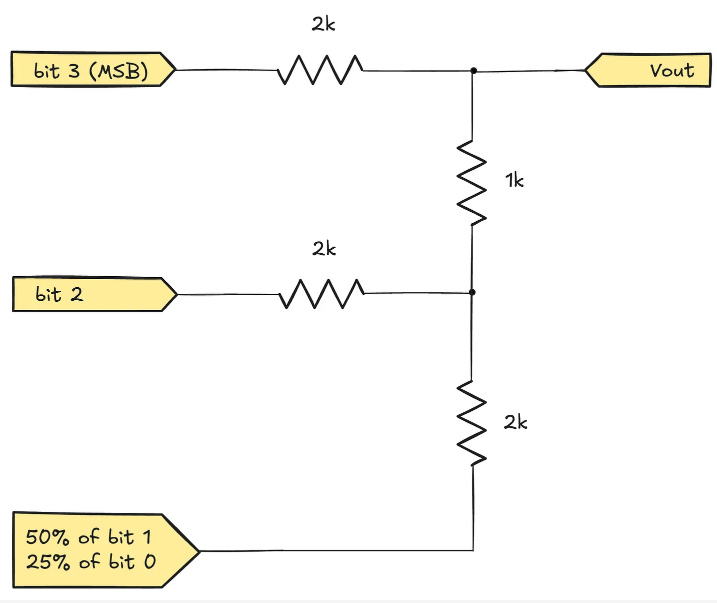

此时可发现,新电路中比特位#1的配置情况与先前对比特位#0的分析具有相似性。其底层结构包含一个连接对应二进制输入的 2 kΩ 电阻,以及另一个连接前级合成电压的 2 kΩ 电阻。实际上,该结构实现了两种信号的50%混合效应。无论上层电路如何变化,此部分均可等效替换为连接新合成输入信号的单个 1 kΩ 电阻:

此迭代过程可持续推进。最终可明确推导出:输出电压将由比特位#3贡献50%,比特位#2贡献25%,比特位#1贡献12.5%,比特位#0贡献6.25%。

(需说明的是,上述权重之和未达100%,因为梯形结构底部的初始下拉电阻会损耗部分电压区间。)

过采样DAC

尽管前文讨论的架构简洁优雅,但在高分辨率(尤其是超过10-12位)场景下会面临线性度挑战。虽然电阻元件精度可达0.1%级别,但在16位数模转换器中,最低有效位(LSB)的理论影响权重仅为最高有效位(MSB)的0.003%。若MSB电阻值与设计值存在0.1%偏差,就足以导致整个系统的线性度严重劣化。

这一困境催生了过采样平均型DAC的研发。此类器件通过高频输出低分辨率交替信号,随后利用输出端的低通滤波器对信号进行平均化处理,从而生成更精细的低频中间电压。

举例说明:对四个连续的单比特DAC输出进行平均处理,可在原生输出范围间插入三个中间电压值,相当于获得两位有效精度提升:

平均(0,0,0,0)=0平均(0,0,0,1)=0.25平均(0,1,0,1)=0.5平均(0,1,1,1)=0.75平均(1,1,1,1)=1

当然,这种方案需要付出代价:部分高频噪声难以被滤波器完全抑制。尽管如此,该方案整体上相当稳健。事实上,消费级音频设备中大量DAC采用单比特脉冲序列(工作频率达数十万赫兹)来实现宣称的24位输出分辨率。虽然电路本底噪声往往使该指标的实际意义有限,但单比特DAC的线性度表现极佳——因为精确时序控制远比制造超精密电阻容易实现。

经典模数转换器(ADC)

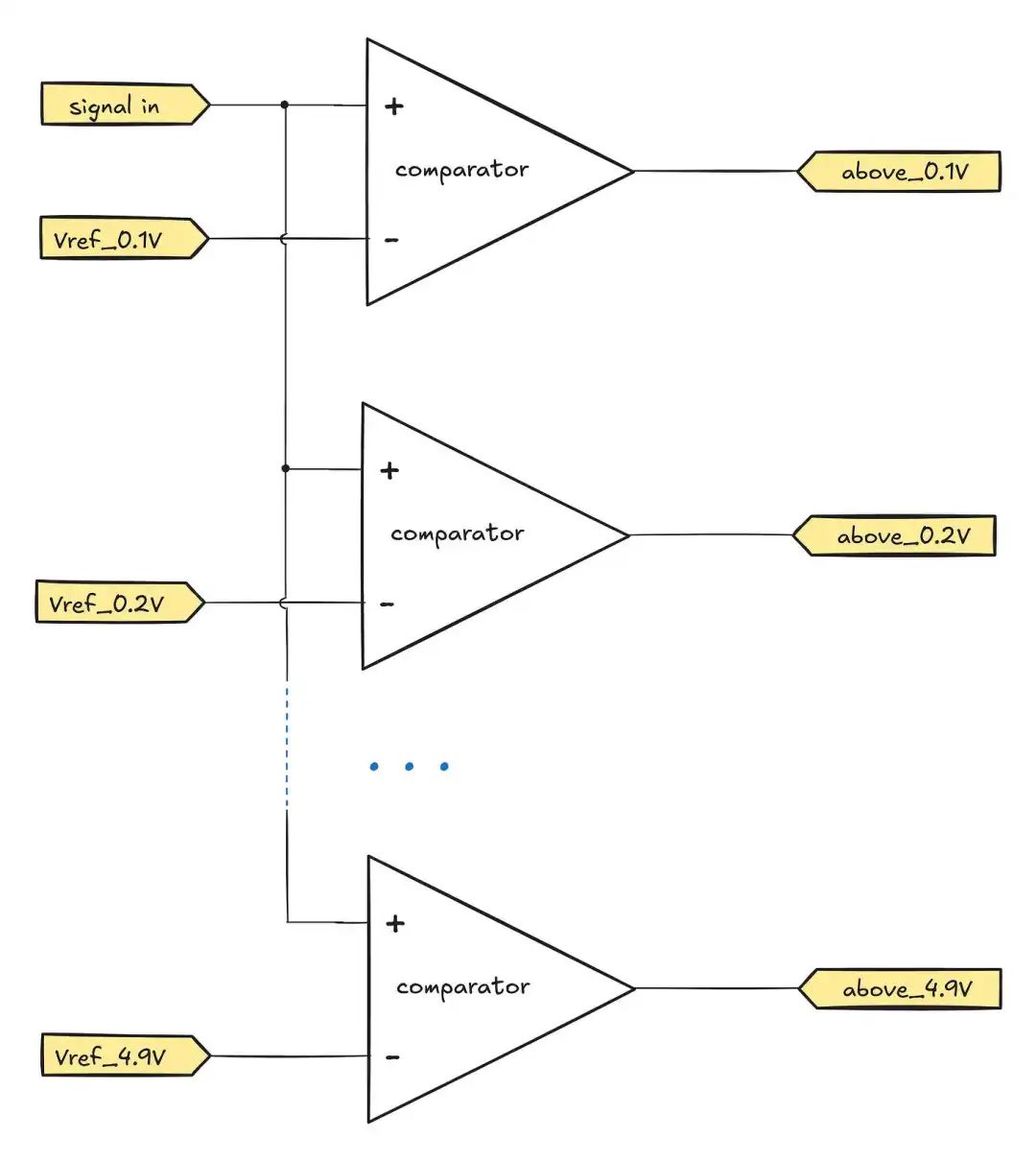

相较于数模转换,将模拟电压转换为二进制数的过程更为复杂。要实现精准的瞬时电压量化,唯一实用的方法是针对每个量化层级配置独立的电压比较器(开环运算放大器),例如:

并联比较型ADC(也叫"flash" ADC)在需要极致速度的特殊场景中偶有应用,但其电路规模随位数呈指数级增长——芯片功耗、输入电容等参数随之急剧恶化。因此这类ADC的分辨率通常不超过4-8位。

更常见的架构是采用单一比较器与可预测变化的参考电压协同工作。一个基础实例是通过电阻对电容充电的电路:通过测量充电开始到比较器触发的时间间隔,即可反推出输入电压值。

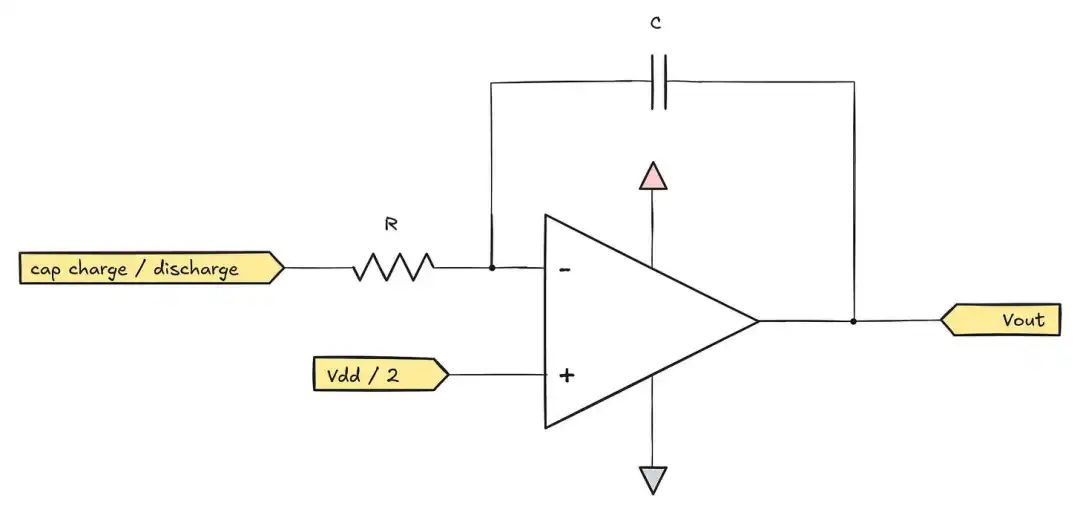

实践中,由于电容恒压充电曲线具有非线性特性,通常改用积分器电路生成参考信号:

积分器是在标准运放电路中引入一个有趣的微调:用反馈电容替代常规反馈电阻。当反相输入端(Vin-)电压高于同相端(Vin+)时,运放输出端电压立即下降,允许充电电流流经电阻 R 对电容充电。

该反馈机制的核心是维持 Vin- 与 Vin+ 电位相等。根据欧姆定律,在固定输入电阻下,充电电流仅由输入电压和电阻 R 决定。当充电电流恒定时,电容电压呈线性上升特性。若输入方波信号,积分器将输出近乎完美的三角波,这为ADC提供了极为理想的线性参考信号。

充电开始到比较器触发的时间间隔不仅取决于输入电压,还与三角波斜率相关,而斜率本身受 R 和 C 参数精度制约。为提高精度,ADC 需测量三角波多个周期内比较器输出信号的占空比。例如,25% 占空比意味着被测电压处于 Vdd 的 75% 处,该测量结果与R、C精度无关。

基于斜率积分的 ADC 具备高精度与低噪声优势,但存在转换速度缓慢的缺陷。性能优化的解决方案是采用数字辅助技术:即逐次逼近寄存器(SAR)架构。其核心原理是通过内置 DAC 生成参考电压,并执行类似计算机科学中二分查找的算法:首先将输入电压与 Vdd/2 比较,若输入更高则排除下半区间,随后在剩余区间的中值(3/4 Vdd)处进行下一轮比较。通过逐次对半压缩搜索范围,仅需数次迭代即可锁定精确值。代价是受DAC线性误差影响存在精度损失,且数字开关噪声有所增加。

高端("流水线")ADC常采用多技术融合方案:例如先通过 "flash" ADC 架构快速确定部分高位,再通过多级缩放与转换处理获取更多低位数据。

Delta-sigma(Δ-Σ) ADC

至此,ADC技术已展现出多样化的实现路径,但最精妙的方案当属高频插值法,通常采用 Δ-Σ(Delta-Sigma)调制技术。其工作机制颇具反常规特性。

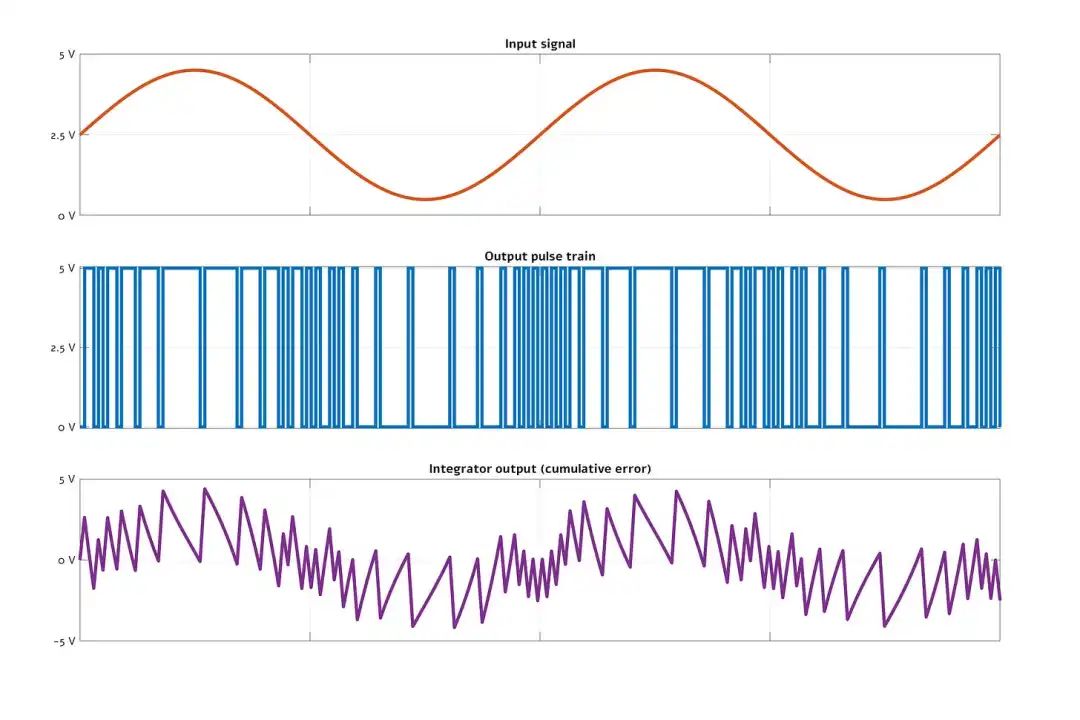

基础型1位Δ-Σ ADC通过比较器级高速输出"0"或"1"逻辑脉冲序列。这些数字输出被引入特殊反馈回路,用于计算二进制输出与输入信号的差异:

简化版1位Δ-Σ ADC架构示意图(时钟信号省略)

在多数情况下,模拟输入电压并不等于数字输出的两种可能电压值,因此位于Δ-Σ ADC前端(左图)的增益为1的运放会输出瞬时大幅正向或负向误差电压。

这些瞬时误差随后输入积分器。如本文前文所述,积分器通过对误差进行时间积分(将累计值存储在线性充电的电容中)实现误差累积。若输入信号正向偏离脉冲序列的平均值,积分器输出电压将逐步攀升;反之则逐渐下降。

该累计误差最终输入至产生实际输出比特流的正相端比较器。其核心逻辑在于:若误差为正(即ADC输出"0"过多),比较器将强制输出"1";反之若累计误差为负(输出"1"过多),则转向输出"0":

一阶Δ-Σ ADC典型工作波形

尽管这种测量方式看似非理性,但通过数字处理看似混沌的高频脉冲占空比,即可精确反推出模拟输入值。该架构的最大优势在于模拟误差源极少,因此线性度表现卓越。代价则是为实现合理精度,ADC工作时钟频率需远高于目标采样率。

需特别说明的是,"Δ-Σ"术语也用于指代前文所述的过采样插值型DAC子类。但与ADC相比,这类DAC的智能程度显著降低:其脉冲调制主要发生在数字域,缺乏精妙的模拟反馈机制。

原文转载自:https://lcamtuf.substack.com/p/dacs-and-adcs-or-there-and-back-again,经过翻译及校验

-

adc

+关注

关注

99文章

6720浏览量

549496 -

dac

+关注

关注

44文章

2413浏览量

194039 -

模拟

+关注

关注

7文章

1438浏览量

84580 -

数字

+关注

关注

1文章

1698浏览量

51958 -

KiCAD

+关注

关注

5文章

265浏览量

9588

发布评论请先 登录

混合信号设备接地须知 ADC的数字地DGND模拟地AGND接地谜团

高速ADC/DAC在现代全数字雷达中的应用

DAC 与 ADC:数字与模拟的往复之旅

如何挑选ADC和DAC?

ADC与DAC的原理参考电压

ADC/DAC,ADC/DAC的原理是什么?

什么是DAC_adc是什么意思

DAC 与 ADC:数字与模拟的往复之旅

DAC 与 ADC:数字与模拟的往复之旅

评论