文章来源:学习那些事

原文作者:小陈婆婆

本文主要讲解了Bi-CMOS工艺。

Bi-CMOS工艺将双极型器件(Bipolar)与CMOS工艺结合,旨在融合两者的优势。CMOS具有低功耗、高噪声容限、高集成度的优势,而双极型器件拥有大驱动电流、高速等特性。Bi-CMOS则能通过优化工艺参数,实现速度与功耗的平衡,兼具CMOS的低功耗和双极器件的高性能,本文分述如下

Bi-CMOS概述

Bi-CMOS工艺分类

Bi-CMOS工艺详解

Bi-CMOS的核心优点

驱动能力增强:相同尺寸下,Bi-CMOS逻辑门的驱动电流更大,驱动大电容负载时速度显著提升。

低功耗特性:与CMOS门电路静态功耗相当,但动态(交流)功耗更低。

接口兼容性:可直接驱动TTL或ECL电平接口,简化系统设计。

主要应用场景

存储器电路:如SRAM中,双极器件构成灵敏放大器,检测微小电压变化。

高速数字电路:双极器件驱动大电容负载,提升电路速度。

数模混合电路:结合CMOS的数字逻辑与双极器件的模拟精度,适用于高精度传感器或射频电路。

Bi-CMOS工艺分类

根据应用场景和成本需求,Bi-CMOS工艺分为三类:

低成本、中速数字Bi-CMOS

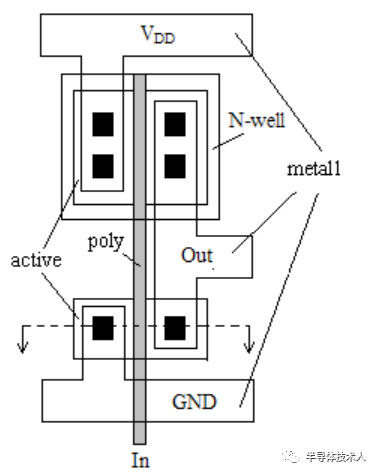

工艺特点:基于标准N阱CMOS工艺,增加一块掩膜版形成双极晶体管的P型基极,N阱作为集电极。

结构:发射极由NMOS源漏注入完成,采用LOCOS隔离。

缺点:集电极串联电阻(Rc)较大(约2kΩ),限制强电流下的性能。

高成本、高性能数字Bi-CMOS

工艺特点:确保CMOS和双极器件性能均达到单独工艺水平,需额外增加3~4块掩膜版。

实现方式:

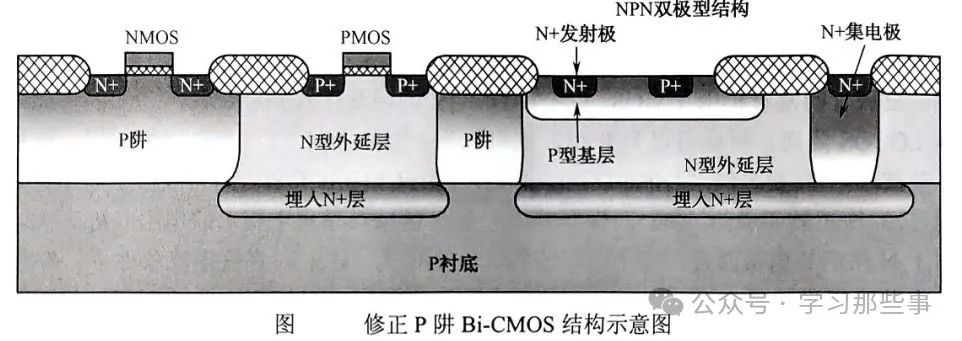

修正P阱工艺:优化阱结构以提升双极器件性能。

修正双阱工艺:通过深阱隔离技术减少寄生效应,提高集成度。

数模混合Bi-CMOS

数模混合Bi-CMOS工艺与数字Bi-CMOS的核心区别在于其需适应宽范围工作电压(尤其是高压场景),这对器件结构和工艺设计提出了特殊要求。

特点:工作电压范围宽(模拟部分需高压),复杂工艺通常由双极工艺衍生而来。

关键器件:PNP晶体管、精密电阻/电容,用于模拟电路的低噪声和匹配特性。

以下从工艺分类、关键设计考量及典型工艺步骤展开分析:

数模混合Bi-CMOS工艺根据电压和功率需求分为两类:

中压工艺(10~30V):基于标准CMOS流程优化,需平衡高电压耐受与器件性能。例如,加厚栅氧以提升栅压承受能力,但会牺牲部分驱动电流。

大功率工艺(>30V且>1A):采用功率模拟工艺,需强化器件的电流承载能力和散热设计,常用于电源管理或电机驱动等场景。

关键设计考量——高压耐受性

栅氧加厚:防止高栅压下氧化层击穿,但导致MOS管饱和电流降低,需通过工艺调整(如优化沟道掺杂)补偿性能损失。

隔离结构优化:采用扩散隔离(如CDI)或深沟槽隔离,避免高压下寄生器件开启。

模拟器件精度

多晶硅电阻:温度系数优于扩散电阻,适用于高精度模拟电路

PIP电容:多晶硅-绝缘层-多晶硅结构(Poly-Insulator-Poly)寄生效应小,适合开关电容电路和A/D转换器。

寄生效应抑制

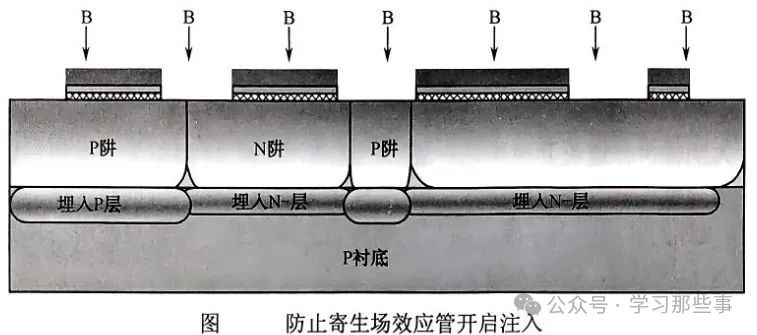

防寄生场效应管注入:通过离子注入调整寄生管阈值电压,避免高压下意外导通。

技术挑战与优化方向

集电极电阻问题:低成本工艺中Rc过大,需通过优化掺杂或结构改进(如埋层集电极)降低电阻。

工艺复杂度:高性能和数模混合工艺需平衡掩膜步骤增加带来的成本与设计灵活性。

功耗与速度权衡:根据应用场景调整双极器件比例,例如在关键路径插入双极器件以提升速度,其余部分保持CMOS低功耗。

Bi-CMOS工艺详解

P阱与双阱工艺对比

P阱Bi-CMOS工艺(SBC工艺)

工艺特点

材料结构:采用P型衬底+N型外延层,通过重掺杂的N+埋层形成双极晶体管的集电极

核心优势

低集电极电阻(Rc):N+埋层显著降低Rc,提升电流驱动能力。

抗闩锁能力增强:N型外延层替代P型外延,降低寄生PNPN路径的增益。

闩锁敏感性降低:埋层结构减少衬底耦合效应。

隔离方式:P阱提供双极结隔离,防止相邻集电极间的干扰。

掩膜增加:需额外3块掩膜版(N+埋层、深N+集电极、P基极区)。

应用场景:适用于对集成度要求适中、需平衡成本与性能的Bi-CMOS电路。

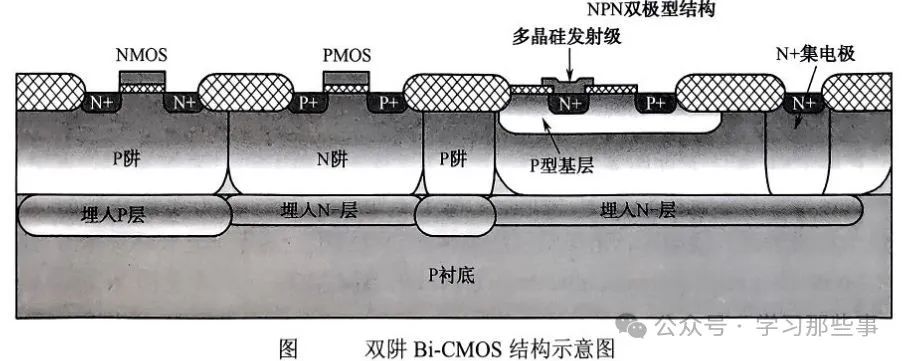

双阱Bi-CMOS工艺(高性能工艺)

工艺改进

自校准埋层:引入埋入P层

使相邻集电极间距缩小至亚微米级,提升集成度。

外延层优化:采用近本征(低掺杂)外延层,灵活调整掺杂浓度以满足双极与PMOS器件需求。

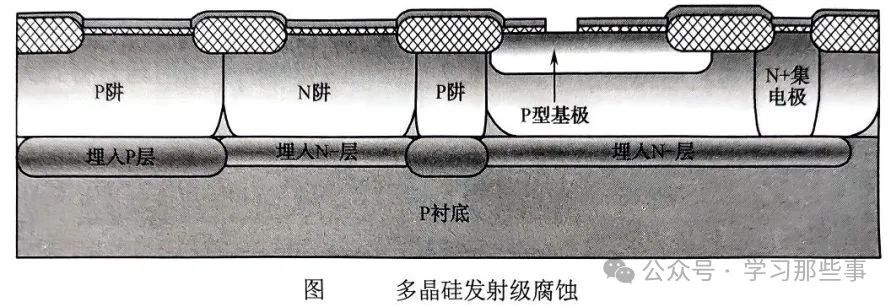

多晶硅发射

性能提升:浅发射极+窄基区宽度提高截止频率。

工艺简化:同一多晶硅层兼作CMOS栅极与双极发射极,减少额外步骤。

掩膜增加:需4块额外掩膜版(埋入N+、深N+扩散、P基极、多晶硅发射极)。

技术优势

高密度集成:紧凑的集电极布局支持复杂电路设计。

灵活性:独立优化P阱与N阱掺杂,适配不同器件需求。

电压兼容性:支持3.3V/5V电路,适用于高性能混合信号系统。

双阱Bi-CMOS工艺步骤详解

初始材料:P型轻掺杂100晶向硅片。

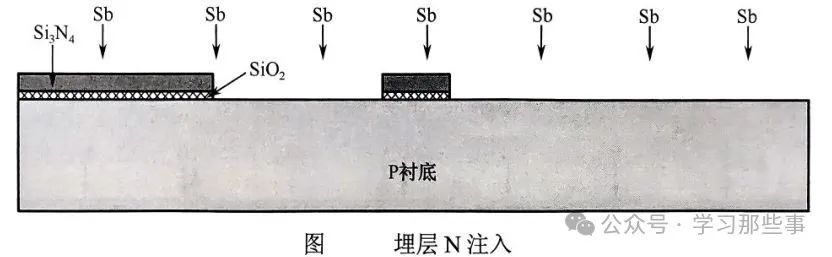

埋层形成

N埋层:光刻定义区域,锑注入后退火,形成N+埋层

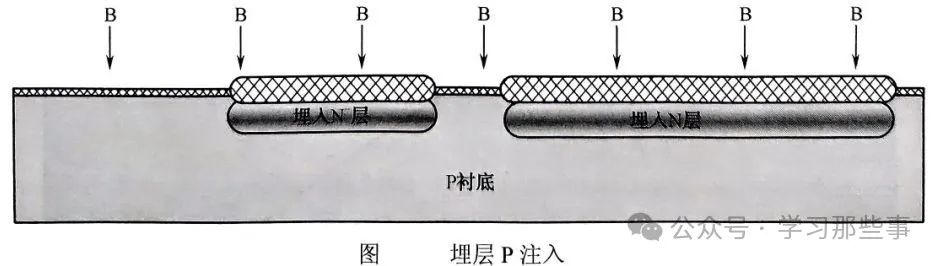

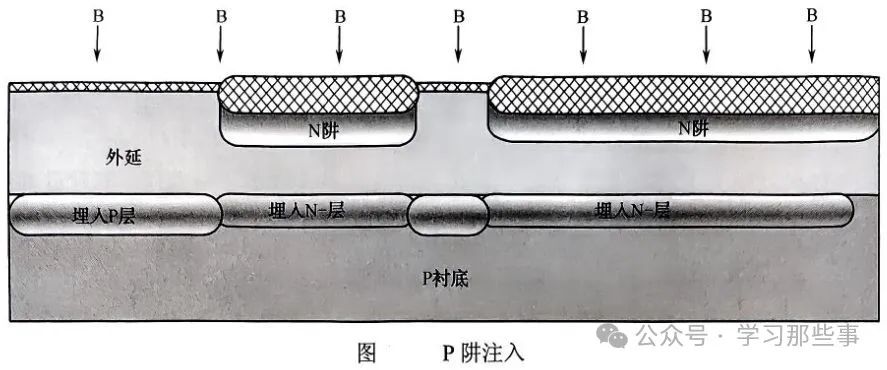

自对准P埋层:硼注入时,厚氧化层阻挡N埋层区域,形成P埋层

外延生长:沉积外延层,掺杂浓度由器件需求决定。

阱工艺

N阱:磷注入并推阱,厚氧化层阻挡后续硼注入。

P阱:利用N阱氧化层阻挡,硼注入形成P阱

有源区与隔离

LOCOS隔离:多晶硅缓冲层提高集成度

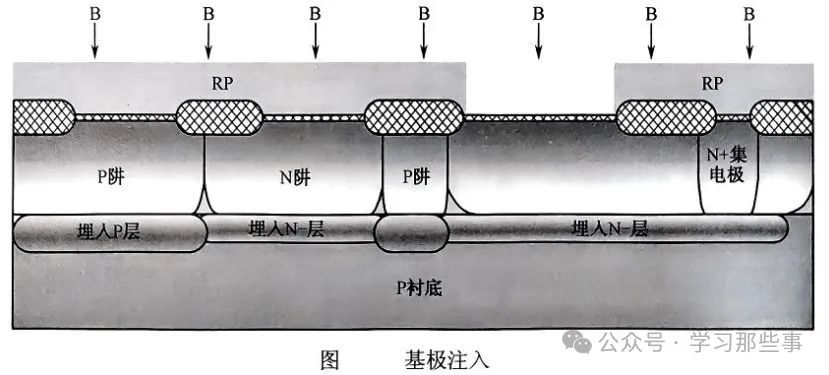

双极器件制作

N+集电极:磷注入并扩散至埋层N

P基极:硼注入形成基区。

多晶硅发射极

双层多晶硅:第一层定义发射极窗口,第二层形成发射极接触

后续工艺:与标准CMOS工艺兼容,完成金属互联等步骤。

-

CMOS

+关注

关注

58文章

6035浏览量

239167 -

工艺

+关注

关注

4文章

690浏览量

29523 -

数字电路

+关注

关注

193文章

1641浏览量

82031 -

数模混合

+关注

关注

0文章

24浏览量

9429

原文标题:Bi-CMOS工艺解析

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CMOS,Bipolar,FET这三种工艺的优缺点是什么?

特征工艺尺寸对CMOS SRAM抗单粒子翻转性能的影响

视频驱动芯片ISL59830相关资料推荐

《炬丰科技-半导体工艺》CMOS 单元工艺

分享芯片SWF254N

MSC1163 pdf datasheet (40-Bit

A705,pdf,datasheet (220mA ADVA

OCP8110,pdf 350mA Advanced Cur

一种采用Bi-CMOS 缓冲器的LDO电路设计

新型BiCMOS集成运算放大器设计

LIN通信总线标准和混合信号半导体工艺技术提高汽车维护性能和可靠性

什么是BCD工艺?BCD工艺与CMOS工艺对比

Bi-CMOS工艺解析

Bi-CMOS工艺解析

评论