在现代电子电路设计和应用中,寄生参数是指那些并非设计者最初所期望的,但在电路或元器件中由于物理结构、材料特性或布局布线等因素而自然产生的非预期电气参数。这些参数虽然不是设计之初所考虑的,但它们对电路的性能和行为有着不可忽视的影响。在本次研究中,重点探讨寄生电感对栅极振荡的影响,同时通过实验来逐步验证。

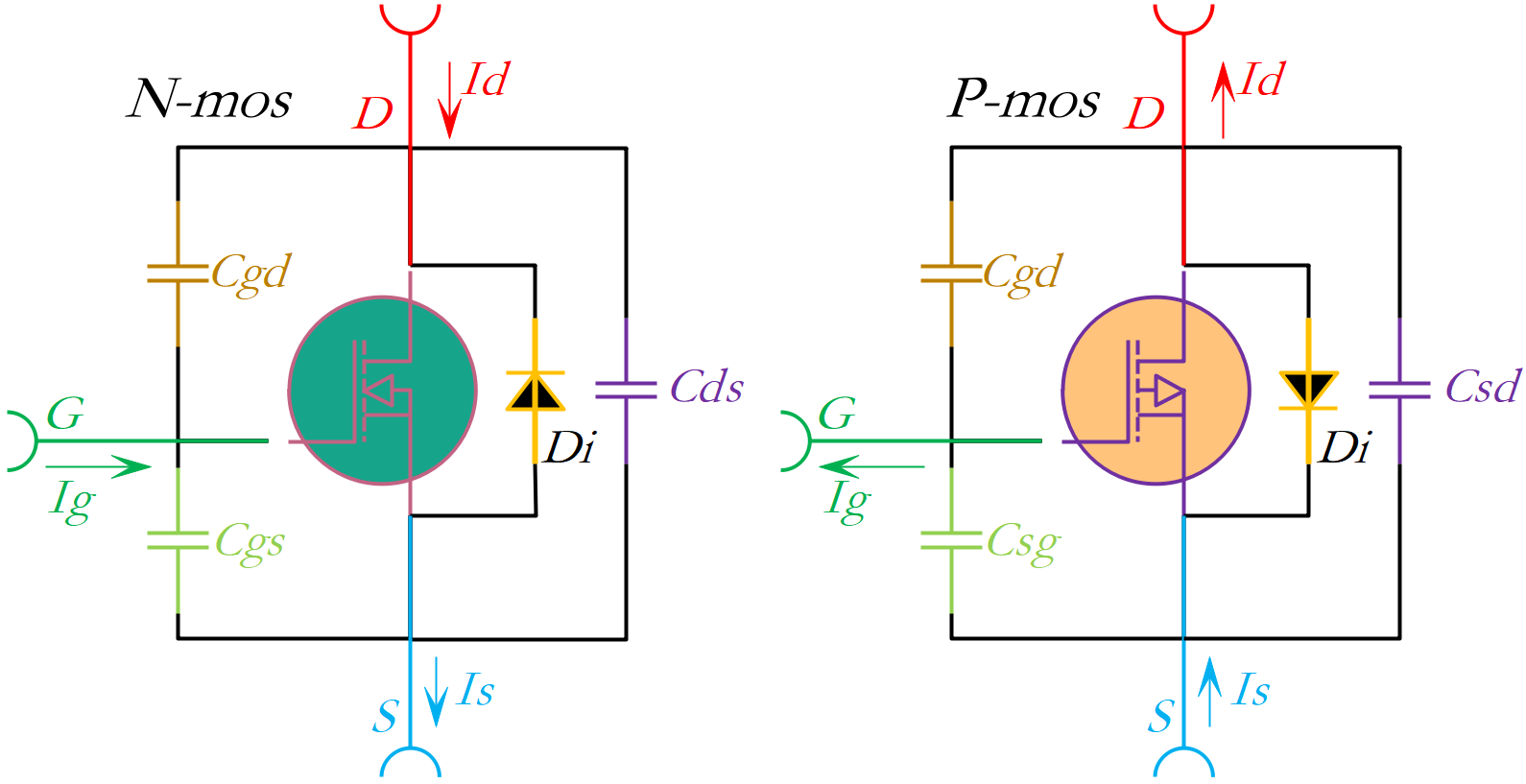

在MOSFET、IGBT等功率器件中,寄生参数主要分为寄生电容,电阻,电感三方面,其中寄生电感的存在会对栅极振铃产生显著影响。其中,栅源极之间(焊引脚和键合线)的寄生电感L是导致栅极振铃的主要因素。根据U=L*di/dt,开关速度快,即di/dt大,则在源极引脚寄生电感上产生的感应电压更大。此时,Vgs外部测量的电压主要由内部Cgs电压叠加栅源寄生电感(3-7nH)上感应电压。

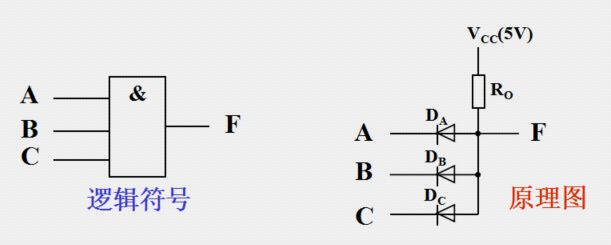

图1 寄生参数模型

实验场景

为了测试器件内外GS电压差异,设计一组对比实验。通过开窗方式漏出芯片打线,采用接地环方式直接测试芯片GS两端(此处测量波形代表器件真实GS波形),同时用差分探头靠近器件的GS引脚处作为常规测试方法(MOS外部测量波形)。

图2 实验平台

对器件采取了开窗处理(如图3)在不损伤芯片的前提下,同时保证前后测试条件一致。

图3 开窗改造示意图

此时我们将G(栅极)和S(源极)引线暴露出来,并使用探针直接对打线和引脚处的波形进行测试。这种方法可以排除键合点位置的寄生干扰,同时可以最直观地展示出差异性。

图4 实际测试图

实验结果

测到开启波形如下:

外部测到的Vgs电压会在米勒平台处有13V左右的振幅,而内部的Vgs电压此时波动幅度非常小(轻微波动主要是电流和电压突变时电磁干扰影响)。

测到关断波形如下:

外部测到的Vgs电压会在Ids突然下降时有很大负压尖峰(约20V)。而内部的Vgs此时几乎不变。

?

?总结

在米勒平台处振荡,Vgs外部测量的很大尖峰电压是由源极引脚寄生电感在高di/dt时感应电压叠加到米勒平台电压上产生的。此时外部测量值也完全不代表器件内部Vgs真实电压。

另外,由于此时器件工作在饱和区(米勒平台),内部Vgs的轻微变化都会使沟道饱和电流大幅度跳变。所以可以通过监测Ids或Ice电流是否出现大幅度波动来侧面反映器件内部的Vgs变化(因为内部真实Vgs往往没办法测量)。

此外,为了减少寄生电感对栅极振荡的影响,建议可以采取以下几种措施。

1、首先,优化电路设计是关键。合理设计电路布局和走线,减少寄生电容和寄生电感的产生。例如,采用短而粗的导线连接栅极和驱动电路,以降低寄生电感;在栅极和源极之间加入适当的去耦电容,以减小寄生电容的影响。

2、其次,选择合适的元器件也非常重要。通常我们需要选用寄生参数较小的元器件,如低寄生电容和低寄生电感的MOSFET等,这点在产品的规格书内都会有所体现。此外,增加阻尼元件也是抑制谐振和震荡的有效方法。在电路中增加阻尼电阻或阻尼电容等,以抑制谐振和震荡的产生。

3、优化驱动电路设计,确保栅极电压能够稳定、快速地变化,其中也包括PCB的绘制与铜箔的合理铺置。例如,采用合适的驱动电阻和驱动电流源,优化电路布局和布线,合理安排元器件的位置,减少信号传输路径上的干扰和损耗,采用合适的线宽、线距和走线方式,避免信号间的串扰和耦合。

-

电阻

+关注

关注

87文章

5634浏览量

175367 -

电感

+关注

关注

54文章

6210浏览量

104358 -

栅极

+关注

关注

1文章

185浏览量

21384 -

寄生电容

+关注

关注

1文章

299浏览量

19811 -

寄生参数

+关注

关注

0文章

17浏览量

2198

原文标题:寄生参数对栅极震荡的影响

文章出处:【微信号:NcePower,微信公众号:无锡新洁能股份有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文详解MOS的寄生模型

一文详解寄生参数对栅极震荡的影响

一文详解寄生参数对栅极震荡的影响

评论