半导体芯片集成电路(IC)工艺是现代电子技术的核心,涉及从硅材料到复杂电路制造的多个精密步骤。以下是关键工艺的概述:

1. 晶圆制备

材料:高纯度单晶硅(纯度达99.9999999%),通过直拉法(Czochralski)生长为圆柱形硅锭。

切割与抛光:硅锭切割成0.5-1mm厚的晶圆(常见尺寸12英寸/300mm),经化学机械抛光(CMP)达到纳米级平整度。

2. 氧化工艺

热氧化:在高温(800-1200°C)下通入氧气或水蒸气,生成二氧化硅(SiO?)绝缘层,厚度可控在几纳米到微米级。

应用:作为晶体管栅极介质、隔离层或掩膜。

3. 光刻(Lithography)

涂胶:旋转涂布光刻胶(正胶/负胶),厚度约0.1-2μm。

曝光:使用紫外光(DUV,波长193nm)或极紫外光(EUV,13.5nm)通过掩膜版(Reticle)转移图形,先进制程需多重曝光。

显影:溶解曝光区域(正胶)或未曝光区域(负胶),形成三维图形。

4. 刻蚀(Etching)

湿法刻蚀:使用HF等化学溶液,各向同性,精度较低。

干法刻蚀(等离子体刻蚀):通过离子轰击实现各向异性,精度达纳米级(如反应离子刻蚀RIE)。

5. 掺杂(Doping)

扩散法:高温(>1000°C)下使磷、硼等杂质扩散入硅,形成PN结。

离子注入:高能离子(1-200keV)轰击硅表面,掺杂深度和浓度精准可控(如晶体管源/漏区)。

6. 薄膜沉积

CVD(化学气相沉积):

LPCVD(低压CVD):沉积多晶硅、氮化硅。

PECVD(等离子体增强CVD):低温沉积绝缘层。

PVD(物理气相沉积):溅射法沉积金属(Al、Cu)或阻挡层(TaN/TiN)。

ALD(原子层沉积):逐层生长,用于高介电材料(HfO?)等纳米级薄膜。

7. 金属互连(Back End of Line, BEOL)

Damascene工艺(主流铜互连):

刻蚀介质层形成沟槽。

沉积Ta/TaN阻挡层(防铜扩散)。

电镀铜填充沟槽。

CMP去除多余铜,实现平面化。

多层堆叠:先进芯片含10-15层金属,线宽缩至几纳米。

8. 测试与封装

晶圆测试:用探针卡检测电路功能,标记缺陷芯片。

切割:激光或金刚石刀将晶圆分割为单个芯片(Die)。

封装:

引线键合:金线连接芯片与引脚。

倒装焊(Flip-Chip):锡球直接焊接至基板,提升密度。

先进封装:2.5D/3D封装(TSV硅通孔)、Chiplet异构集成。

关键工艺节点与技术趋势

节点演进:从28nm平面晶体管到FinFET(16/7/5nm),再到GAAFET(3nm及以下)。

EUV光刻:ASML EUV光刻机(13.5nm光源)实现单次曝光7nm以下图形。

新材料:钴互连(替代铜)、Low-k介质(降低寄生电容)。

挑战:量子隧穿效应(栅极氧化层<1nm)、热管理、制造成本(3nm晶圆厂投资超200亿美元)。

-

集成电路

+关注

关注

5430文章

12139浏览量

368970 -

晶圆

+关注

关注

53文章

5181浏览量

130127 -

半导体芯片

+关注

关注

61文章

934浏览量

71503

发布评论请先 登录

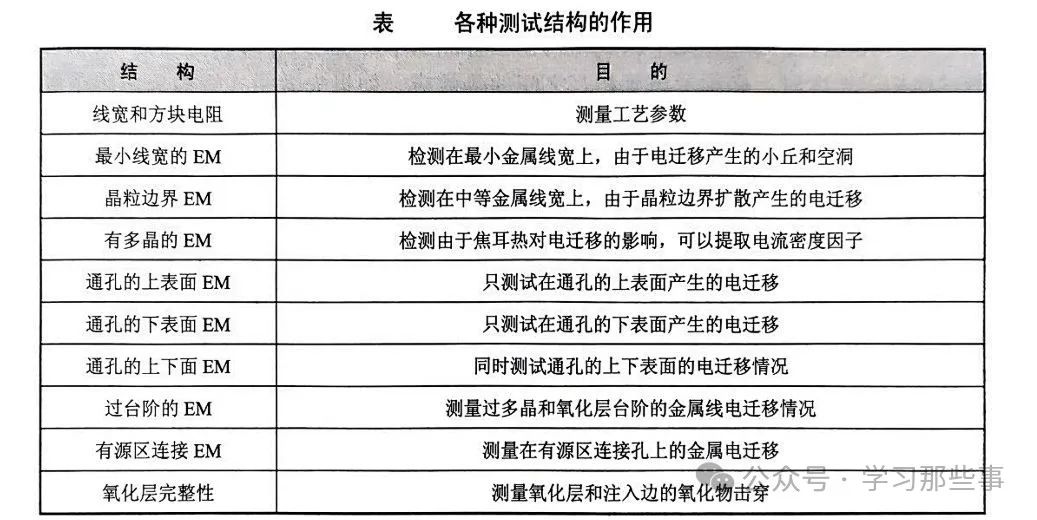

提供半导体工艺可靠性测试-WLR晶圆可靠性测试

基于集成电路的高可靠性电源设计

芯片,集成电路,半导体含义

如何实现高可靠性电源的半导体解决方案

集成电路与半导体

半导体集成电路的可靠性设计

半导体集成电路可靠性测试及数据处理

集成电路可靠性检查的最佳实践方案

半导体芯片集成电路工艺及可靠性概述

半导体芯片集成电路工艺及可靠性概述

评论