概述

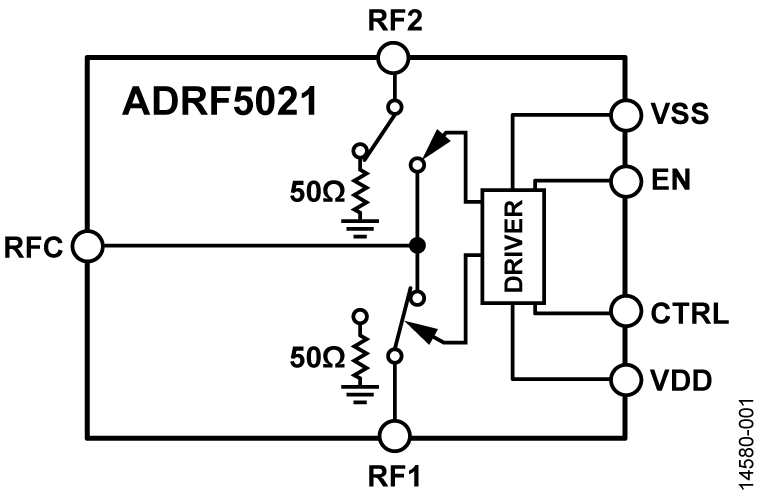

ADRF5021是一款通用型单刀双掷(SPDT)开关,采用硅工艺制造。它采用3 mm × 3 mm、20引脚基板栅格阵列(LGA)封装,在9 kHz至30 GHz频率范围内提供高隔离度和低插入损耗。

该宽带开关采用+3.3 V和?2.5 V双电源电压供电,提供CMOS/LVTTL逻辑兼容控制。

数据表:*附件:ADRF5021 9kHz至30GHz、硅SPDT开关技术手册.pdf

应用

- 测试仪器仪表

- 微波无线电和甚小孔径终端(VSAT)

- 军用无线电、雷达、电子对抗(ECM)

- 宽带电信系统

特性 - 超宽带频率范围:9 kHz至30 GHz

- 非反射式50 Ω设计

- 低插入损耗:2.0 dB至30 GHz

- 高隔离度:60 dB至30 GHz

- 高输入线性度

- 1 dB功率压缩(P1dB):28 dBm(典型值)

- 三阶交调截点(IP3):52 dBm(典型值)

- 高功率处理

- 24 dBm(通过路径)

- 24 dBm(端接路径)

- ESD灵敏度:1级、1 kV人体模型(HBM)

- 20引脚、3 mm × 3 mm基板栅格阵列封装

- 无低频杂散

- 射频(RF)建立时间(高达最终RF输出的0.1 dB):6.2 μs

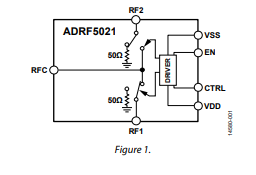

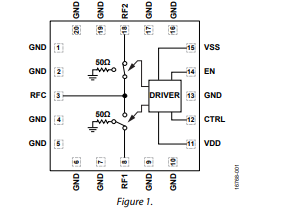

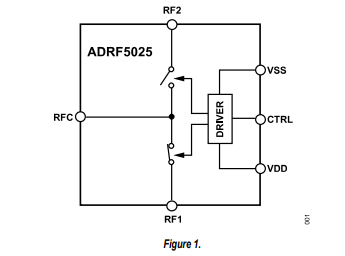

框图

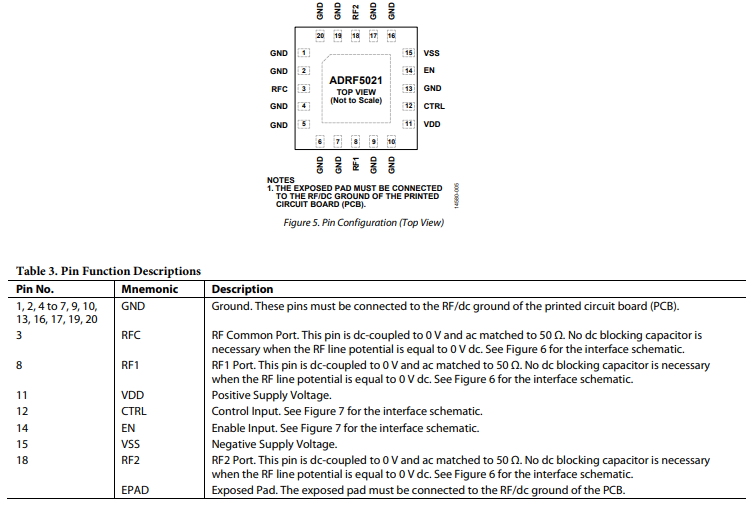

引脚配置

接口示意图

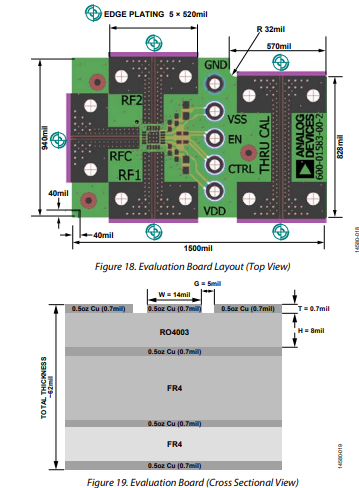

图18和图19显示了评估板的俯视图和横截面图,该评估板采用4层结构,铜层厚度为0.5盎司(0.7密耳),各铜层之间采用电介质材料。

所有RF和dc走线都布设在顶层铜层上,内层和底层是接地层,为RF传输线路提供坚实的接地。顶部介电材料是8密耳罗杰斯罗4003,提供良好的高频性能。中间和底部介电材料是FR-4型材料,以实现62密耳的总板厚。RF传输线路采用共面波导(CPWG)模型设计,宽度为14密耳,接地间距为5密耳,特性阻抗为50ω。为了实现良好的RF和热接地,尽可能多的镀通孔应布置在传输线路周围和封装裸露焊盘下方。

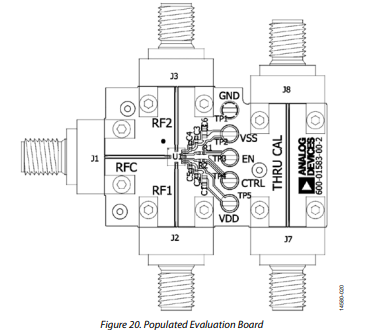

图20显示了实际ADRF5021评估板的元件布局。两个电源端口连接到VDD和VSS测试点,TP5和TP2,接地参考连接到TP1的GND测试点。在每条电源走线上,使用一个100 pF旁路电容,未填充的元件位置可用于施加额外的旁路电容。

-

开关

+关注

关注

19文章

3287浏览量

95893 -

SPDT

+关注

关注

0文章

133浏览量

27089 -

引脚

+关注

关注

16文章

1837浏览量

53477

发布评论请先 登录

ADRF5021 9 kHz至30 GHz、硅SPDT开关

ADRF5021 9 kHz to 30 GHz, Silicon SPDT Switch

ADRF5019:硅,SPDT开关,无反射,100 MHz至13 GHz数据表

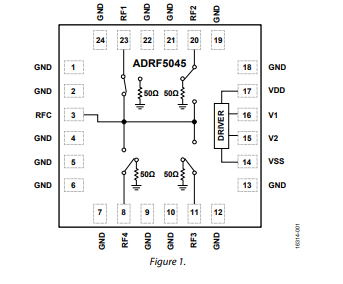

ADRF5045 9kHz至30GHz硅SP4T开关技术手册

ADRF5021 9kHz至30GHz、硅SPDT开关技术手册

ADRF5021 9kHz至30GHz、硅SPDT开关技术手册

评论