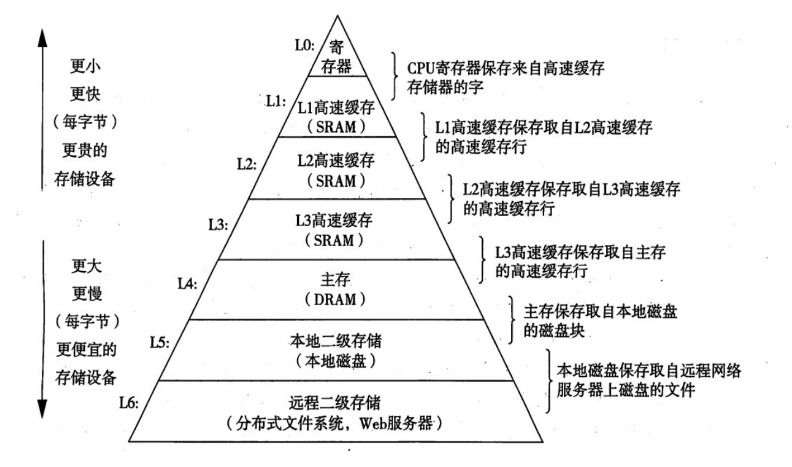

动态随机存取存储器(DRAM)是现代计算机系统中不可或缺的核心组件,广泛应用于个人计算机、服务器、移动设备及高性能计算领域。本文将探讨DRAM的基本工作原理、存储单元结构及制造工艺演进,并分析未来发展趋势。

DRAM 介绍

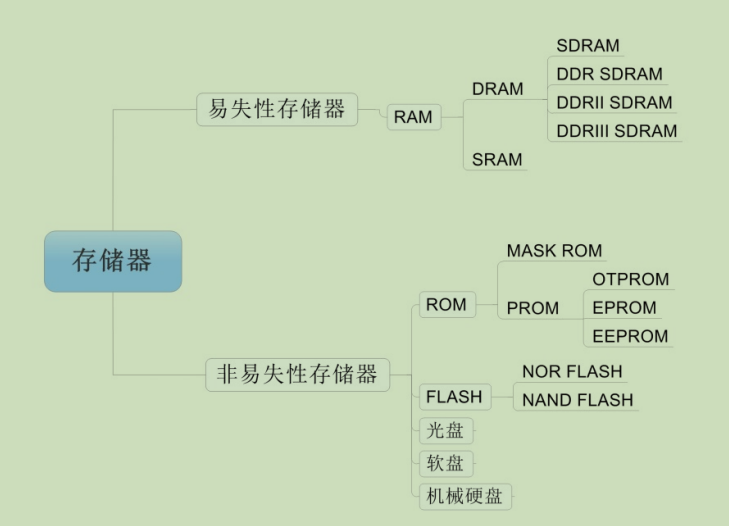

动态随机存取存储器(Dynamic Random Access Memory,缩写为 DRAM)是一种易失性存储设备。这意味着,一旦停止供电,它所存储的数据就会丢失。DRAM 的工作原理依赖于电容器来保存电荷,以此记录数据。然而,电容器中的电荷会随着时间逐渐泄漏。为了确保数据的完整性,需要在电荷完全消失之前进行刷新操作。这个刷新过程一直持续到下一次数据写入或者计算机完全断电。由于每次数据读写操作都伴随着电荷刷新,并且每隔几毫秒就需要借助独立电源对存储单元进行充电,因此被称为 “动态” 存储器。基于此,DRAM 的设计需要保证数据能够被定期读取。由于 DRAM 通常被安置在靠近中央处理器(CPU)的位置,其性能对于整个计算机系统的运行效率起着关键作用。与计算机闪存器件(NAND)不同,DRAM 的技术创新主要围绕降低每单元成本展开,同时在性能方面,快速的读写切换速度也是重点考量因素。

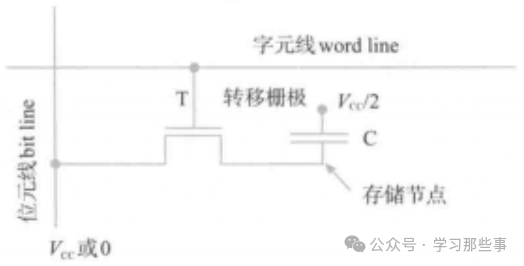

DRAM的存储单元设计相当简洁,核心由一个晶体管搭配一个存储电容构成,这一组合被业界简称为1T/1C架构(即一个晶体管与一个电容器)。尽管后续涌现了多种创新的DRAM存储单元设计,但从组件数目及电路复杂度考量,它们均未能超越1T/1C架构的简洁性。因此,即便是容量介于64MB至464MB之间的DRAM,仍广泛沿用了这一基础架构。一个完备的DRAM单元主要包含三大组件:负责数据保存的电容、用于激活单元的字线,以及执行数据读写操作的位线。1T/1C架构正是集成了这三项关键组件的最简化形式,其等效电路示意图可参考下图。目前,多数DRAM存储单元采用的是NMOS型晶体管。在构成电容的两个极板中,主动施加电压的极板被称为单元极板(CP),而另一个用于实际数据存储的极板则命名为存储节点(SN)。此外,存储单元内的MOS晶体管在特定语境下被称作转移栅极。简而言之,1T/1C架构由一个MOS晶体管及其源极直接相连的电容C共同构成。

1T/1C的DRAM单元原理

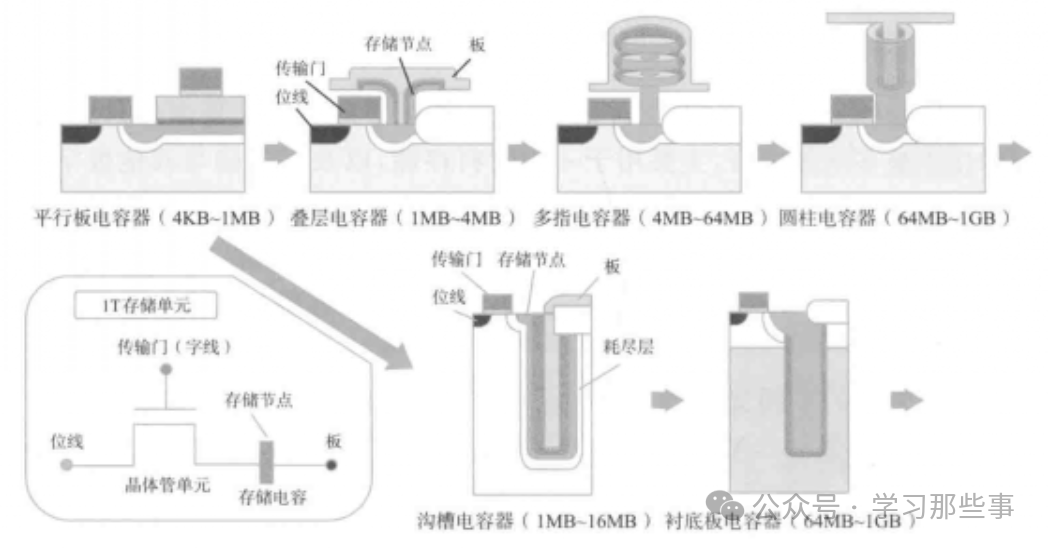

尽管1T/1C的基础架构维持不变,DRAM的制造技术却已历经数代革新,如下图所示。最初,DRAM单元电容采用的是平板式设计,但随着技术迭代,已演进为现今的三维电容单元,即3D单元,主要包括堆叠式和沟槽式两大类。沟槽式电容技术(TRC)的制作流程大致为:首先构造第一层极板,随后沉积介电层,再形成第二层极板,最终在沟槽顶端嵌入连接线路,以实现与晶体管单元的电气连接。简而言之,沟槽式技术遵循先电容后晶体管的制造顺序。继沟槽式技术之后,衬底板式技术应运而生。相比之下,堆叠式电容技术(STC)则采取相反的步骤,即先完成晶体管的制作,随后再构建电容。

DRAM工艺技术变化

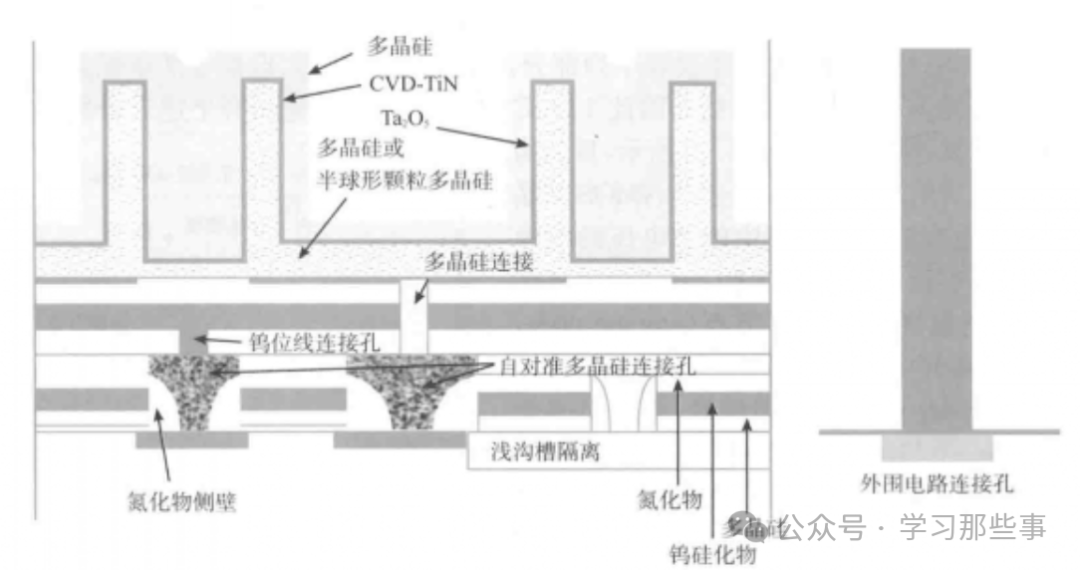

堆叠式工艺主要有两种类型:电容在位线下(Capacitor Under Bitline,简称 CUB)和电容在位线上(Capacitor Over Bitline,简称 COB) 。现代 DRAM 的制造工艺与标准的 CMOS 工艺完全兼容,常见的做法是在 CMOS 基础工艺上,通过添加深槽电容和堆栈电容的制作流程,来构建 DRAM 单元。

COB堆叠式工艺DRAM横截面

DRAM 的制造工艺

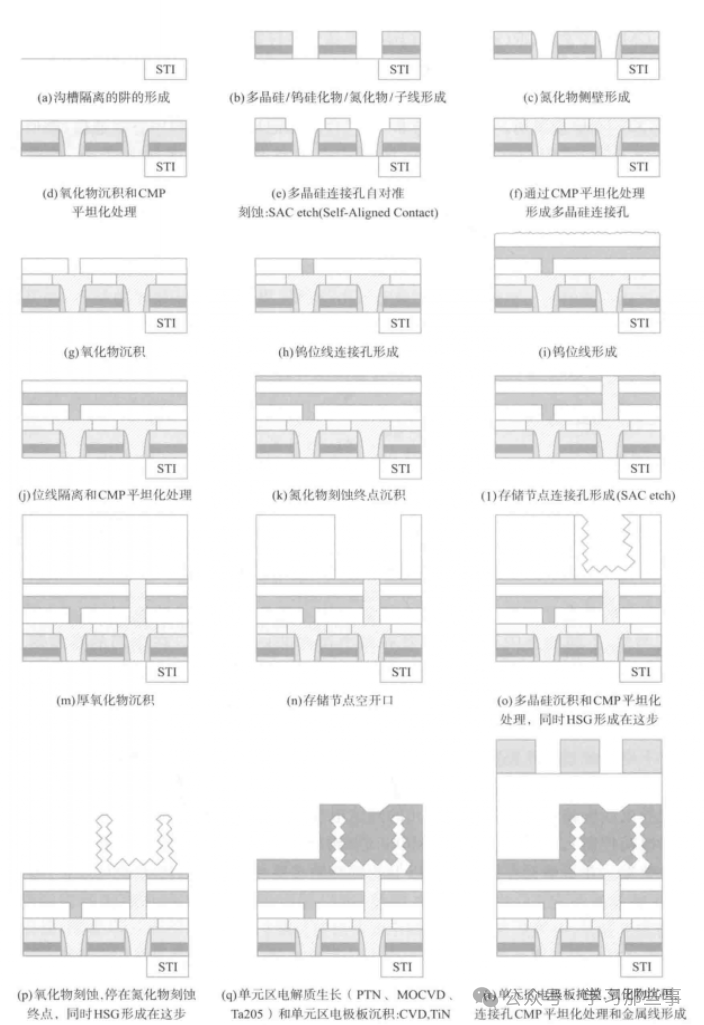

考虑到篇幅限制,这里不会详细介绍所有的 DRAM 制造工艺。下图展示的是 COB 堆叠式 DRAM 单元的具体制作流程。

COB堆叠式DRAM单元的制造工艺

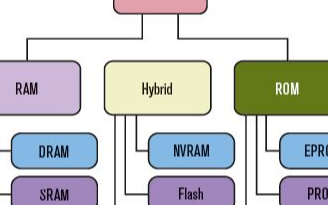

非易失性存储器 -- 快闪存储器

快闪存储器(Flash Memory),通常简称为闪存,是一种电子式的可擦除可编程只读存储器。它的特点是可以在设备运行过程中进行多次数据擦除和写入操作。闪存主要用于一般的数据存储,以及在计算机和其他数字设备之间进行数据交换和传输。作为非易失性固态存储技术中最重要、应用最广泛的一种,闪存常见于固态硬盘、笔记本电脑、数字随身听、数码相机、游戏主机、手机等各种电子设备中。闪存属于非易失性存储器(Non - Volatile Memory,简称 NVM),即当外部电源断开后,其存储的数据不会丢失。

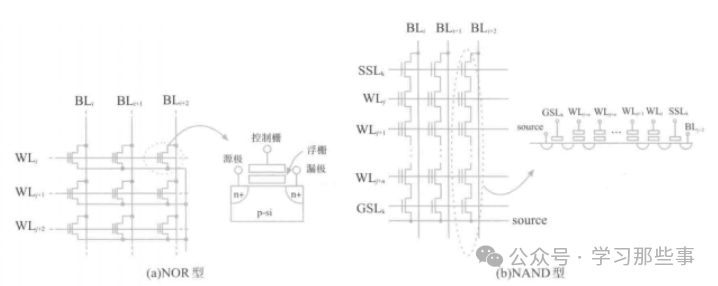

根据内部架构的不同,闪存可以分为 NOR(或非)和 NAND(与非)两种类型,如下图所示。NOR 型和 NAND 型闪存之间存在两个主要区别:一是连接单个存储单元的方式不同;二是数据读写的接口不同(NOR 型闪存支持随机存取,而 NAND 型闪存只支持页访问)。NOR 型闪存内部的存储单元以并行方式连接到比特线,这使得可以对单个存储单元进行独立的读取和编程操作。这种并行连接方式类似于 CMOS 工艺中 NOR 逻辑门的晶体管连接方式。从 NOR 型闪存中读取数据的方式与从 RAM 中读取数据相似,只需提供数据的地址,数据总线就能准确地输出相应的数据。基于这些特性,大多数微处理器可以将 NOR 型闪存作为原地执行(Execute In Place,简称 XIP)存储器使用。NAND 型闪存内部的存储单元采用顺序连接方式,类似于 NAND 逻辑门。这种连接方式占用的空间比并行连接方式小,从而降低了 NAND 型闪存的生产成本。NAND 型闪存架构由东芝公司于 1989 年发布,其访问方式类似于硬盘、存储卡等块存储设备,每个存储块由多个页面组成。

闪存结构

闪存的基本存储单元建立在浮栅金属氧化物半导体场效应晶体管之上,这种晶体管与常规的MOSFET结构相似,但存在一个显著差异:闪存晶体管配备了两个栅极,而非单一栅极。顶部的栅极被命名为控制栅(CG),其功能与MOSFET中的栅极作用一致。控制栅之下,存在一个被氧化物层隔离的浮栅(FG),它置于控制栅与MOSFET沟道间。浮栅在电气上处于孤立状态,一旦电子进入其中便会被俘获,这些电荷在常态下能稳定保存多年。当浮栅捕获电荷时,会部分抵消控制栅产生的电场效应,进而调整存储单元的阈值电压。数据读取时,通过控制栅施加电压,MOSFET沟道的导通状态由存储单元的阈值电压决定(该电压受浮栅电荷量调控),电流流经沟道,以二进制形式解读并恢复存储的信息。在多层单元(MLC)技术中,每个单元能存储超过1比特的数据,通过精确测量浮栅电荷的电位,依据感应电流的强度(而非单纯的存在与否)来读取数据。

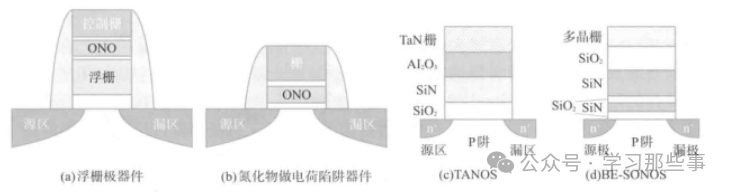

常见的闪存存储单元工艺类型如下图所示,包括浮栅极器件、氮化物电荷陷阱器件、TANOS(TaN - Al0, - SiN - oxide - Si)和 BE - SONOS(Bandgap Engineered Silicon - Oxide - Nitride - Oxide - Silicon,即能带工程的 SONOS 结构) 。

常见的闪存存储单元工艺种类

下面以 BE - SONOS 为例,简要介绍闪存存储单元的制作工艺。与其他现代 NVM 技术相比,BE - SONOS 工艺的优势在于它与 CMOS 逻辑工艺完全兼容。在标准 CMOS 工艺的基础上,SONOS 技术只需额外增加 3 - 4 层光刻步骤。在将 SONOS 工艺集成到标准 CMOS 工艺中时,不会改变标准 CMOS 器件的特性,确保了工艺的兼容性。SONOS 在 CMOS 标准逻辑工艺中额外添加的步骤包括:①氧化前清洗;②多晶沉积和掺杂;③掩模和图案化;④氧化物去除。这些步骤在 N 阱和 P 阱工艺之后、栅极工艺之前进行。

-

CMOS

+关注

关注

58文章

6035浏览量

239168 -

DRAM

+关注

关注

40文章

2351浏览量

185840 -

存储器

+关注

关注

38文章

7654浏览量

167852

原文标题:常见存储器工艺简介

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

光盘存储器的类型

半导体存储器有哪些类型

只读存储器有哪些类型及相变存储器的详细介绍

常见存储器的区别分析

存储器工艺概览:常见类型介绍

存储器工艺概览:常见类型介绍

评论