本文介绍了芯片里的介质及其性能。

介电常数k概述

在介质薄膜的沉积过程中,除了薄膜质量如均匀性、致密性、间隙填充及台阶覆盖能力备受关注外,介质材料的介电常数k也成为了焦点,因其直接关联到芯片的性能表现。下面将深入探讨介电常数k的重要性,并逐一阐述低k、超低k及高k材料的发展与应用。

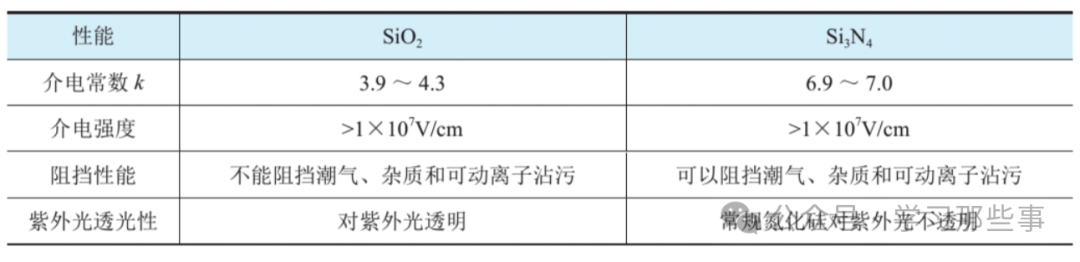

导电材料的介电常数,是衡量材料在电场作用下存储电能效率的关键指标,它反映了材料作为电容隔离层的效能。在集成电路制造领域,介电常数通常以k值表示,其中空气的k值最低,为1。不同制备工艺得到的绝缘薄膜,其k值会有轻微差异,例如热生长二氧化硅的k值约为3.9,而等离子体增强化学气相沉积(PECVD)二氧化硅的k值则在4.1至4.3之间。

相较于二氧化硅,另一种常见绝缘介质氮化硅的介电常数较高。尽管氮化硅在阻挡可动离子污染及防止硼磷硅酸盐玻璃(BPSG)中的硼、磷扩散至晶体管源、漏区方面表现出色,但由于其较高的介电常数(6.9至7.0),会增加RC延迟,从而降低芯片速度。因此,在实际应用中,常采用折中方案:先沉积一层较薄的氮化硅,主体介质材料仍以二氧化硅为主。

二氧化硅与氮化硅的性能对比参见下表。芯片性能的一个重要衡量标准是信号传输速度。随着芯片微型化需求的增长,金属互连的线宽不断缩小,导致传输信号导线的电阻R增大。同时,导线间距的减小也引发了寄生电容C的增加,进而加剧了RC信号延迟,降低了芯片速度。RC信号延迟,亦称互连延迟,已成为制约芯片性能的关键因素之一。

从本质上看,互连尺寸的减小带来了寄生电阻和电容效应的增强,从而导致了信号延迟的增加。然而,这与晶体管的发展趋势相悖。随着栅长的缩短,晶体管的延迟减小,速度提升。因此,我们不能仅凭互连延迟的增加就反对线宽的减小。因为线宽的减小不仅意味着晶体管速度的提升,还使得芯片更加轻便,便于携带。

既然线宽的减小是必然趋势,那么如何抵消RC信号延迟的增加呢?一方面,采用电阻率更低的铜替代传统的铝材料,以降低导线电阻R。另一方面,由于电容C与绝缘介质的k值成正比,因此寻找低k材料以降低寄生电容C成为了关键。低k绝缘介质的应用有助于减小芯片的总互连电容,降低RC信号延迟,从而提升芯片性能。

低k材料

降低绝缘介质的介电常数k值,能有效减少相邻导线间的电耦合损耗。这是因为低k介质存储电荷较少,且充电时间更短,从而提升了金属导线的传导效率。特别是在现代晶体管中,金属线间距极小的纳米器件中,低k(low-k)材料作为层间介质(ILD)显得尤为关键。

传统的二氧化硅绝缘体介电常数在3.9至4.3之间。而新型绝缘体则拥有更低的介电常数,它们通过减少互连电容并防止高性能逻辑电路中金属线之间的串扰,显著提升了芯片的运行速度。通常,我们将k值低于3.9的材料定义为低k材料。采用低k材料替代传统的二氧化硅,已成为集成电路工艺发展的必然趋势。

对低k材料的性能要求涵盖多个方面:

①电学性能:要求具有低介电常数、低介电损耗、低漏电流以及高可靠性。

②机械性能:需具备低应力、良好的黏附性、低收缩性、优异的硬度以及抗开裂能力。

③ 工艺性能:应易于图形制作,具备良好的间隙填充能力、低针孔密度、少颗粒污染以及易于平坦化。

④ 热学性能:要求具有高导热性、良好的热稳定性以及低的热扩散系数。

⑤ 化学性能:需具备低杂质含量、低湿气吸收性、易于干法刻蚀、耐酸碱腐蚀、无侵蚀性以及可接受的存储寿命。

⑥ 金属化搭配性能:要求具有低的接触电阻、低应力、低电子迁移率、表面光滑以及与金属材料的良好兼容性。

在特大规模集成电路(ULSI)互连中,曾考虑的低k值ILD材料包括氟硅玻璃(FSG,k值为3.4至4.1)、纳米多孔硅(k值为1.3至2.5)、氢硅倍半环氧乙烷(HSO,k值为2.9)、非晶氟化碳(a-C:F,k值为2.8)以及聚Z醚(PAE,k值为2.6至2.8)等。其中,FSG作为典型代表,被广泛应用于深亚微米CMOS集成电路互连线间的介质隔离。

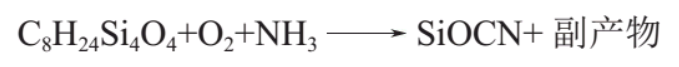

业界广泛采用的黑金刚石(black diamond,SiCON)材料,其k值范围在2.7至3.0之间,能够满足45nm节点的技术要求。八甲基环四硅氧烷(OMCTS)是沉积SiCON的前驱体,其分子式为CH3SiO,常温下呈液态,沸点约为175℃。通过载气He将OMCTS输入反应腔中,在等离子体作用下发生化学反应,生成SiCON。该反应过程可简要表示为:

超低k材料

随着集成电路特征尺寸的持续缩减,为了更有效地降低金属间的寄生电容C并减少RC延迟,超低k材料(ultralow-k, ULK)的研发成为了业界关注的热点。然而,超低k材料的研发工作给化学家、物理学家、材料科学家以及集成电路工程师们带来了前所未有的挑战。因为当材料的k值降低时,其力学性能和热稳定性往往会受到影响。在此背景下,多孔超低k介质成为了主流的研究方向。

多孔介质是一种内部含有空气间隙的介质材料,其沉积方法主要包括旋涂技术和化学气相沉积技术。通常,我们将介电常数小于或等于2.5的材料定义为超低k材料。目前,业界广泛采用的多孔SiCOH超低k材料是通过等离子体增强化学气相沉积(PECVD)技术制备的,由硅、碳、氧、氢等元素组成的掺碳非晶玻璃材料。在特定的等离子体条件下,科研实验室已成功制备出平均孔径小于2.5纳米、孔隙率高达30%、k值低至1.95的超低k纳米多孔介质薄膜。

除了具有极低的介电常数外,SiCOH薄膜还展现出了卓越的电学性能,其漏电流极低且耐压性能优异。此外,SiCOH薄膜在力学性能方面也表现出色,具有可接受的硬度和弹性模量,并具有良好的防开裂性能。更重要的是,SiCOH薄膜的热膨胀系数较低,且与铜的热膨胀系数相近,这有助于实现与铜的良好集成。

目前,产业界量产的SiCOH薄膜其k值大约在2.47左右。其制备工艺流程大致如下:首先,利用二甲基乙氧基硅烷(DEMS)和氧化环己烯(CHO)在等离子体作用下沉积一层有机硅玻璃薄膜;随后,通过紫外光辐照处理,排除有机气体;最后,在晶圆表面形成多孔的SiCOH介质薄膜。

高k材料

在探索特殊k值材料的征程中,另一个极具挑战性的方向,便是研发高k材料,以此来取代MOS结构中的栅氧材料——二氧化硅 。

在集成电路技术持续演进的历程中,工艺层面的每一次革新都蕴含着深刻的意义与挑战。随着时代的发展,对于集成电路性能的要求愈发严苛,为了实现更高的集成度,在有限的芯片空间内容纳更多的晶体管,同时达成降低器件功耗以及提升整体性能的目标,一系列关键参数的调整成为必然趋势。其中,集成电路的特征尺寸不断按照一定比例缩小,工作电压也随之持续降低。在这一复杂的变革过程中,抑制短沟道效应成为了一项至关重要的任务。为了有效达成这一目标,除了逐步增加沟道掺杂浓度,降低源漏的结深之外,栅氧厚度的不断降低也成为了关键举措。这是因为栅氧厚度的减小,能够在微观层面上提高栅极电容,进而增强栅极对沟道的精准控制能力,就如同为电路的运行提供了更为精细的调控阀门。

当栅氧化硅层的厚度大于4nm时,它在集成电路的运行环境中堪称理想的绝缘体。尤其是与多晶硅栅搭配使用时,二者相互协作,能够保障电路的稳定运行,为早期集成电路的发展奠定了坚实的基础。然而,随着技术的不断进步,当栅氧厚度持续降低,一旦小于3nm,情况便发生了显著的变化。此时,在微观世界中,量子隧穿效应开始在栅极与衬底间崭露头角。具体来说,衬底硅中的电子会以一种奇妙的量子形式,穿越原本被视为阻隔的栅氧,进入到栅极之中,这一过程直接导致了栅极漏电流的形成。更为棘手的是,这个漏电流会随着栅氧厚度的减小呈现出指数级增长的态势。经研究发现,栅氧每减小0.2nm,隧穿电流就会增大10倍。栅极漏电流的大幅增加,不仅会造成集成电路功耗的显著上升,浪费宝贵的能源资源,还会引发器件发热的问题,进而对器件的可靠性产生严重影响,如同在精密的电路系统中埋下了一颗不稳定的“炸弹”。

当晶体管内部的特征尺寸迈入0.18um节点时,栅的厚度已经小于3nm,这一关键参数的变化促使集成电路制造企业不得不寻求新的解决方案。在这一背景下,氮氧化硅(SiON)开始进入人们的视野,并逐渐被采用来代替纯SiO?作为栅介质层。这种替代方法巧妙地利用了SiO?作为主要栅介质的基础优势,通过在SiO?膜中精确掺入适量的氮,使其转变为结构更为致密的SiON,从而成功提高了栅介质的介电常数。从数据对比来看,传统栅介质SiO?的k值为3.9,而纯SiN的k值则可达到7。基于这一特性,通过精准地改变掺杂氮的比例,就能够实现对SiON栅介质介电常数的有效调控。同时,该方法仍然将SiO?作为栅介质的主体,这使得它与前期的集成电路技术之间保持了良好的连续性和兼容性。在实际应用中,这种兼容性能够有效降低技术升级的成本和风险,使得新工艺能够较为顺利地融入到已有的生产体系中。因此,在这一特定的技术发展阶段,SiON受到了广泛的欢迎和应用。其受欢迎的原因主要体现在以下几个关键方面:首先,SiON具有较高的k值,这一特性使得在相同等效栅电容的情况下,允许有更厚的物理氧化层存在。更厚的物理氧化层能够在一定程度上增强电路的稳定性和可靠性,为电路的正常运行提供更为坚实的保障;其次,SiON具备较高的电子绝缘特性,在相同厚度的情况下,它的栅极漏电流大大降低。这对于降低集成电路的功耗、提高能源利用效率具有重要意义;最后,SiON中氮原子的掺入还能有效地抑制PMOS中多晶硅栅极掺杂的硼离子在栅介质中的扩散。硼离子的扩散问题如果得不到有效控制,将会穿过介质层到达衬底,进而影响器件的阈值电压,而SiON的这一特性成功地避免了这一潜在风险。

随着技术的不断推进,特征尺寸进一步缩小到90nm及以下,此时栅氧的厚度也减小到2nm左右。在这一更为精细的尺度下,栅极漏电流和硼离子扩散的问题变得愈发严重,如同技术发展道路上的两座险峻高山,阻碍着集成电路性能的进一步提升。为了克服这些难题,就要求SiON中氮的含量不断提高。而要实现这一目标,就需要采用更先进的等离子氮化工艺来沉积SiON材料。这种先进工艺不仅能够提高栅氧中氮的含量,还能够对氮的分布进行精确控制,使氮主要分布在栅介质的上表面,远离SiO?和沟道界面。这样的分布方式有助于改善SiO?和Si衬底的界面特性,就像在两个关键部件之间搭建了一座稳固且高效的桥梁,保障了电子在其中的顺畅传输。

当特征尺寸进入到45nm节点以后,栅的厚度已经小于2nm,此时由SiON和多晶硅栅组成的搭档在应对极高的栅极漏电流、急剧增加的功耗以及栅介质层完整性和可靠性问题时,已经显得力不从心。在这种技术困境下,2007年,Intel公司宣布在45nm节点采用全新的高k栅介质氧化铪(HfO?)来替代传统的SiO?,同时利用金属栅代替多晶硅栅,这一创新性的工艺被称为HKMG(High - k,Metal Gate)工艺。这一工艺的出现,如同在黑暗中点亮了一盏明灯,为集成电路技术的发展开辟了新的道路。

实际上,在高k材料领域,研究人员长期以来一直在进行深入的基础研究。在这一漫长而艰辛的探索过程中,他们发现了众多具有高k值的材料,如SiN、Al?O?、Ta?O?、TiO?、TaO、HfO?等。然而,这些材料在实际应用中总是存在各种各样的局限性。它们往往只能满足某一方面的特定要求,例如在介电常数、绝缘性能或者热稳定性等方面表现出色,但在其他关键性能指标上却存在不足。或者,这些材料在与其他工艺的兼容性方面存在严重问题,无法顺利地融入到现有的集成电路制造体系中。正是由于这些原因,尽管这些材料在理论研究中展现出了一定的潜力,但在实际应用中却面临着重重困难。直到工艺发展到特定阶段,传统的以氧化硅为主的介质材料在面对日益严苛的技术要求时,已经无法满足集成电路进一步发展的需求,人们才不得不将目光投向那些曾经被视为存在诸多问题的高k材料。

HfO?作为一种备受关注的高k材料,其介电常数可达25左右,这一数值相较于传统的栅介质材料具有明显的优势。然而,它也并非完美无缺,其结晶温度较低,低于600℃。这一特性在实际应用中带来了一个严重的问题,即后续的高温工艺会使其结晶化,一旦发生结晶化,栅极漏电流就会急剧增加,从而对集成电路的性能产生负面影响。幸运的是,研究人员通过不断的实验和探索,发现可以通过向HfO?中掺入Si、N的方法来提高其结晶温度。经过这种掺杂处理后,HfO?的结晶温度能够提高到1000℃,这在很大程度上解决了其在高温工艺中的稳定性问题。但令人遗憾的是,掺杂也带来了另一个问题,即HfO?掺杂后得到的HfSiON介电常数会降低。虽然HfSiON的介电常数会随着N含量的增加而增大,但即便在N含量达到最大值时,其介电常数也只能达到16,这与未掺杂的HfO?相比,存在一定的差距。

为了使HfO?和HfSiON能够更好地与当前的硅工艺相兼容,研究人员通过改变工艺流程和改用金属栅极等一系列创新举措,成功地解决了这一难题。目前,HfO?和HfSiON已经凭借其出色的性能,成为了最合适的栅极高k介质材料。它们之所以能够脱颖而出,主要基于以下两点关键优势:其一,HfO?和HfSiON具有很高的电子绝缘特性,这一特性使得它们能够有效地阻止电子的泄漏,保障了集成电路的正常运行;其二,HfO?和HfSiON的k值范围是15 - 25,比SiON的k值4 - 7要大得多。在相同等效氧化层厚度下,HfO?和HfSiON的厚度可以是SiON的3 - 6倍多。这一显著的差异将显著减小量子隧穿效应,从而有效改善栅极漏电流及其引起的功耗问题,为集成电路的高性能运行提供了有力的支持。

在金属栅极(metal gate)制备时,根据不同的MOS类型,可以采用不同的金属材料。对于NMOS而言,其金属栅极材料可选用Ta - AlN,这种材料能够在NMOS的工作环境中发挥出良好的性能;而对于PMOS,其金属栅极材料则可选用TaN,TaN在PMOS中能够有效地实现其功能,满足电路对PMOS的性能要求。

高k介电材料的应用领域并不仅限于取代超薄栅氧化硅,它在半导体存储器领域也有着重要的应用价值。以动态随机存储器(DRAM)为例,高k介电材料作为其中电容的介质材料,承担着存储信息的关键任务。对于DRAM器件而言,要确保存储信息的电荷在刷新时能够正常恢复,就必须要有一定的电容容量作为保障。为了提高DRAM的容量,不断减小器件的特征尺寸成为了必然选择。然而,特征尺寸的减小意味着电容面积也会随之减小。在电介质厚度不变的情况下,根据电容公式,为了保持同样的电容大小,就必须提高介质的介电常数,以此来抵消面积减小带来的影响。例如,可以采用基于二氧化锆的高k材料,其介电常数在26左右,具有较高的性能优势。在制备这种材料时,可采用原子层沉积(atomic layer deposition,ALD)方法。ALD也被称为原子层化学气相沉积(ALCVD)。原子层沉积是一种将物质以单原子膜形式一层一层地镀在衬底表面的独特工艺。它与普通CVD虽然有相似之处,但在ALD中,新一层原子膜的化学反应是直接与之前一层相关联的。这种独特的工艺特点使得每次反应只沉积一层原子,从而能够实现对材料生长的精确控制,为制备高质量的高k介电材料提供了有力的技术支持。

-

芯片

+关注

关注

460文章

52616浏览量

442711 -

介质

+关注

关注

0文章

142浏览量

18886

原文标题:芯片里的介质及其性能介绍

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体芯片中的互连层次

CI24R1超低成本高性能2.4GHz GFSK无线收发芯片中文手册

芯知识|WT588系列语音芯片BUSY引脚功能解析与设计指南

芯知识|WT3000T8语音合成芯片:功能解析与应用指南

玻璃中介层:颠覆传统封装,解锁高性能芯片 “新密码”

芯片制造的关键一环:介质层制备工艺全解析

单片机语音芯片中的SPI Flash探秘及其分类详解

详解金属互连中介质层

芯片中介质及其性能解析

芯片中介质及其性能解析

评论