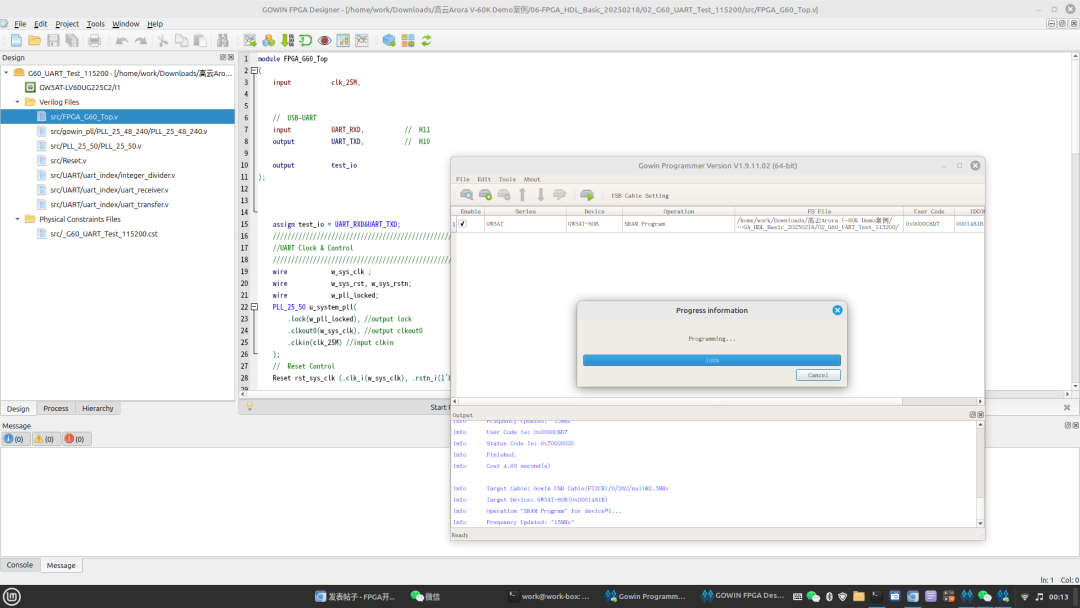

如图1.9所示。这个流程图是一个相对比较高等级的FPGA开发流程,从项目的提上议程开始,设计者需要进行FPGA功能的需求分析,然后进行模块的划分,比较复杂和庞大的设计,则会通过模块划分把工作交给一个团队的多人协作完成。各个模块的具体任务和功能划分完毕(通常各个模块间的通信和接口方式也同时被确定),则可以着手进行详细设计,包括代码输入、综合优化、实现(映射和布局布线)。

为了保证设计达到预期要求,各种设计的约束输入以及仿真验证也穿插其间。在EDA工具上验证无误后,则可以生成下载配置文件烧录到实际器件中进行板级的调试工作。从图中的箭头示意不难看出,设计的迭代性是FPGA开发过程中的一个重要特点,这就要求设计者从一开始就要非常认真细致,否则后续的很多工作量可能就是不断的返工。

图1.7 FPGA开发流程

当然了,对于没有实际工程经验的初学者而言,这个流程图可能不是那么容易理解。不过没有关系,我们会简化这个过程,从实际操作角度,以一个比较简化的顺序的方式来理解这个流程。如图1.8所示,从大的方面来看,FPGA开发流程不过是三个阶段,第一个阶段是概念阶段,或者也可以称之为架构阶段,这个阶段的任务是项目前期的立项准备,如需求的定义和分析、各个设计模块的划分;第二个阶段是设计实现阶段,这个阶段包括编写RTL代码、并对其进行初步的功能验证、逻辑综合和布局布线、时序验证,这一阶段是详细设计阶段;第三个阶段是FPGA器件实现,除了器件烧录和板级调试外,其实这个阶段也应该包括第二个阶段的布局布线和时序验证,因为这两个步骤都是和FPGA器件紧密相关的。我们这么粗略的三个阶段划分并没有把FPGA整个设计流程完全的孤立开来,恰恰相反,从我们的阶段划分中,我们也看到FPGA设计的各个环节是紧密衔接、相互影响的。

图1.8 简化的FPGA开发流程

-

FPGA开发

+关注

关注

1文章

45浏览量

15440

原文标题:【精品博文】勇敢的芯伴你玩转Altera FPGA连载8:FPGA开发流程

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera Stratix 10和Agilex 7 FPGA的电源管理及配置问题案例

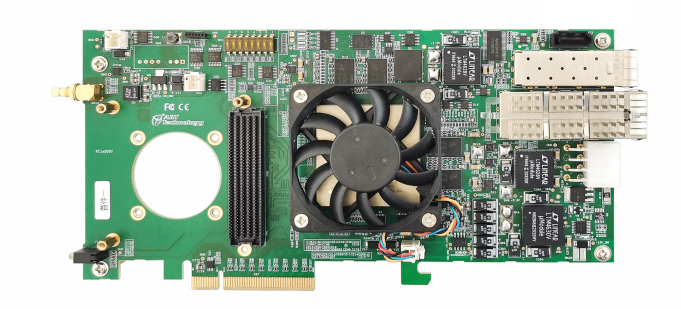

【经验分享】玩转FPGA串口通信:从“幻觉调试”到代码解析

Altera Agilex 3 FPGA和SoC产品介绍

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

玩转Altera FPGA的关键与FPGA开发流程分享

玩转Altera FPGA的关键与FPGA开发流程分享

评论