MOS管,作为现代电子设备中不可或缺的关键元件,广泛应用于各种电路设计中。然而,在MOS管的工作过程中,有时会出现电压或电流尖峰现象,这不仅可能影响电路的稳定性和可靠性,还可能导致设备损坏。因此,深入了解MOS管尖峰产生的原因对于电路设计和维护具有重要意义。本文将从多个方面详细分析MOS管尖峰产生的原因,并给出相应的解决方案。

一、MOS管的基本结构与工作原理

MOS管是一种具有绝缘栅的场效应晶体管(FET),其结构主要包括源极(S)、漏极(D)、栅极(G)和衬底(B)。MOS管的工作原理是通过改变栅极电压来控制源极和漏极之间的通道电阻,从而实现对电流的控制。当栅极电压达到一定阈值时,通道电阻迅速减小,形成导电通道,使得源极和漏极之间的电流迅速增加。

二、MOS管尖峰产生的原因

电感效应

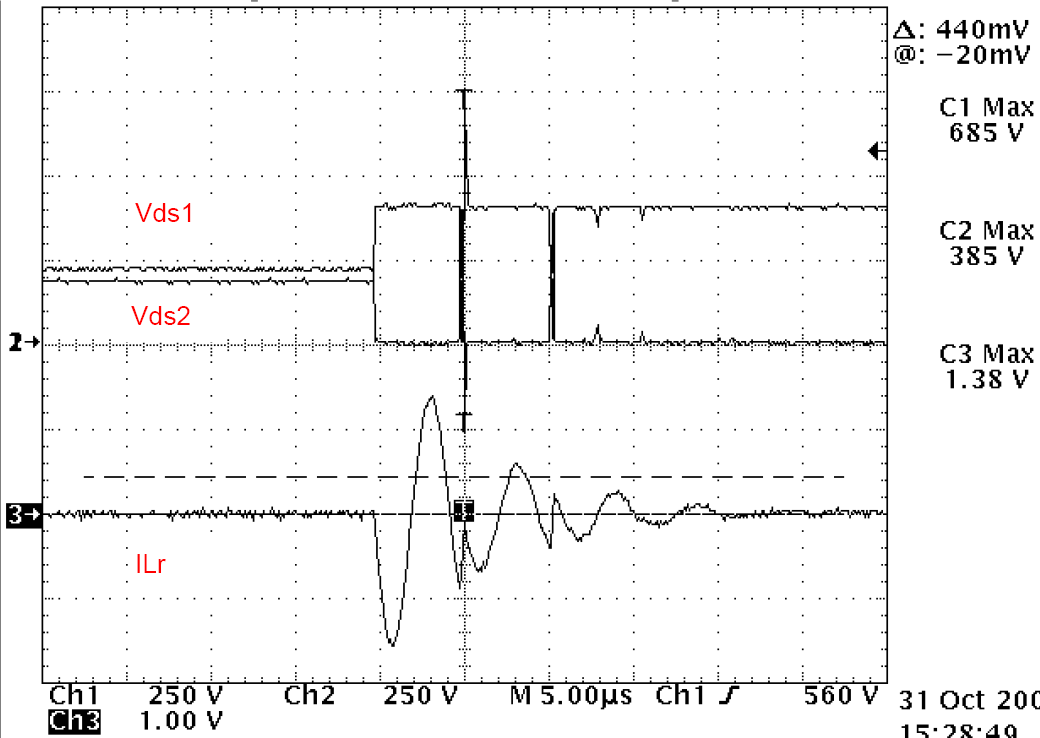

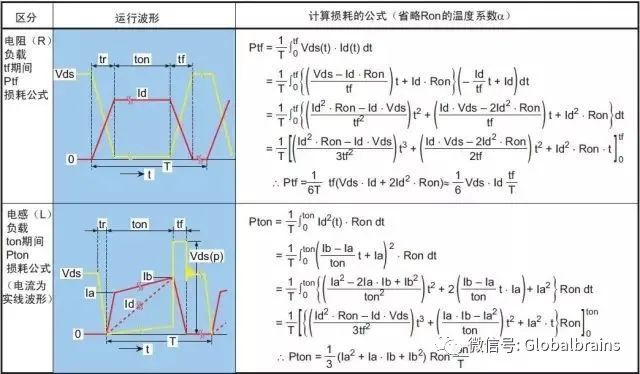

在MOS管的工作电路中,由于导线、元件等存在一定的电感,当MOS管开关时,电流的变化会在电路中产生电感压降(L*di/dt)。这个电感压降会叠加在MOS管的漏极电压上,形成电压尖峰。特别是在MOS管快速开关的情况下,电流变化率(di/dt)较大,产生的电感压降也较大,从而导致电压尖峰更加明显。

寄生电容效应

MOS管的源极和漏极之间存在寄生电容,这个电容在MOS管开关过程中会充放电。当MOS管从关闭状态切换到开启状态时,漏极电位迅速下降,导致寄生电容迅速放电,从而在漏极-源极(C_DS)之间产生尖峰电压。同样地,当MOS管从开启状态切换到关闭状态时,也会由于寄生电容的充放电过程而产生电压尖峰。

栅源寄生电容效应

MOS管内部存在栅源寄生电容,当MOS管关断时,栅源寄生电容上的电荷释放,也会产生电压尖峰。这种电压尖峰通常较小,但在某些特定情况下也可能对电路产生不良影响。

制造工艺与材料因素

MOS管的制造工艺和材料选择也会影响其尖峰特性。例如,MOS管中的氧化层厚度、掺杂浓度等参数的变化都可能影响其开关速度和通道电阻,进而影响电压尖峰的产生。此外,不同材料制成的MOS管在性能上也有所差异,可能导致不同的尖峰特性。

三、MOS管尖峰的影响与解决方案

MOS管尖峰对电路的影响主要表现在以下几个方面:一是可能导致电路中的其他元件损坏;二是可能使电路的稳定性下降;三是可能使电路的功耗增加。为了减小MOS管尖峰对电路的影响,可以采取以下解决方案:

优化电路设计

通过优化电路设计来减小电感效应和寄生电容效应的影响。例如,采用低电感元件和导线、减小寄生电容的大小等。

增加并联电阻和电容

在MOS管的源极和漏极之间增加并联电阻和电容可以减小电压尖峰的幅值。这是因为并联电阻和电容可以吸收和释放一部分电荷能量,从而减小电感压降和寄生电容充放电过程对电路的影响。

选用高性能MOS管

选用具有高性能的MOS管可以减小其尖峰特性。例如,选用具有低阈值电压、高开关速度等特性的MOS管可以减小电压尖峰的幅值和频率。

采用缓冲电路

在MOS管的两端加入缓冲电路可以减小电压尖峰的影响。缓冲电路可以吸收和释放一部分电荷能量,从而减小电感压降和寄生电容充放电过程对电路的影响。

综上所述,MOS管尖峰产生的原因主要包括电感效应、寄生电容效应、栅源寄生电容效应以及制造工艺与材料因素等。为了减小MOS管尖峰对电路的影响,可以采取优化电路设计、增加并联电阻和电容、选用高性能MOS管以及采用缓冲电路等解决方案。这些措施可以有效提高电路的稳定性和可靠性,降低设备损坏的风险。

-

MOS管

+关注

关注

109文章

2634浏览量

71258 -

晶体管

+关注

关注

77文章

10030浏览量

142244 -

尖峰

+关注

关注

0文章

14浏览量

7395

发布评论请先 登录

mos管尖峰电压如何消除

MOS管驱动波形和导通波形不对 ,还有尖峰

请问变压器的漏感只会在MOS管关断的时候,对MOS管DS间的电压产生影响吗?

反激式电源MOS管漏极开机瞬间尖峰电压很大,如何解决?

BUCK到底是怎么产生尖峰振荡呢?

半桥LLC电路中上管VDS的尖峰

产生尖峰电流的主要原因

mos管损坏的原因分析

MOS管尖峰产生的原因

MOS管尖峰产生的原因

评论