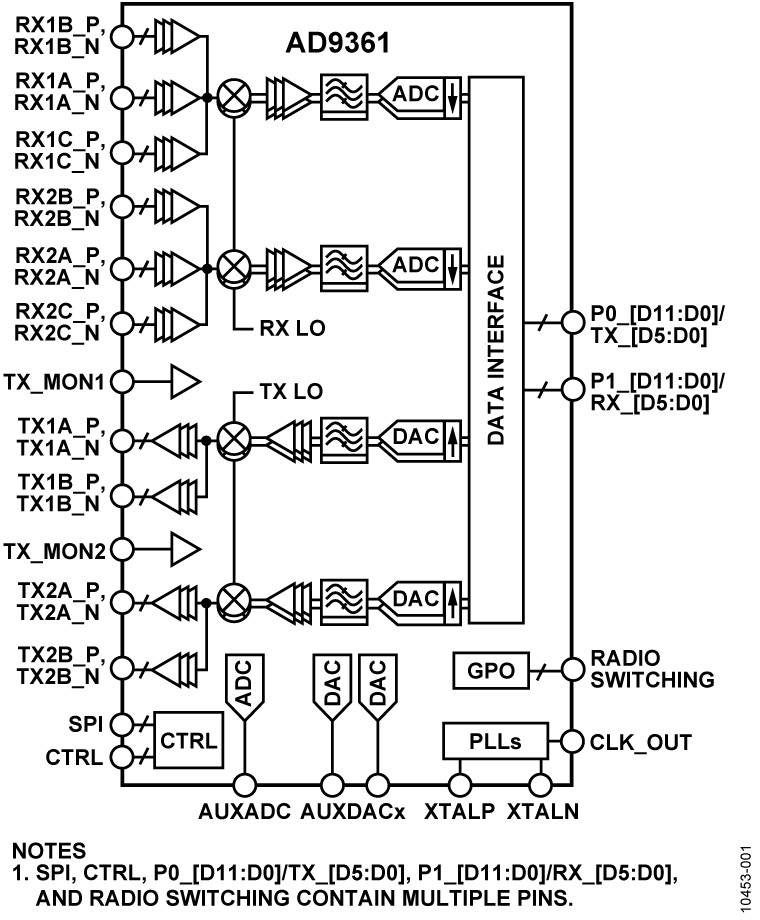

AD9361是ADI推出的面向3G和4G基站应用的高性能、高集成度的射频解决方案。该器件集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器提供可配置数字接口。AD9361接收器LO工作频率范围为70 MHz至6.0 GHz,发射器LO工作频率范围为47 MHz至6.0 GHz,涵盖大部分特许执照和免执照频段,支持的通道带宽范围为200 kHz以下至56 MHz。

两个独立的直接变频接收器拥有首屈一指的噪声系数和线性度。每个接收(RX)子系统都拥有独立的自动增益控制(AGC)、直流失调校正、正交校正和数字滤波功能,从而消除了在数字基带中提供这些功能的必要性。TheAD9361还拥有灵活的手动增益模式,支持外部控制。每个通道搭载两个高动态范围模数转换器(ADC),先将收到的I信号和Q信号进行数字化处理,然后将其传过可配置抽取滤波器和128抽头有限脉冲响应(FIR)滤波器,结果以相应的采样率生成12位输出信号。

发射器采用直接变频架构,可实现较高的调制精度和超低的噪声。这种发射器设计带来了行业较佳的TX误差矢量幅度(EVM),数值不到?40 dB,可为外部功率放大器(PA)的选择留出可观的系统裕量。板载发射(TX)功率监控器可以用作功率检测器,从而实现高度精确的TX功率测量。

完全集成的锁相环(PLL)可针对所有接收和发射通道提供低功耗的小数N分频频率合成。设计中集成了频分双工(FDD)系统需要的通道隔离。

AD9361系统构成

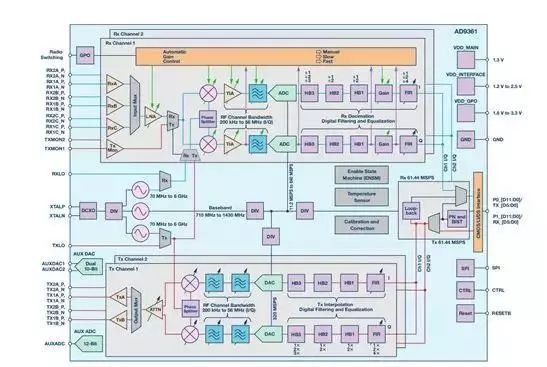

AD9361的框架如下图2-1所示:

图2-1

它支持2x2 MIMO通信,收发各有两条独立的射频通路。

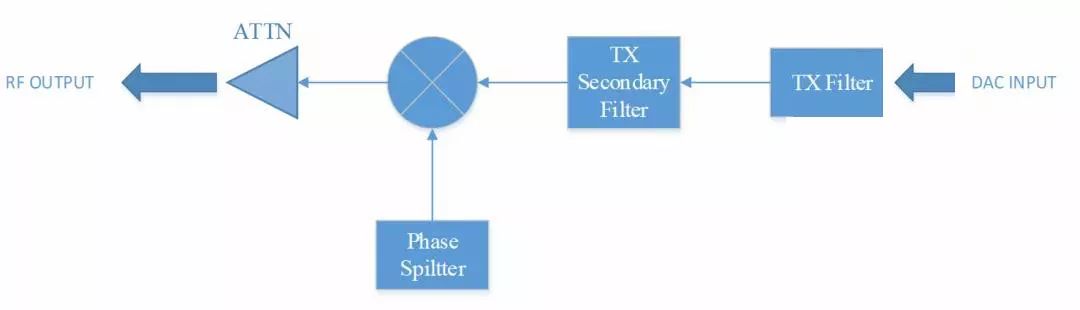

TX射频前端构成如下图2-2所示:

图2-2

TX数据通路如下图2-3所示:

图2-3

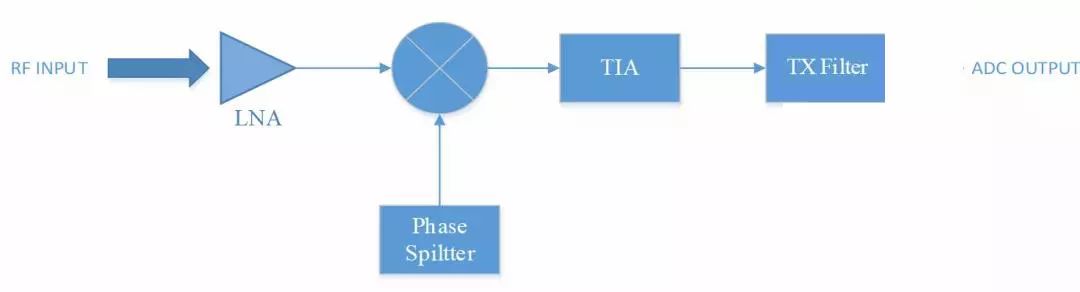

RX射频前端构成如下图2-4所示:

图2-4

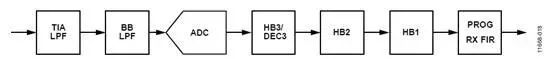

RX数据通路如下图2-5所示:

图2-5

初始化及校准总述

AD9361在上电之后便会进入休眠状态。此时用户需要根据所需参数,对芯片进行初始化配置。其配置包括以下几方面:

基本参数配置(包含SPI时钟频率、DCXO补偿、射频时钟使能)

BB PLL频率配置及校准

PolyPhase TX Digital Filter的系数写入

PolyPhase RX Digital Filter的系数写入

数字数据接口配置

AuxDAC/AuxADC初始化

Control_Out端口输出配置

GPO端口参数配置

频率无关的射频参数配置,包括LO Power、VCO&LDO

参数配置、Charge Pump校准等)

T/Rx频率综合器参数配置

T/Rx工作频率配置及校准

Mixer GM table增益配置

RX Gain table配置

RX手动增益配置

T/RX基带模拟滤波器校准(tune)

RX TIA配置及校准

二级TX滤波器校准

ADC初始化

BB/RF DC校准

发射数据正交性校准(相当于IQ校准)

TX增益配置

RSSI及功率测量的初始化

使用AD9361,我们主要关注的有五个方面:一是其中各器件的校准;二是有关滤波器的配置;三是有关数字部分接口的模式、工作方式的配置;四是射频工作状态机控制;五是有关T/Rx增益的配置。以下分4节对这几个方面分别阐述。

时钟源和RF & BB PLL频率综合器

由于时钟是整个芯片的核心,在介绍上节所述五方面之前,我们先详述一下AD9361的时钟、PLL和频率综合器。

01

参考时钟及DCXO

AD9361使用分数分频锁相环生成一个本地时钟为信号转换、数字滤波器、IO端口提供时钟源。这些PLL均需要一个参考时钟,这个时钟可以通过外部晶振提供,或者由外部晶体加上一个可变电容生成所需频率。在使用外部晶体的情况下,需使用DCXO补偿晶体频率来保证输出参考时钟稳定。

02

RF & BB PLL频率综合器

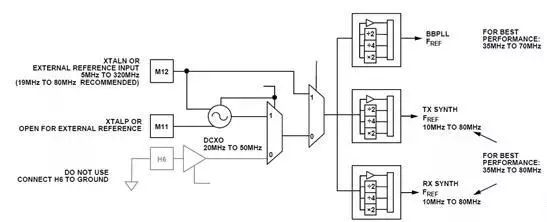

图4-1

参考时钟输入后,分别进入3个独立的PLL(如图4-1所示),分别为T/RX频率综合器、基带PLL提供参考时钟源。3个PLL需各自进行校准。

A)TX、RX PLL的锁定

在FDD模式下,TX和RX的PLL可工作在不同频率下,它们同时开启;TDD模式下,TX和RX的PLL根据收发情况轮流开启。

一般的TDD模式工作状态按照Rx-ALERT-Tx-ALERT-Rx跳转,基带通过跳转TXNRX信号来控制TX、RX状态的跳转,当TXNRX从0跳变到1时,RX PLL关闭,TX PLL开启并进行重新校准锁定,反之TX PLL关闭,RX PLL开启并重新校准锁定。TDD模式下每次PLL校准锁定的时间大概为45us~60us左右。

不过假如系统每次收发帧所使用的载波频率不变,则不需每次打开TX或RX时重新进行校准,而沿用上一次的校准值。此时需要在一次校准过后将寄存器中的VCO Cal比特关闭,这样可以明显得缩短信号收发之前,频率综合器的稳定时间。

B)Fast Lock模式

假如你的系统需要在多个频点上工作,则可以使用Fast Lock模式,它支持保存多个频点的频率控制字,使得频率变化是,PLL的锁定时间短。然而这种模式TX和RX分别只能保存8个频点,还是有一点局限性。

器件校准

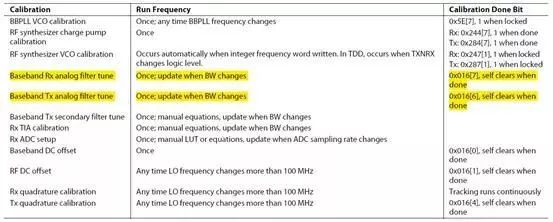

AD9361的校准及其校验方式简介如下表5-1所示:

表5-1

每次芯片上电或者硬件复位之后都必须进行校准,校准之后的参数会被保存。

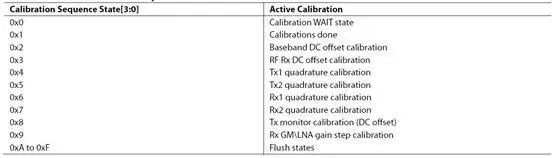

校准的顺序由状态机控制,其状态如下表5-2所示。由于其中部分校准需导入其他校准所得结果,因此假如多个校准同时使能,则校准顺序由校准状态机控制。当校准状态机停留在0x1状态时,表示校准完成。

需要注意的是:T/Rx的基带滤波器校准不受校准状态机控制,必须在其他校准均不进行时,进行T/Rx基带滤波器的校准。

表5-2

下面对几个重要的校准进行单独阐释。

注1:RF频率综合器VCO校准

AD9361的发射和接收的频率综合器是独立的,因此TX和RX的RF VCO校准需分别进行。

在TDD模式下,TXNRX为高代表发射,TXNRX低代表接收,做RF TX VCO校准是,TXNRX需拉高;RF RX VCO校准时,TXNRX拉低。FDD模式下,需要将ENSM调整到ALERT状态,随后使能频率综合器校准。

官方建议无论使用TDD还是FDD工作模式,均可在做RF频率综合器VCO校准时,使用FDD的校准方式,因为FDD校准的频率较为准确稳定,但是弊端是耗时较长。

注2:T/Rx模拟滤波器校准

模拟滤波器校准有一点需要注意,在进行校准带宽设置时,带宽值需要设置成BB带宽的1.6倍,BB带宽值是基带复数输出带宽的一半,即RX为26MHz~0.2MHz,TX为20MHz~0.625MHz。

滤波器配置

本节介绍发射和接收的滤波器通路。

01

发射滤波器通路

TX滤波器通路总体分为3级数字滤波器和两级模拟滤波器,示意图如下图6-1所示:

图6-1

通路输入为I、Q两路12bit补码。

A)TX数字滤波器

数字滤波器分为4级,主要用于对接口I、Q信号进行插值滤波。它们可由用户控制选通。

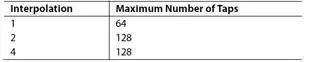

第一级Prog TX FIR支持1倍、2倍、4倍插值,可通过用户配置最高128阶位宽16bit滤波器系数,并且可提供0~-6db滤波器增益。其插值倍数和滤波器阶数关系如表6-1所示:

表6-1

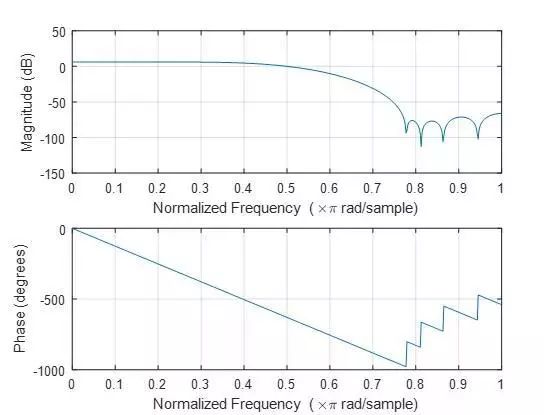

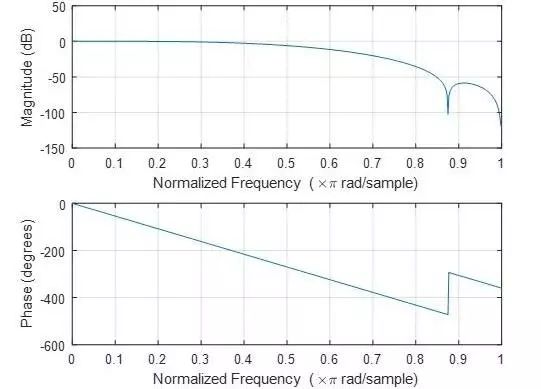

第二级HB1是一个固定2倍插值低通滤波器。其滤波器系数为[?53, 0, 313, 0, ?1155, 0, 4989, 8192, 4989,0, ?1155, 0, 313, 0, ?53]。频率幅度相应如图6-2:

图6-2

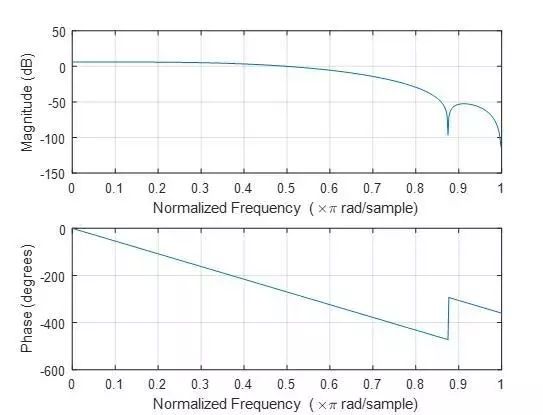

第三级HB2也是一个固定2倍插值低通滤波器,系数为[?9, 0, 73, 128, 73, 0, ?9]。其幅频相应如图6-3所示。

图6-3

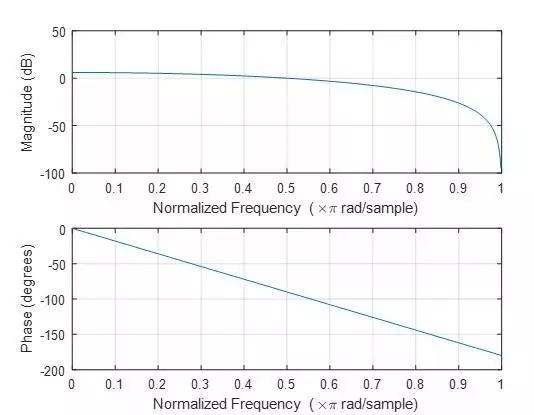

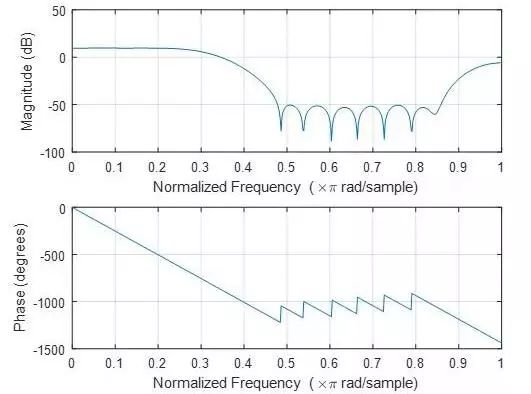

第四级HB3/INT3可实现2倍或者3倍插值。2倍插值滤波系数为[1, 2, 1],其幅频相应如图6-4所示。三倍插值系数为[36, ?19, 0, ?156, ?12, 0, 479, 223, 0, ?1215, ?993, 0, 3569, 6277,8192, 6277, 3569, 0, ?993, ?1215, 0, 223, 479, 0, ?12, ?156, 0, ?19, 36],幅频相应如图6-5所示。

图6-4

图6-5

B)TX模拟滤波器

在数字滤波信号经过DAC转换成模拟信号之后,需要经过低通滤波器在滤除杂散干扰。

模拟滤波器分为两级,带宽均可配置。第一级的带宽范围较窄,为625kHz~32MHz,通带带宽设置为信号带宽的1.6倍;第二级的带宽范围为2.7MHz~100MHz,通带带宽设置为信号带宽的5倍。

02

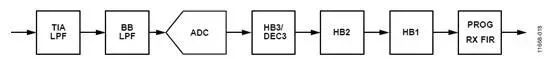

接收滤波器通路

接收通路分为两级模拟滤波器和四级数字滤波器,连接示意图如图6-6所示:

图6-6

通路输出也为12bit补码。

A)RX模拟滤波器

接收端模拟滤波器也分为两级,第一级TIA LPF的可配置带宽为1MHz~70MHz,配置带宽设置为信号带宽的2.5倍;第二级BB LPF的可配带宽为200kHz~39.2MHz,配置带宽为信号带宽的1.4倍。

B)RX数字滤波器

数字通路的4级滤波器正好是发射通路的反向。

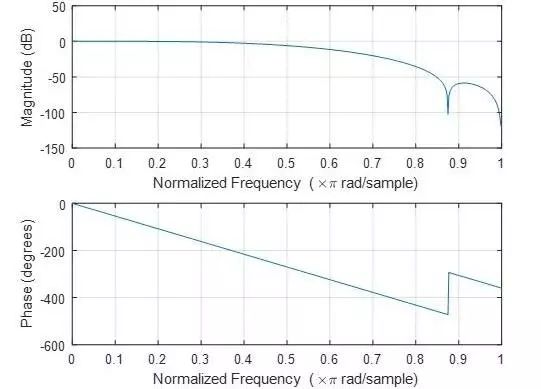

第一级HB3/DEC3为2倍或3倍抽取可选。2倍抽取的滤波系数为[1, 4, 6, 4, 1],其幅频相应如图6-7所示。3倍抽取滤波器系数为[55, 83, 0, ?393, ?580, 0, 1914, 4041, 5120, 4041, 1914, 0, ?580,?393, 0, 83, 55]。其幅频相应如图6-8所示。

图6-7

图6-8

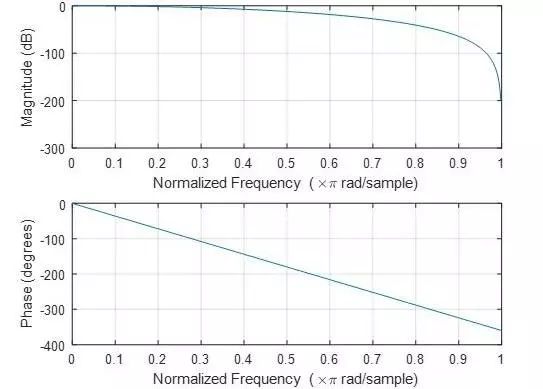

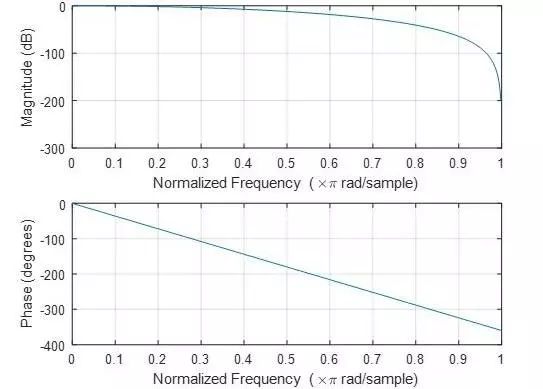

第二级HB2和第三级HB1均为2倍抽取的低通滤波器。其系数如下:

HB2:[?9, 0, 73, 128, 73, 0, ?9]

HB3:[?8, 0, 42, 0, ?147, 0, 619, 1013, 619, 0, ?147, 0, 42, 0, ?8]

HB2的幅频相应如图6-9,HB3的幅频相应如图6-10。

图6-9

图6-10

最后一级Prog RX FIR也支持1倍、2倍、4倍抽取,可通过用户配置128阶位宽16bit滤波器系数,并且可提供-12db、-6db、0db、6db滤波器增益。

数字接口详述

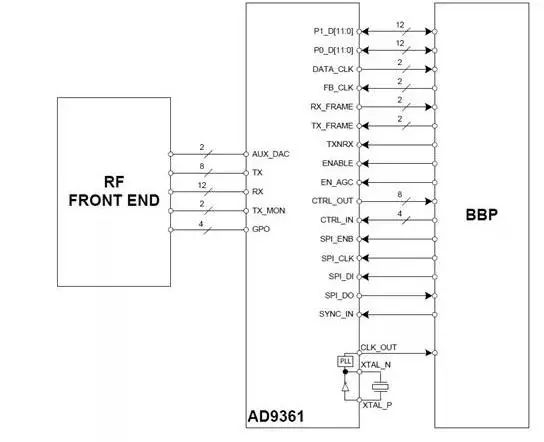

AD9361与数字基带的接口示意图如图7-1所示:

图7-1

数字接口电平有两种可配置模式:CMOS和LVDS。

01

接口功能介绍

AD9361主要的接口有SPI、数据端口P0_D、P1_D、DATA_CLK、FB_CLK、TX_FRAME、RX_FRAME、ENABLE、TXNRX。

SPI:该芯片集成的SPI接口为4线SPI,可读可写,主要用于配置内部寄存器。

P0/1_D:这是数据传输端口,位宽均为12bit,根据应用模式可配置成输入、输出和双向。

DATA_CLK:DATA_CLK由AD9361输出。该时钟主要用于RX状态外部数字基带对P0_D、P1_D数据采样,数字基带生成的数据和控制信号均需为DATA_CLK时钟域的,否则可能导致AD9361获取数据时的采样问题。CMOS模式下DATA_CLK通过DATA_CLK_P端口输出。

FB_CLK:FB_CLK是DATA_CLK反馈到AD9361的数据时钟。用于AD9361内部对TX_FRAME、ENABLE、TXNRX信号的上升沿采样,以及对于P0_D、P1_D数据端口的上升沿和下降沿采样。注意:FB_CLK必须与DATA_CLK同源(频率相同,占空比相同),对两个时钟的相位没有要求。CMOS模式下,仅适用FB_CLK_P线。

RX_FRAME:RX_FRAME用于在接收状态下标识P0_D、P1_D的数据有效。它可以配置成常高,或是50%占空比的脉冲信号。

TX_FRAME:TX_FRAME用于TX状态下,标识发射数据有效。其时序与RX_FRAME类似。发射状态下,TX_FRAME为低,射频发射空数据。

ENABLE & TXNRX:ENABLE和TXNRX信号主要在TDD模式下使用,ENABLE拉高时,根据TXNRX信号,使射频芯片进入TX或RX状态,TXNRX为1表示TX,为0表示RX。

02

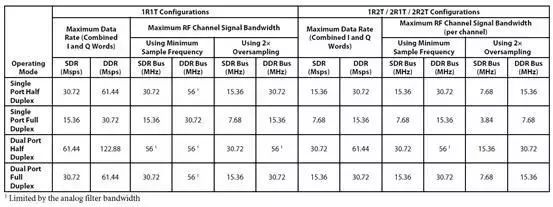

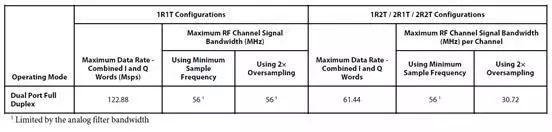

接口模式

AD9361数字接口模式主要分四个方面:电平模式(LVDS、CMOS),数据速率(Single Data Rate(SDR)、Dual Data Rate(DDR)),端口模式(Dual Port、Single Port)、收发天线个数(1T1R、2T2R)(此处暂时不详述)。

A)电平模式

接口电平模式主要根据电平信号类型来分类,主要分为两种:LVDS模式和CMOS模式。它们的区别体现在可使用的信号bit为上。

CMOS模式下,各种接口时序的最高频率如表7-1所示。

表7-1

LVDS模式下,各接口时序的最高频率如表7-2所示。

表7-2

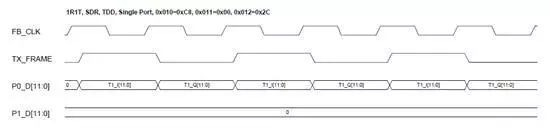

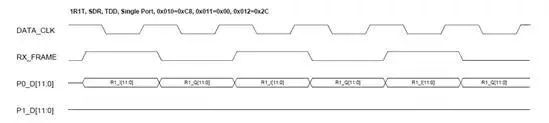

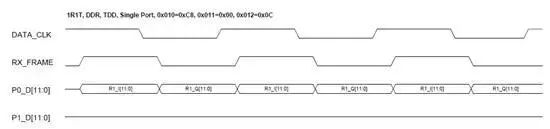

CMOS模式下,所有接口信号都是单端信号。在此电平模式下,允许两组12bit端口P0_D、P1_D并行使用,即允许双端口时序。CMOS模式下,单端口信号TX时序如图7-2,RX时序如图7-3;P0/1_D和T/Rx_D_P/N的对应关系可参见硬件连接的spec。

图7-2

图7-3

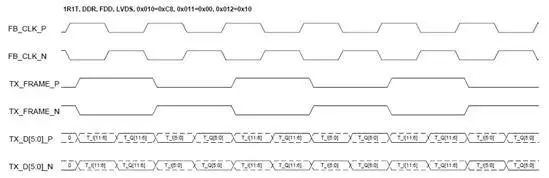

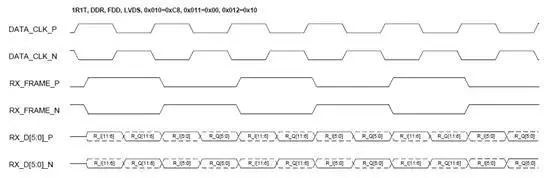

LVDS模式下,每bit信号需要P和N两个接口,因此24bit接口用作12bit数据信号。LVDS模式下,TX信号时序如图7-4所示,RX信号时序如图7-5所示。

图7-4

图7-5

B)数据速率

数据速率是针对数据端口和时钟的关系来区分。主要分为两种:Single Data Rate(SDR)、Dual Data Rate(DDR)。

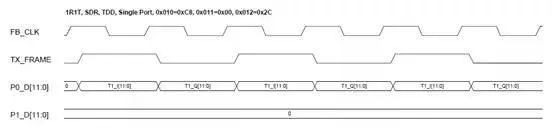

SDR的时序举例如下图7-6所示:

图7-6

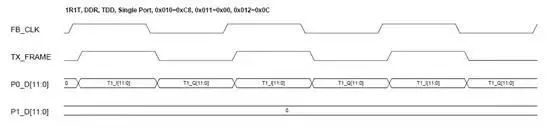

DDR的时序举例如图7-7所示:

图7-7

C)端口模式

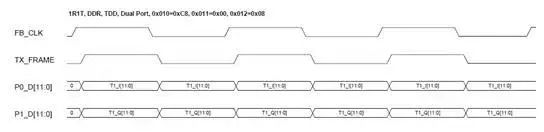

端口模式的区分主要根据使用端口的个数上,分为双端口(Dual Port)和单端口(Single Port)。

单端口如图7-8所示;双端口如图7-9所示。

图7-8

图7-9

射频工作状态机控制

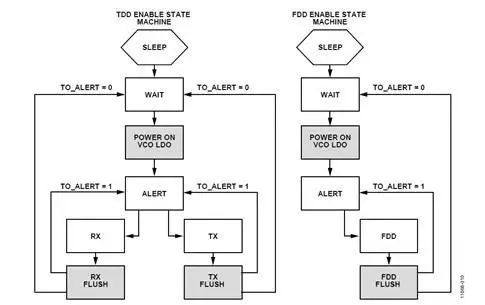

AD9361的工作模式通过状态机(ENSM,enable state machine)控制,ENSM可通过SPI控制状态跳转,也可以通过ENABLE、TXNRX pin信号来实时控制。不过假如校准不成功,这些控制均无效。

图8-1为TDD和FDD模式下,ENSM各状态之间的跳转关系。图中的TO_ALERT是通过寄存器ENSM Config1控制,它的作用是在ENSM从TX或者RX状态跳转到WAIT状态后,自动进入ALERT状态。

图8-1

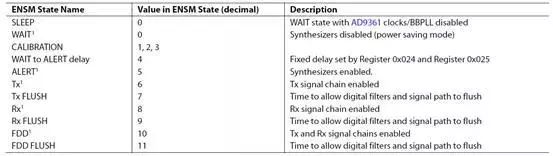

ENSM的状态定义如表8-1所示。

表8-1

01

SPI控制

SPI控制跳转与接口时钟DATA_CLK非一个时钟域,因此被认为是异步跳转,默认关闭,可通过ENSM Config1寄存器打开。

ENSM状态机控制寄存器如下表8-2所示:

表8-2

其中Force Rx、Force Tx、Force Alert State用于在TDD模式下,SPI控制状态机。而在FDD模式下,Force Rx信号是无用的,从ALERT->FDD状态通过Force Tx控制。

02

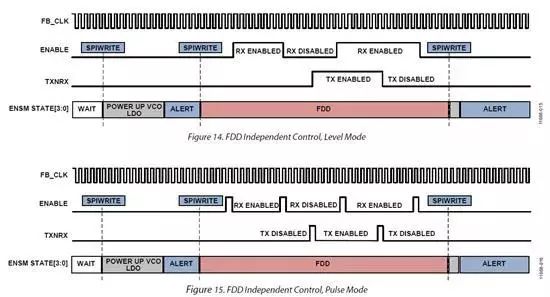

ENABLE/TXNRX PIN控制

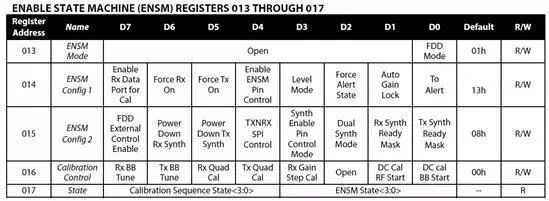

ENABLE/TXNRX Pin控制跳转默认开启。这种控制模式还分两种:一种是Pulse Mode;二是Level Mode。

Pulse Mode

PulseMode的Pulse主要是针对ENABLE信号而言的。TXNRX主要标示下一个状态是跳转到TX还是RX,为1时跳转TX,为0时跳转RX。

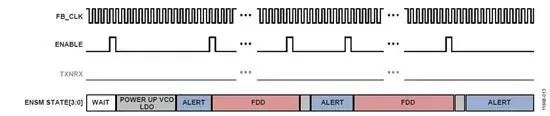

ENABLE以脉冲的形式给出,脉宽不得小于一个FB_CLK周期。TDD模式下控制时序如下图8-2所示:

8-2

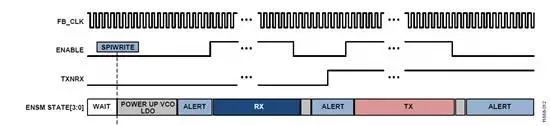

FDD模式下,控制时序如图8-3所示:

图8-3

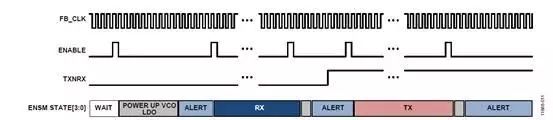

Level Mode

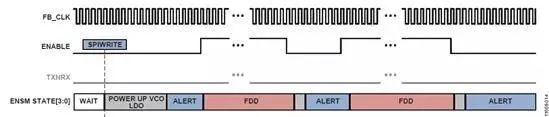

LevelMode下,ENABLE以电平形式给出,而ENABLE信号为高时表示芯片现在处于工作状态。而VCO、LDO的上电使能还是要通过SPI配置。

TDD模式下,控制时序如图8-4所示:

图8-4

FDD模式下,控制时序如图8-5所示:

图8-5

03

FDD Independent模式

AD9361的TX和RX在FDD模式下允许工作在同一载波频率下,这就使得FDD模式不局限于仅适用在全双工系统中。像wifi、蓝牙这样的半双工系统,也可以使用FDD模式来避开TDD模式下PLL稳定时间较长的问题。而假如FDD模式,TX、RX工作在同一频率,则会导致发送和接收的相互干扰,此时我们就需要TX、RX支持开关。

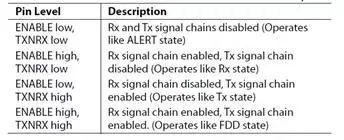

而本小节的FDD Independent模式便支持收发开关独立控制,功能开关是ENSM Config2 D7比特。功能开启后,可通过TXNRX、ENABLE共同控制TX、RX的开启关闭,控制逻辑如表8-3所示。

表8-3

这个模式下,收发关闭后,状态机是不会跳转到FDD FLUSH状态的,因此用户使用时要控制好时间,在两次收或者发开启之间留下足够的时间清空残留数据。

FDDIndependent模式的Level Mode和Pulse Mode的控制时序如图8-6所示:

图8-6

04

ENSM与RF VCO校准

ENSM会输出一个内部信号,控制TX、RX频率综合器校准。

FDD模式下,TX、RX频率综合器会在两种情况下进行校准,一是ENSM从WAIT->ALERT时,二是频率控制字写入时。而在FDD状态下,校准结果是保持不变的。

TDD模式下,与FDD类似,会在ENSM从WAIT->ALERT时进行校准,在频率控制字写入时,会根据TXNRX判断,让当前使能的VCO进行校准。

为了节省功耗,TDD模式下,T/Rx的VCO并一直保持锁定状态,在RX使能时,TX VCO会关闭,反之亦然。当TXNRX改变时,再对当前使能的VCO重新校准。因此在使用时,ALERT状态下应该尽早跳转TXNRX来为VCO校准争取较多时间。

(我司是一家中高端电子元器件的混合型分销商及授权代理商。---深圳市芯科华高科技有限公司

公司总部设立在深圳福田,在成都、南京、上海、香港、新加坡等地设有分支机构。公司拥有优质稳定的产品供货渠道、具备多年从业经验的经营管理团队,及专职技术支持团队。

客户群体包含国内主要国防军工企业、科研院所、高校、上市公司等。

主营业务:公司业务以高端芯片进出口业务、国产元器件的代理业务以及一站式配套服务业务为主。

主要产品:以高端微波芯片、高速ADC/DAC、FPGA芯片及整板配套产品为主,包括XILINX、ADI、TI全系列受控开发板均有优势。

主要优势品牌: XILINX、ADI、ALTERA、MACOM、TI、MINI、QORVO、LT、E2V、EUVIS、CREE、MICRON、NXP、AVAGO、TOSHIBA 等国际一线厂牌。)

审核编辑 黄宇

-

芯片

+关注

关注

460文章

52616浏览量

442712 -

ADI

+关注

关注

149文章

46045浏览量

262519 -

接收器

+关注

关注

15文章

2577浏览量

74185

发布评论请先 登录

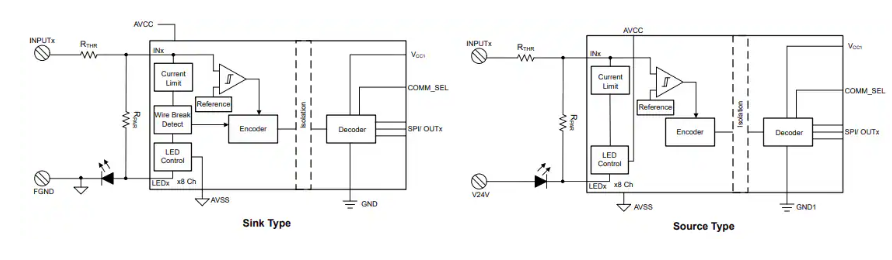

Texas Instruments ISO1228数字输入接收器数据手册

【PZSDR AD9361】——璞致PZ-FL9361 软件无线电模块:工业级射频解决方案的技术标杆

蓝牙接收器SRRC认证流程解析

AD9361

芯知识|WT588系列语音芯片BUSY引脚功能解析与设计指南

USB接收器的安装和使用

AD9361 RF捷变收发器,评估套件和开发资源

AD9361接收器简述的应用及功能解析——chiptuo(芯片拓展者)

AD9361接收器简述的应用及功能解析——chiptuo(芯片拓展者)

评论