Cadence近日宣布,其数字和定制/模拟流程在Intel的18A工艺技术上成功通过认证。这一里程碑式的成就意味着Cadence的设计IP将全面支持Intel的代工厂在这一关键节点上的工作,并提供制程设计套件(PDK),助力开发者加速一系列前沿应用的开发,包括低功耗消费电子、高性能计算(HPC)、人工智能和移动计算设计。

值得一提的是,Cadence的研发团队与Intel代工厂紧密合作,确保了流程的兼容性和高效性。这次认证不仅为客户提供了一流的SoC(系统级芯片)和芯片系统设计能力,还推动了更先进的人工智能、高性能计算和高级移动应用的开发。

Cadence为Intel 18A技术设计的IP具有广泛的应用范围,特别在高性能计算(HPC)和人工智能/机器学习(AI/ML)领域表现出色。其中包括支持企业级PCI Express(PCIe)6.0和Compute Express Link(CXL)的解决方案,为数据传输和计算性能提供了强大的支持。此外,LPDDR5X/5 8533Mbps的多标准PHY则能够满足多样化的存储应用需求。值得一提的是,UCIe技术将进一步提升多芯片系统的封装集成能力,而112G超长距离SerDes则以其卓越的比特误码率(BER)性能,为数据传输提供了坚实的保障。

此次认证不仅证明了Cadence在半导体设计领域的领先地位,也为其客户提供了更加可靠和高效的设计流程和设计IP。随着这些先进的工具和技术的广泛应用,我们有理由期待在未来看到更多创新的产品和应用快速上市,满足市场和消费者的需求。

-

半导体

+关注

关注

335文章

29039浏览量

240319 -

Cadence

+关注

关注

67文章

978浏览量

144609 -

intel

+关注

关注

19文章

3497浏览量

188760

发布评论请先 登录

Cadence携手台积公司,推出经过其A16和N2P工艺技术认证的设计解决方案,推动 AI 和 3D-IC芯片设计发展

新思科技与英特尔在EDA和IP领域展开深度合作

BiCMOS工艺技术解析

英特尔 Panther Lake 移动 SoC 延迟上市,又是18A背锅?

英特尔18A与台积电N2工艺各有千秋

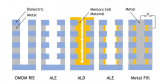

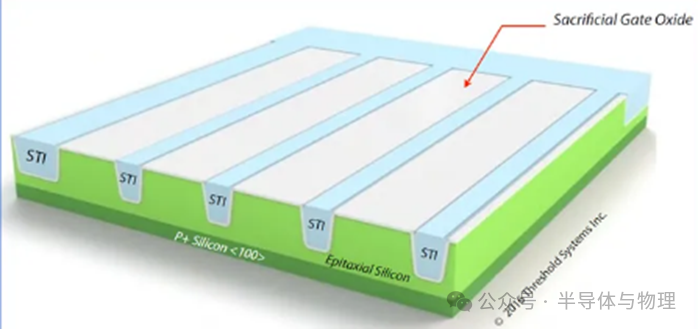

ALD和ALE核心工艺技术对比

Cadence数字和定制/模拟流程通过Intel 18A工艺技术认证

Cadence数字和定制/模拟流程通过Intel 18A工艺技术认证

评论