相位抖动是从哪来的?通信中有哪些抖动?

相位抖动是指信号在传输过程中产生的相位变化,导致信号的相位偏离理想值的现象。它是由多种因素引起的,包括时钟不准确、传输介质不稳定、信号传输路径不确定等。

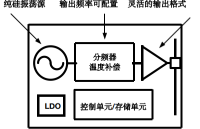

时钟抖动是相位抖动的主要原因之一。在通信系统中,时钟扮演着非常重要的角色,它确定了信号的采样时间和传输速率。然而,由于各种原因,包括晶体振荡器的温度变化、电力供应的不稳定、电磁干扰等,时钟信号会产生偏移和抖动,导致传输的信号出现相位变化。

传输介质的不稳定性也会导致相位抖动。例如,在光纤通信中,光信号在光纤中的传输受到多种影响,如折射率的变化、光纤的拉伸和压缩等,这些因素都会导致信号的传输速度和相位发生变化,从而产生相位抖动。

除了时钟抖动和传输介质不稳定性,信号传输路径的不确定性也是相位抖动的一个重要原因。在实际的通信系统中,信号通常需要经过多个中继站点或路径,每个中继站点都会对信号进行处理和转发,这会导致信号的传输时间和相位发生变化,从而产生相位抖动。

在通信中,相位抖动会对信号的质量和可靠性产生一定的影响。当相位抖动超过一定的范围时,会导致信号的错位和失真,使接收端无法正确解读信号的信息。这对于需要高速传输和高精度的信号来说尤为重要,例如无线通信、高速数据传输等领域。

为了降低相位抖动对通信的影响,可以采取一系列的技术手段。例如,在时钟抖动方面,可以使用更稳定、更精确的时钟源,如GPS同步和精密振荡器。在传输介质不稳定性方面,可以采用抗快速衰减和抗色散的光纤材料,并对光纤进行稳定的温度和压力控制。在信号传输路径的不确定性方面,可以优化和规划网络拓扑结构,减少中继站点的数量和信号转发的次数。

综上所述,相位抖动是通信中常见的现象,由多种因素引起。它会对信号的相位产生变化,影响通信的质量和可靠性。为了降低相位抖动的影响,需要采取一系列的技术手段来优化通信系统的设计和实施。

相位抖动是指信号在传输过程中产生的相位变化,导致信号的相位偏离理想值的现象。它是由多种因素引起的,包括时钟不准确、传输介质不稳定、信号传输路径不确定等。

时钟抖动是相位抖动的主要原因之一。在通信系统中,时钟扮演着非常重要的角色,它确定了信号的采样时间和传输速率。然而,由于各种原因,包括晶体振荡器的温度变化、电力供应的不稳定、电磁干扰等,时钟信号会产生偏移和抖动,导致传输的信号出现相位变化。

传输介质的不稳定性也会导致相位抖动。例如,在光纤通信中,光信号在光纤中的传输受到多种影响,如折射率的变化、光纤的拉伸和压缩等,这些因素都会导致信号的传输速度和相位发生变化,从而产生相位抖动。

除了时钟抖动和传输介质不稳定性,信号传输路径的不确定性也是相位抖动的一个重要原因。在实际的通信系统中,信号通常需要经过多个中继站点或路径,每个中继站点都会对信号进行处理和转发,这会导致信号的传输时间和相位发生变化,从而产生相位抖动。

在通信中,相位抖动会对信号的质量和可靠性产生一定的影响。当相位抖动超过一定的范围时,会导致信号的错位和失真,使接收端无法正确解读信号的信息。这对于需要高速传输和高精度的信号来说尤为重要,例如无线通信、高速数据传输等领域。

为了降低相位抖动对通信的影响,可以采取一系列的技术手段。例如,在时钟抖动方面,可以使用更稳定、更精确的时钟源,如GPS同步和精密振荡器。在传输介质不稳定性方面,可以采用抗快速衰减和抗色散的光纤材料,并对光纤进行稳定的温度和压力控制。在信号传输路径的不确定性方面,可以优化和规划网络拓扑结构,减少中继站点的数量和信号转发的次数。

综上所述,相位抖动是通信中常见的现象,由多种因素引起。它会对信号的相位产生变化,影响通信的质量和可靠性。为了降低相位抖动的影响,需要采取一系列的技术手段来优化通信系统的设计和实施。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟抖动

+关注

关注

1文章

63浏览量

16195 -

信号传输

+关注

关注

4文章

457浏览量

20736

发布评论请先 登录

相关推荐

热点推荐

差分输出VCXO振荡器 | FCom富士晶振 - 低抖动时钟解决方案

FCom富士晶振提供FVC-3L/5L/7L-PG系列差分VCXO,支持LVPECL/LVDS输出,低相位抖动,适用于光通信、工业控制、数据存储等领域的高精度时钟应用。

差分输出VCXO:低抖动时钟源助力光通信系统精密同步

在高速光通信系统中,时钟信号的相位稳定性与输出结构决定了整个链路的同步能力与数据可靠性。传统的CMOS单端输出振荡器难以满足SerDes、CDR、PAM4调制等对低抖动与对称输出的要求。此背景下,集

【电子元件】FCO-3L-PG系列FASTXO差分输出振荡器:低相位抖动与宽频应用设计

内容概要:本文档详细介绍了FCO-3L-PG系列FASTXO频率差分输出振荡器的技术规格和应用特性。该振荡器支持10至1500MHz的频率范围,具有低相位抖动(0.6pS典型值)和三态使能/禁用

发表于 05-20 14:23

?0次下载

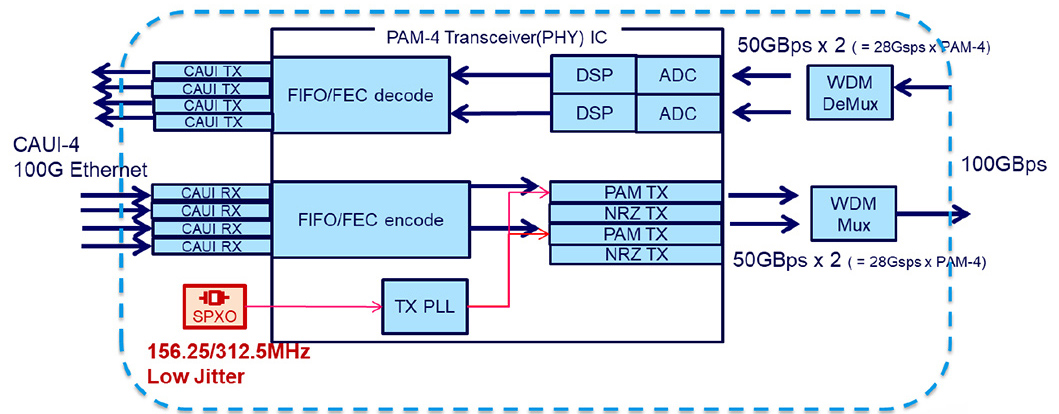

低抖动差分晶振SG2520VHN 312.5Mhz在PAM4调制光模块中的应用

CCHPZB,频点312.5Mhz,凭借其低相位抖动、高频特性、小尺寸封装以及宽温度范围等优势,成为PAM4光模块中理想的时钟解决方案。 1.?提供高精度时钟信号 SG2520VHN 312.5Mhz晶振具有低相位抖动(最大值为50fs),能够为PAM4调制光模块提供高

实现 65fs Typ.※1低相位抖动 差分输出石英晶体振荡器“SG7050EBN”商品化

基波※2 起振并实现低相位抖动※3。本商品应对 100MHz 至 175MHz 的频率,相位抖动为 65fs Typ.,实现了高标准规格,能够满足高端路 由器等有线

发表于 11-29 15:48

?0次下载

周期性抖动例如电源上的抖动造成时钟的Dj对 ENOB有影响吗?如何计算这部分的影响?

一般考量采样时钟抖动对ADC ENOB的影响都是用相位噪声的随机抖动Rj计算,想请教周期性抖动例如电源上的抖动造成时钟的Dj对 ENOB

发表于 11-13 08:15

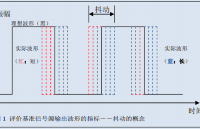

抖动定义和测量

引言:时钟抖动(jitter)是现代通信和数字系统中至关重要的性能指标之一,对数据传输速率和系统同步起着关键作用。本文将深入探讨时钟抖动的定义、不同类型,详细介绍各种抖动类型的测试方法

数字锁相环固有的相位抖动是怎样产生的,如何解决

数字锁相环(DPLL)固有的相位抖动主要来源于多个方面,这些抖动因素共同影响着锁相环的同步精度和稳定性。以下是数字锁相环相位抖动产生的主要原因:

CDR电路设计与抖动管理

在高速串行通信系统中,CDR(时钟数据恢复)技术是实现数据传输的关键技术之一。然而,CDR电路的设计面临着一个重要的挑战——抖动。抖动现象指的是数据信号在实际传输过程中的位置相对于理想位置的偏离

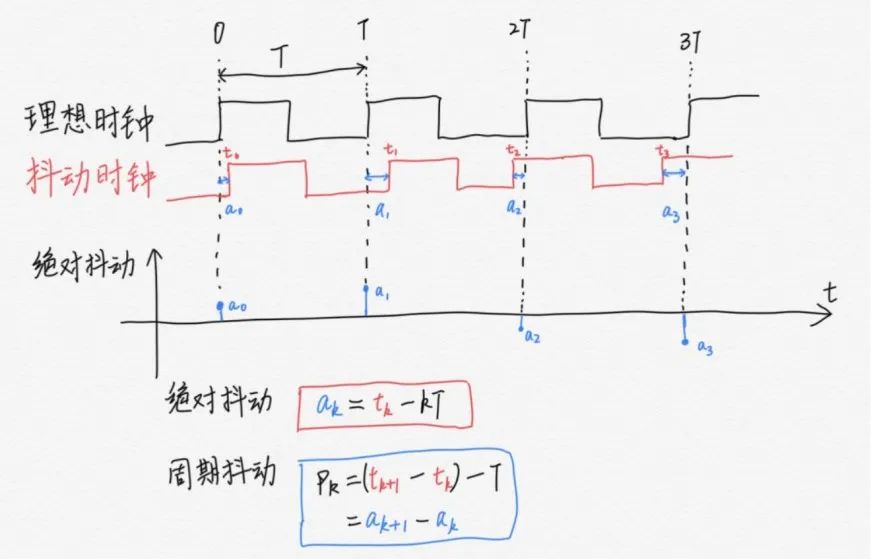

抖动的概念和类型 量化时域抖动、随机抖动和频域抖动的方法

绝对抖动 (Absolute Jitter) 是一个衡量时间点的不确定性概念,参考为理想时钟的时间点,该相对偏差量可能表示为一个离散时间的随机变量。绝对抖动造成的时间点不确定性可能会对很多采样电路

时钟抖动与相位噪声的关系

时钟抖动和相位噪声是数字系统和通信系统中两个至关重要的概念,它们之间存在着紧密而复杂的关系。以下是对时钟抖动和相位噪声关系的详细探讨,旨在全

FPGA如何消除时钟抖动

在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从

抖动与相位噪音的基础知识

【序文】近年,伴随影像传输等普及,骨干网中流过的通信量有增无减,通信的高速、大容量化进展迅速。在这种情况下,高速化通信基础设施对高频且输出信号稳定的基准信号源的需求十分强烈。抖动(Ji

相位抖动是从哪来的?通信中有哪些抖动?

相位抖动是从哪来的?通信中有哪些抖动?

评论