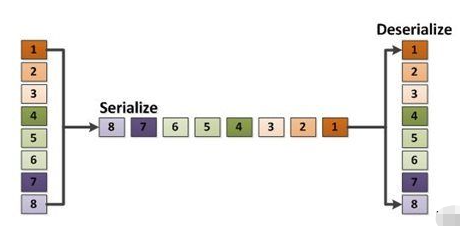

串行解串器 (Serializer/Deserializer, SerDes)的特点为数据与时钟在同一信道中传输,在接收端通过时钟数据恢复技术(CDR)提取数据中所包含的时钟信息并以此时钟采样接收到的数据。当前,绝大部分高速信号传输使用SerDes 结构。

SerDes 的发送端(TX)包括并串转换器、编码器、发送端均衡、驱动器等部分,SerDes 的接收端(RX)包括接收端衰减器 (ATT)、接收端均衡、时钟数据恢复、解码器、串并转换等。目前SerDes 主要有并行时钟 SerDes 方案(Parallel Clock SerDes)、嵌入式时钟SerDes 架构 (Embedded Clock SerDes)、8bit/10bit SerDes 方案、位交织SerDes 方案(Bit Interleaved SerDes)四种实现方案。

并行时钟 SerDes 方案中时钟与数据分离,数据与控制/地址位信号分别传输,其中数据与时钟信号分别通过特定线传输,常用于低速传输。其优点在于不需要时钟数据恢复电路,电路简单,对抖动要求低;其缺点在于需要额外的时钟线,且时钟线会造成电磁辐射(EMI)及串扰,因此无法在高速链路上使用。目前采用该种 SerDes 的有 DDR 等。

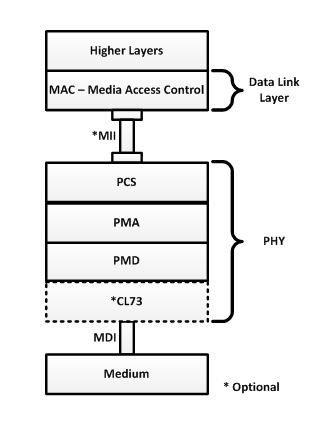

嵌入式时钟 SerDes 架构是标准 SerDes 架构,即时钟嵌入数据信号中并在接收端通过 CDR 恢复。优点在于消除了单独时钟线引起的电磁干扰和串扰的影响,且减少了时钟线对 PCB 布局的影响;缺点在于远端时钟恢复对抖动要求高,PCle、USB 3.0、USB 3. 1、SATA 均采用此种 SerDes 方案。

8bit/10bit SerDes 方案,即在串行数据中添加额外编码来平衡直流分量,降低CDR 压力。其编码不一定是 8bit/10bit,也有更高效率的编码,比如 PCle3.0的 128bit/ 132bit 编码。优点在于插入的位可防止长“1”或“0”码型,从而能够始终让 CDR 接收到 0/1 跳变保证其正常工作;缺点在于插入的位会造成无效冗余,比如 8bit/10bit 编码的冗余可达到 20%。

位交织 SerDes 方案是指将多个低速串行数据拼接成一条高速串行数据。其优点在于能提高速率且减少数据传输通道数,有利于 PCB 的布局及降低串扰;缺点在于需要额外的时钟、选择器和 CDR 电路。12Gbit/s XAUI (XAUIx4)就是通过这种架构实现的。

由于数据传输速度的不断提高,所以开发出了 SerDes 结构。早期信号传输速度仅为 kbit/s~ Mbit/s 时,并行接口足以处理此类型传输。然而伴随工艺的更新和传输速率的增长,高速信号特别是时钟信号对其他传输线造成的串扰(Crosstalk)日益严重并影响传输质量;同时,应用产品的小型化也需要减少并行走线:因此,使用串行走线并不需要单独时钟线的 Ser Des 结构成为最好选择。

SerDes 架构是目前民用高速接口协议的主流选择。目前国内外各大公司均采用SerDes 架构来实现高速接口产品,如Synopsys 的 USB/PCIe/SATA 等IPIP、华为的 10Gbit/s 企业级 SerDes Xilinx 在2011 年推出的 26Gbit/s SerDes 等。

-

编码器

+关注

关注

45文章

3822浏览量

138408 -

高速接口

+关注

关注

1文章

59浏览量

15022 -

解串器

+关注

关注

1文章

146浏览量

14269 -

串行解串器

+关注

关注

0文章

8浏览量

6826

原文标题:串行/解串器,串列/解串器,SerDes

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

简单认识串行解串器

简单认识串行解串器

评论