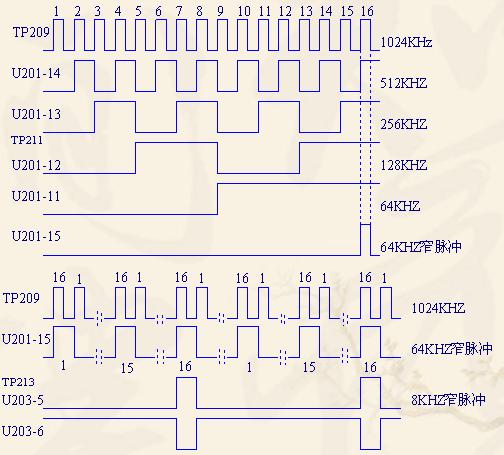

前几天看到有人讨论如何实现分频时钟÷2,÷4,÷8,÷16之间的切换。

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

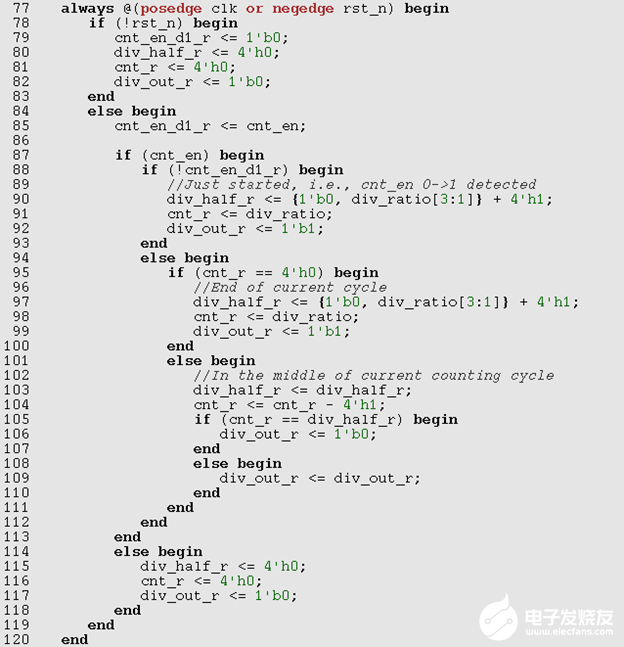

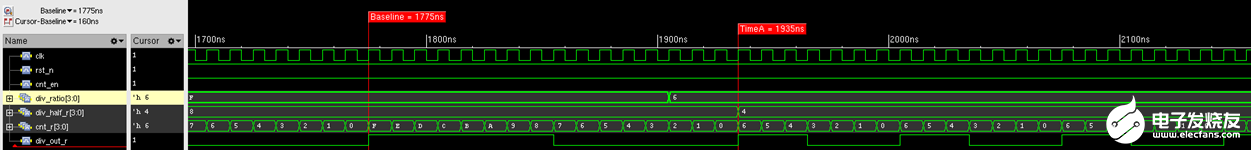

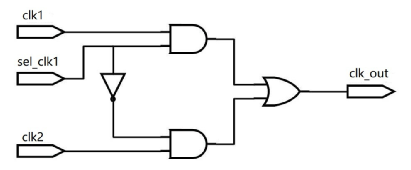

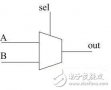

RTL示意如下。这里的关键是要等当前周期跑到最后才切换到新的分频率。这样才能保障输出总是一个完整的周期,不会出现不规则的周期。

这里没有加奇数分频占空比调整。如果希望奇数分频后占空比是50-50,要再加一个negedge DFF,再加一个OR,很简单的,就不赘述了。

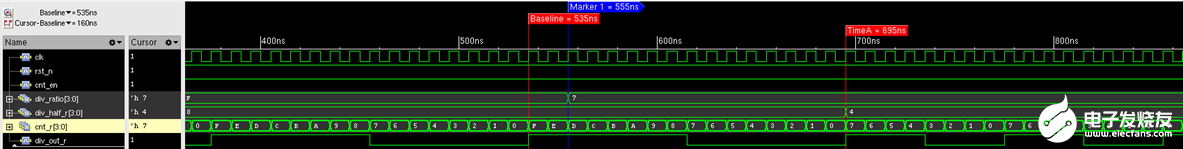

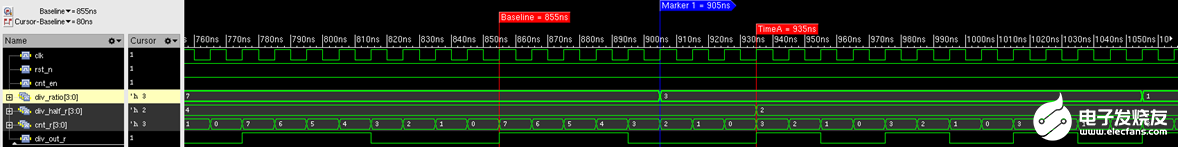

Divide 16 to divide 8

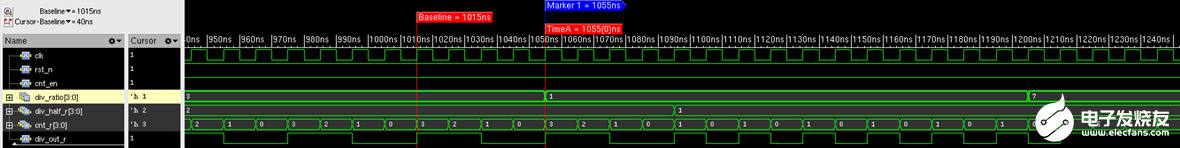

Divide 8 to divide 4

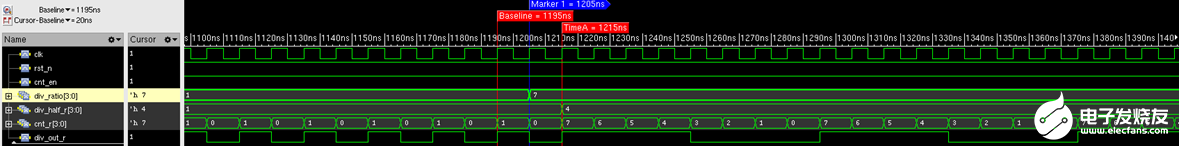

Divide 4 to divide 2

Divide 2 to divide 8

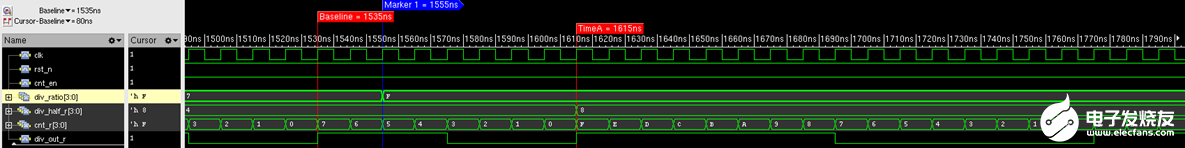

Divide 8 to divide 16

Divide 16 to divide 7

审核编辑:黄飞

-

计数器

+关注

关注

32文章

2292浏览量

96555 -

时钟设计

+关注

关注

0文章

27浏览量

11052 -

控制逻辑

+关注

关注

0文章

14浏览量

2481

发布评论请先 登录

SPARTAN 3E上的时钟分频怎么实现?

时钟切换模式是如何工作的?

基于FPGA的高频时钟的分频和分配设计

如何理解STM32系统时钟和分频

verilog的时钟分频与时钟使能

时钟切换电路设计方案

如何实现分频时钟的切换

如何实现分频时钟的切换

评论