ÊčÓĂĄ°~Ą±ÔËËă·û¶Ô”„bitĐĆșĆœűĐĐÈĄ·ŽŁšÒČłÆÎȘλ·ŚȘ»ò·ŽÏòŁ©ĄŁ

ÀęÈ磏ŒÙÉèÓĐÒ»žö”„bitĐĆșĆaŁŹÄăżÉÒÔŽŽœšÒ»žöĐ”ÄĐĆșĆbŁŹËüÊÇa”Ä·ŽÏòŁș

wire a; wire b = ~a;ÈçčûaÊÇ1ŁŹÄÇĂŽbŸÍÊÇ0Ł»ÈçčûaÊÇ0ŁŹÄÇĂŽbŸÍÊÇ1ĄŁŐâŸÍÊÇËùÎœ”ÄÈĄ·ŽČÙŚśĄŁ

¶Ô¶àbitĐĆșĆœűĐĐÈĄ·ŽÊ±ŁŹÒÀÈ»żÉÒÔÊčÓĂ "~" ÔËËă·ûĄŁ

ÀęÈ磏ŒÙÉèÓĐÒ»žö8bit”ÄĐĆșĆ 'a'ŁŹÄúżÉÒÔŽŽœšÒ»žöĐ”ÄĐĆșĆ 'b'ŁŹËüÊÇ 'a' ”ÄÈĄ·ŽŁș

wire [7:0] a; wire [7:0] b = ~a;

ÔÚŐâžöÀęŚÓÖĐŁŹÈçčû `a` ÊÇ `8'b10101010`ŁŹÄÇĂŽ `b` ŸÍÊÇ `8'b01010101`ĄŁŐâžöČÙŚś»á·Ö±đ¶Ô `a` ”ÄĂżÒ»Î»œűĐĐÈĄ·ŽŁŹČ»ĐèÒȘÊčÓĂŃ»·»òŐß generate ÓïŸäĄŁ

”±È»ŁŹ`generate` șÍ `for` ÓïŸäżÉÓĂÓÚÉúłÉÒ»ŚéœáččÀàËÆ”ÄÄŁżé»òŽúÂëżéĄŁ

ÈçčûÏë¶Ô¶àλÊęŸĘœűĐĐÈĄ·ŽČÙŚśŁŹÒČżÉÒÔÊčÓĂ `for` Ń»·șÍ `generate` ÓïŸäĄŁ

ÒÔÏÂÊÇÊčÓĂ `for` șÍ `generate` ¶Ô¶àλĐĆșĆœűĐĐÈĄ·Ž”ÄÊŸÀęŁș

module invertor #(parameter WIDTH = 8) ( input wire [WIDTH-1:0] a, // ÊäÈëĐĆșĆ output wire [WIDTH-1:0] b // ÊäłöĐĆșĆ ); genvar i; // ÉúłÉ±äÁż, ÔÚgenerateżéÖĐŚśÎȘŒÆÊęÆśÊčÓĂ generate for (i = 0; i < WIDTH; i = i + 1) begin: invert_loop // Öž¶šŃ»·±êÇ© assign b[i] = ~a[i]; // ¶ÔĂżÒ»Î»œűĐĐÈĄ·ŽČÙŚś end endgenerate endmoduleÔÚŐâžöÀęŚÓÖĐŁŹ`for` Ń»·±éÀúÊäÈëÏòÁż `a` ”ÄĂżÒ»Î»ŁŹČą¶ÔĂżÒ»Î»ÊčÓĂ `~` ÔËËă·ûœűĐĐÈĄ·ŽČÙŚśŁŹÈ»șó°ŃœáčûžłÖ”žűÊäłöÏòÁż `b` ”ÄÏàӊλĄŁ

`generate` șÍ `genvar` čŰŒüŽÊÓĂÓÚŽŽœšżÉÉúłÉ”ÄÓČŒțœáč襣

ŐâÖÖŚö·šżÉÒÔŽŠÀíÈÎșÎλżí”ÄÊäÈ룏ֻÒȘœ«Î»żíŚśÎȘČÎÊꎫ”ĘžűÄŁżéŒŽżÉĄŁ

ÉóșË±àŒŁșÁőÇć

-

Verilog

+čŰŚą

čŰŚą

29ÎÄŐÂ

1367äŻÀÀÁż

112418 -

forŃ»·

+čŰŚą

čŰŚą

0ÎÄŐÂ

61äŻÀÀÁż

2744

ÔÎıêÌâŁșVerilog»ùŽĄŁș°ŽÎ»ÈĄ·ŽĄ°~Ą±”ÄÓĂ·š

ÎÄŐÂłöŽŠŁșĄŸÎąĐĆșĆŁșÀŚŽïÍšĐĆ”çŚÓŐœŁŹÎąĐĆč«ÖÚșĆŁșÀŚŽïÍšĐĆ”çŚÓŐœĄż»¶ÓÌíŒÓčŰŚąŁĄÎÄŐÂŚȘÔŰÇ댹ÜłöŽŠĄŁ

·ąČŒÆÀÂÛÇëÏÈ ”ÇÂŒ

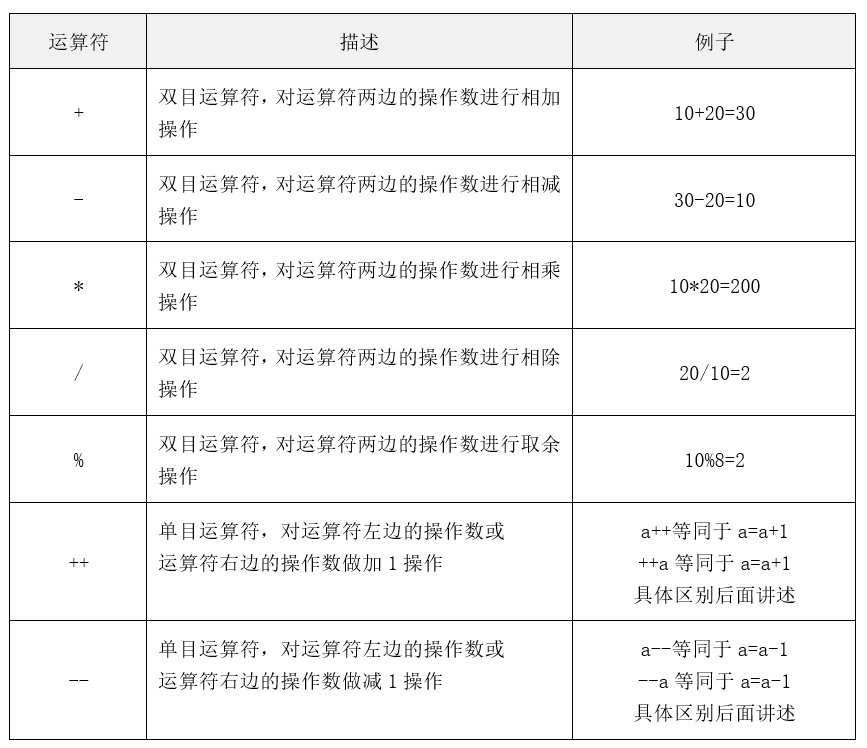

CÓïŃÔÔËËă·û”ÄÊčÓĂ·œ·š

ĄŸžúÎÒѧ”„ÆŹ»úCÓïŃÔĄżÏêœâÔËËă·ûșͱíŽïÊœ”ÄλÔËËă·û

CÓïŃÔÔËËă·ûÓĆÏÈŒ¶ŁšłŹÏêÏžŁ©

Âߌ”ç·ÓëÂߌÔËËă·û

2.7 pythonÔËËă·û

ÌőŒțÔËËă·ûÊÇÊČĂŽ_ÌőŒțÔËËă·ûÓĐÄÄĐ©

”„ÄżÔËËă·ûÊÇÊČĂŽ_”„ÄżÔËËă·ûÓĐÄÄĐ©

ËőŒőÔËËă·û”Ä耳ÌÊ”ÀęœČœâ

ÇłÎöMySQLÖДĞśÀàÔËËă·û

pythonÔËËă·ûÊÇÊČĂŽ

ÊČĂŽÊÇÔËËă·ûÖŰÔŰ

ÌőŒțŁšÈęÔȘŁ©ÔËËă·û

ÊČĂŽÊÇÒÆλÔËËă·û

cÓïŃÔÔËËă·ûŒ°ÀęÌâ

CÓïŃÔ”ÄÔËËă·û

ÊčÓĂĄ°~Ą±ÔËËă·û¶Ô”„bitĐĆșĆœűĐĐÈĄ·Ž

ÊčÓĂĄ°~Ą±ÔËËă·û¶Ô”„bitĐĆșĆœűĐĐÈĄ·Ž

ÆÀÂÛ