作者:IAR

在嵌入式软件开发中,利用完整的应用跟踪,可为开发人员分析其产品行为提供无限的可能性。通过对应用程序的全面了解,他们可以跟踪每一条指令,看看他们的应用程序是否按照预期运行,或者是否出现错误或漏洞。那么,如何才能最大化地利用现有可用的RISC-V跟踪呢?

什么是跟踪?

与传统的通过设置断点、printf等进行调试相比,跟踪更像是在不打扰的情况下观察你的应用程序。基本上,开发人员可以在不干扰程序的情况下观察整个程序的工作情况。跟踪包括完整的指令执行流程(不需要printf也不需要UART),一旦跟踪数据被捕获,你可以快速追溯,并隔离异常和硬故障。

这使得寻找那些罕见的、依赖于执行顺序的漏洞变得更加容易,因为这提供了一串线索:程序执行是怎么样的,按什么顺序执行的。这使开发人员能够准确地了解它们是如何以及为什么总是会停在一串特殊的代码上。你可以迅速发现异常和硬故障,进而发现那些罕见的、依赖于执行顺序的错误。如果没有跟踪,当你的程序出现崩溃,就很难重现实际发生的情况。

然而,跟踪不仅仅是为了发现错误。跟踪还可以进行代码剖析、代码覆盖等,你可以实时了解你的设备的行为。性能和覆盖率监测是强大的功能,当你有跟踪功能时,就可以实现这些强大的功能。如果你的带宽够宽,甚至可以将实时跟踪流整合到你的调试器中。

RISC-V的跟踪技术

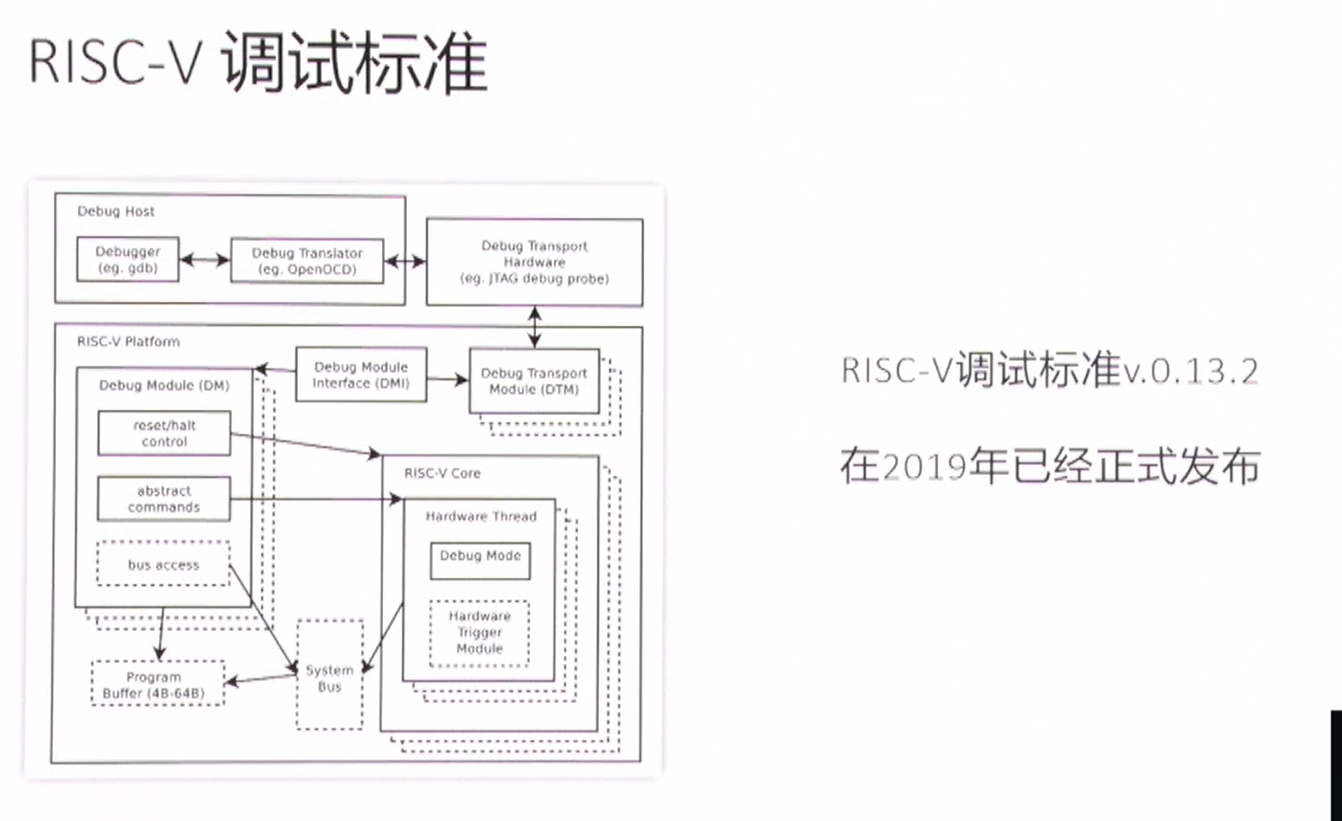

RISC-V组织的主要关注点之一是为RISC-V制定标准化的规范。对所有RISC-V成员开放的各种工作小组,目前正专注于开发制定这些规范。其中一个例子是处理器跟踪工作组,该工作组在2020年2月批准发布了处理器跟踪规范。另一个例子是Nexus跟踪小组,该小组致力于研究如何使用Nexus IEEE-ISTO 5001?标准针对RISC-V内核定义的跟踪技术。

这类工作将持续进行,因为必须考虑跟踪标准的所有方面。其中,包括跟踪控制的输出格式。最低的目标是与更成熟的架构的现有标准看齐。如果RISC-V跟踪规范做得好,它将使现有的跟踪查看器、硬件跟踪探头和跟踪分析工具易于采用。目前已经有一些实现的方案,但RISC-V架构应该在从物联网到服务器的每个设备中都有跟踪,即使是简单、标准的跟踪也比完全没有跟踪好。

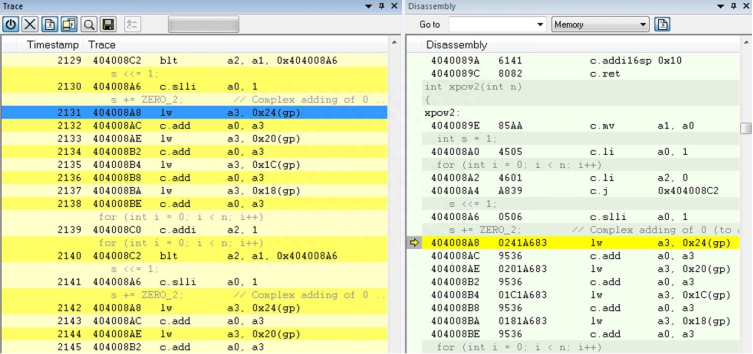

图1 来自一个RISC-V设备的跟踪

看清每条指令

软件开发工具中集成对跟踪的支持增强了日常的代码开发/调试。跟踪应该是设计人员日常环境中固有的一部分,而不应该是事后分析的东西。因此,你可以写代码并运行,看看是如何到达当前的执行点的。通过快速追溯、隔离异常和硬故障的功能,你可以直接迭代并获得良好的代码质量。你还可以找到依赖于执行顺序的漏洞,并找到可以与你的程序流程相关联的功耗测量值。所有这些分析也可以在具有挑战性和复杂依赖性的多核环境下进行。

在寻找一个漏洞时,翻阅捕获的跟踪的难度无异于大海捞针。在短短几秒钟的执行时间里,可以产生数以亿计的指令。因此,极为重要的是,规范将提供足够的触发器,以便能够将捕获限制在特定区域。先进的导航和搜索功能是必不可少的,如果你的编译器/调试器工具提供该功能,则可以使用跟踪触发器将跟踪数据限制在你需要的范围内。

为什么需要跟踪?

在设备中植入跟踪单元,让你有可能在产品运行时进行非侵入性的跟踪。因为即使添加非常底层的调试打印输出,也会改变应用程序的时间,并掩盖其真实行为。

有许多方法可以捕捉和获得从设备中输出的跟踪数据:

l 顺序排列

- 足够的PC采样跟踪(对统计代码剖析研究有好处)

- 轻型仪器、实时操作系统(RTOS)监控、变量跟踪等

- 配备优秀的探针,有可能达到几兆字节/秒的速度

l 高速并行接口(4至16位的双边接口)

- 捕获一切(时钟速度可以很高)

- 通过控制流转移时留下的信息进行跟踪

- 为你执行的每一条指令提供保证

- 指令执行过程信息实时存储在调试器探针上

l RAM缓冲区

- 要么是小的专用RAM,要么与系统内存共享

- 即使是4KB的跟踪RAM也能提供足够的功能,真正发挥作用

l 高速排列

- 速度为10Gbits/s或更高

- 主要适用于较大的、复杂的系统

l 通过功能接口进行跟踪(USB3.0提供了超高带宽!)

- 使用案例有限——对小型物联网设备来说不是一个选择

调试异常情况

通过在日常工作中使用跟踪,你可以真实看到应用程序是如何运行的。你可以检查程序流,直到一个特定的状态,如应用程序崩溃,然后使用跟踪数据来定位问题的起源。

异常或未处理的故障可以由指针问题、非法指令或数据中止引起。通常,当这种情况发生时,你的堆栈(和函数调用信息)会被毁掉,但通过跟踪,你可以获得完整的应用程序历史记录。跟踪数据对于定位那些显现不规则且零星发生的编程错误也很有用。这可以帮助发现价值“百万美元”的漏洞。

硬件和软件工具的集成

获得尽可能高质量的代码的最佳方法是将跟踪分析能力整合到你的日常开发环境中。如果你能在每次部署变化时验证程序时序和正确性,那么将复杂的漏洞推给后期系统验证甚至客户的风险就会大大降低。最好的解决方案是拥有像跟踪调试探针这样的硬件工具,它可以在你的集成开发环境中与软件工具无缝协作。例如,IAR提供跟踪探头I-jet Trace,它与完整的C/C++编译器和调试器工具链IAR Embedded Workbench完全集成。

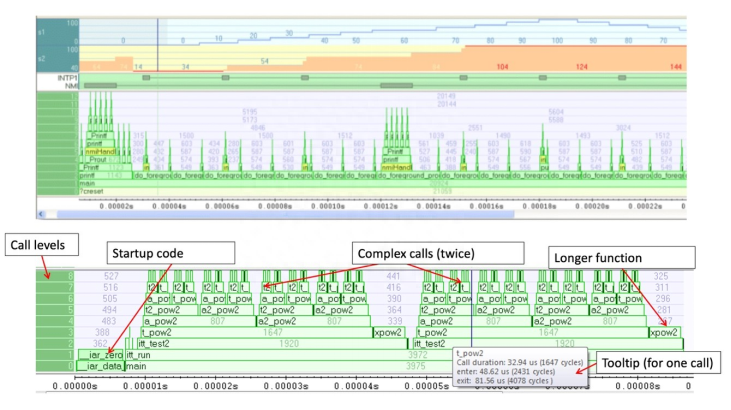

I-jet Trace解锁了IAR Embedded Workbench 集成开发环境中的一些高级功能。在图2中,你可以看到几个高级视图功能的例子,上面是时间轴,下面是代码堆栈。这显示的是运行中的程序正在进行复杂的函数调用,并且中断也在同步触发。蓝色部分显示的是数据跟踪,这样你就可以获得仪表化的显示,并看到RTOS的切换等。下面的详细图显示了启动代码的运行情况——有复杂的调用,还有一些较长和较短的函数,甚至还有一个工具提示来优化其中一个调用的代码。

图2 结合调用堆栈和中断以及变量记录的时间轴实例

代码质量

但是,跟踪不仅仅是为了发现漏洞。它还可以帮助你监控你的应用程序——它是否按照预期运行?集成性能监控是使用跟踪的主要好处之一,因为它可以帮助你了解应用程序执行时间都花在哪里了,是否受到中断风暴的影响,是否有时反应不够快等等。

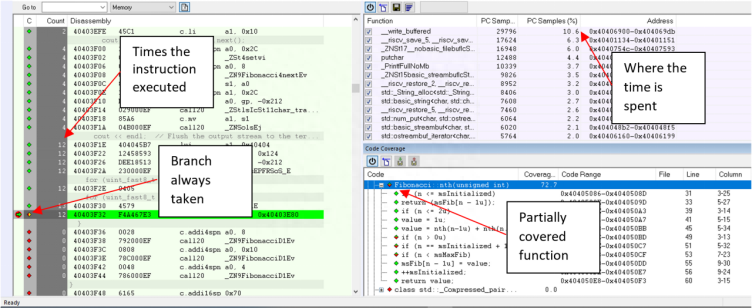

代码覆盖率也是一个可以用跟踪实现的功能(图3展示了它在IAR Embedded Workbench中的样子)。这可以用来证明代码至少被运行过一次,查找出未运行的代码,显示测试的缺陷等等。功能安全认证强烈建议将代码覆盖率作为提高质量的一个手段。静态代码分析工具是对跟踪分析器一个很好的补充。这可以确保代码符合特定行业的标准和最佳编程实践。除了覆盖率,该工具还可以收集每个单独指令的执行次数。例如,有些指令块被执行了4次,有些被执行了12次。很明显,没有被覆盖的代码执行了0次。

图3 跟踪也可以审查代码覆盖率

总结

跟踪提供了各种有益的数据源,如收集数据或协助开发人员将信息过滤成实际的知识和见解。用不同的跟踪查看器进行可视化和分析,可以创建一个产品如何运行及其动态行为的真实描述,为开发人员提供必要的信息,以跟踪那些很难,甚至不可能通过其他手段捕捉的复杂漏洞。通过在日常开发中加入跟踪,开发人员可以加速软件开发过程,提高软件质量。

审核编辑 黄宇

-

跟踪技术

+关注

关注

0文章

10浏览量

3263 -

RISC-V

+关注

关注

46文章

2633浏览量

49244

发布评论请先 登录

UltraSoC宣布提供业界首款RISC-V处理器跟踪IP产品

rIsc-v的缺的是什么?

为什么选择RISC-V?

RISC-V架构

2023 RISC-V中国峰会:RISC-V深圳技术分享会(同期会议)

UltraSoC宣布推出业界首款支持RISC-V的处理器跟踪技术

RISC-V规范的演进 RISC-V何时爆发?

什么是RISC-V?RISC-V的关键技术

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

如何有效使用RISC-V的跟踪技术

如何有效使用RISC-V的跟踪技术

评论