жБВЅЮЪД№ећРэШчЯТЃЌЙЉДѓМвВЮПМЁЃ

ЯжГЁРДВЛМАЬсЮЪЁЂЛђДэЙ§жБВЅЕФЙлжкПЩвддкКѓЬЈСєбдЬсЮЪЃЌЮвУЧЛсзЊИјЯрЙиММЪѕШЫдБНјааНтД№ЁЃ

вВЛЖгДѓМвОЭХрбЕБОЩэЕФИФНјвтМћИјЮвУЧСєбдЃЌЮвУЧЛсИљОнДѓМвЕФЗДРЁЕїећНёКѓЕФХрбЕМЦЛЎЁЃ

Q

PCBжаШчКЮПижЦзшПЙЃЌзшПЙЕФПижЦКЭФФаЉвђЫиЯрЙиЃП

Д№ЃК

PCB ВМОжКЭВуЖбЕўЃКзшПЙЪмЕН PCB ВМОжКЭВуЖбЕўЕФгАЯьЁЃР§ШчЃЌаХКХЯпгыЕиЦНУцжЎМфЕФОрРыЁЂаХКХЯпжмЮЇЕФв§НХКЭЭЬюГфЕШЖМЛсгАЯьзшПЙЁЃвђДЫЃЌдкНјаа PCB ВМОжЪБЃЌашвЊПМТЧетаЉвђЫиРДПижЦзшПЙЁЃ

ДЋЪфЯпЬиадзшПЙЃКзшПЙгыДЋЪфЯпЕФЬиадВЮЪ§гаЙиЃЌШчДЋЪфЯпЕФПэЖШЁЂМфОрЁЂИпЖШЁЂНщЕчГЃЪ§ЕШЁЃИљОнЫљЪЙгУЕФ PCB ВФСЯКЭЩшМЦвЊЧѓЃЌПЩвдЪЙгУ Allegro ШэМўЬсЙЉЕФЙЄОпРДМЦЫуКЭЩшжУДЋЪфЯпЕФЬиадзшПЙЁЃ

ВюЗжЯпКЭЦЅХфзшПЙЃКЖдгкВюЗжаХКХЯпЃЌашвЊБЃГжВюЗжзшПЙЕФЦЅХфЃЌвдШЗБЃаХКХЕФЦНКтКЭвжжЦЙВФЃдыЩљЁЃдк Allegro ШэМўжаЃЌПЩвдЪЙгУВюЗжЯпдМЪјРДЩшжУВюЗжзшПЙЕФвЊЧѓЁЃ

Q

Allegro X КЭ Allegro 17.4ЁЂAllegro 22.1 ЕФЧјБ№ЃП

Д№ЃКAllegro X ЪЧаТвЛДњЕФ Allegro PCB ЩшМЦШэМўЃЌЪЧМЏКЯСЫЧАЖЫЁЂКѓЖЫЩшМЦЃЌПтЁЂЪ§ОнЙмРэЁЂEE ЗжЮіЕШЮЊвЛЬхЕФзлКЯадЦНЬЈЃЈPCB DeisgnerЁЂSystem CaptureЁЂPulseЁЂPCB LibrarianЁЂDesign Workbench...)ЁЃ

Жј Allegro 17.4 жЛЪЧ Allegro ШэМўЕФвЛИіАцБОКХЁЃФПЧАЕФАцБОвбОИќаТЕН 22.1ЁЃ

Allegro X ЪЧдк 22.1 АцБОЯТЗЂВМЕФЃЌвђДЫЖдБШ 17.4 АцБОЃЌГ§СЫЬсЙЉећКЯЕФЦНЬЈжЎЭтЃЌИќЬсЙЉСЫИќЖрИпаЇЁЂНјНзЕФЙІФмЃЌР§Шч ConvertЁЂIn-Design AnalysisЁЂVoid spacing control ЕШЁЃ

ШчЙћвЊСЫНтЯъЯИЬиадЃЌЧыСЊЯЕЮвУЧЃКspb_china@cadence.comЁЃ

Q

дк Allegro ШэМўжаЃЌШчКЮеыЖд DDR4 ЕФЩшМЦНјааЙцдђЩшжУвдМАШчКЮЪЙгУЙцдђдМЪјВМЯпЃП

Д№ЃКЪзЯШЃЌДђПЊ Allegro ШэМўВЂМгди DDR4 ЩшМЦЮФМўЃК

дкВЫЕЅРИжабЁдё Constraints -> Physical -> Constraint ManagerЃЌДђПЊЙцдђЙмРэЦїМўЃЌДДНЈдМЪјЙцдђЁЃЖдгкDDR4 ЩшМЦЃЌвЛаЉГЃМћЕФдМЪјЙцдђАќРЈЪБађЙцдђЁЂВМОжЙцдђКЭаХКХЭъећадЙцдђЁЃ

ЪБађЙцдђЃКдк ЁАTimingЁБ бЁЯюПЈЯТЃЌПЩвдЩшжУЪБжгКЭЪ§ОнаХКХЕФЪБађЙцдђЃЌШчЪБжгЦЕТЪЁЂЪБжгбгГйЁЂЪ§ОнДЋЪфЪБађЕШ

ВМОжЙцдђЃКдк ЁАPlacementЁБ бЁЯюПЈЯТЃЌПЩвдЩшжУDDR4аОЦЌЕФВМОжЙцдђЃЌШчаОЦЌЮЛжУЁЂв§НХЗжХфЕШ

аХКХЭъећадЙцдђЃКдк "Signal IntegrityЁА бЁЯюПЈЯТЃЌПЩвдЩшжУаХКХЕФЕчЦјЬиадЙцдђЃЌШчаХКХЗљЖШЁЂДЋЪфЯпЬиадзшПЙЕШЁЃ

ИљОн DDR4 ЕФЙцИёКЭЩшМЦвЊЧѓЃЌж№ИіЩшжУЫљашЕФдМЪјЙцдђЁЃПЩвдЭЈЙ§ЕуЛї"Add"АДХЅРДЬэМгаТЕФдМЪјЙцдђЃЌВЂИљОнашвЊНјааЩшжУЁЃ

дкЩшжУдМЪјЙцдђЪБЃЌПЩвдЪЙгУAllegroЬсЙЉЕФдМЪјФЃАхЛђздЖЈвхдМЪјЃЌОпЬхИљОн DDR4 ЕФЙцИёКЭЩшМЦвЊЧѓРДОіЖЈЁЃ

ЭъГЩдМЪјЙцдђЕФЩшжУКѓЃЌПЩвдЖдЩшМЦНјааВМЯпЙцдђЁЃдкВМЯпЙ§ГЬжаЃЌAllegro ЛсИљОнЩшжУЕФдМЪјЙцдђНјааВМЯпЃЌШЗБЃЩшМЦТњзудМЪјвЊЧѓЁЃ

ашвЊзЂвтЕФЪЧЃЌDDR4 ЩшМЦЕФдМЪјЙцдђЩшжУашвЊИљОнОпЬхЕФЩшМЦвЊЧѓКЭ DDR4 ЕФЙцИёРДШЗЖЈЃЌНЈвщВЮПМDDR4 ВњЦЗЪжВсКЭ Allegro ШэМўЕФЯрЙиЮФЕЕРДСЫНтИќЖрЯъЯИаХЯЂКЭВйзїВНжшЁЃ

Q

ШчКЮдк Allegro ШэМўжаЖдзшПЙНјааЩшжУЃП

Д№ЃКДђПЊ Allegro ШэМўВЂМгди PCB ЩшМЦЮФМўЃК

дкВЫЕЅРИжабЁдё Constraints -> Physical -> Constraint ManagerЃЌДђПЊЙцдђЙмРэЦїЁЃ

дкЙцдђЙмРэЦїжаЃЌбЁдё ЁАSignal IntegrityЁА бЁЯюПЈЁЃдкИУбЁЯюПЈЯТЃЌПЩвдЩшжУаХКХЕФЕчЦјЬиадЙцдђЃЌАќРЈзшПЙЁЃ

ЕуЛїЁАAddЁБАДХЅЃЌЬэМгаТЕФаХКХЙцдђЁЃдкЕЏГіЕФЖдЛАПђжаЃЌбЁдё"Net"ЃЌШЛКѓбЁдёвЊЩшжУзшПЙЕФаХКХЯпЁЃ

дкЙцдђЩшжУжаЃЌПЩвджИЖЈаХКХЯпЕФзшПЙЙцИёЁЃПЩвдбЁдёЙЬЖЈзшПЙжЕЃЌвВПЩвдбЁдёЭЈЙ§ЖЈвхДЋЪфЯпВЮЪ§РДМЦЫузшПЙЁЃ

ЭъГЩзшПЙЩшжУКѓЃЌПЩвдНјааВМЯпКЭЗТецЃЌAllegro ЛсИљОнЩшжУЕФзшПЙЙцдђРДВМЯпВЂНјаааХКХЭъећадЗжЮіЁЃ

ашвЊзЂвтЕФЪЧЃЌзшПЙЕФЩшжУашвЊИљОнОпЬхЕФЩшМЦвЊЧѓКЭЫљЪЙгУЕФ PCB ВФСЯРДШЗЖЈЃЌНЈвщВЮПМ PCB ВФСЯЕФЙцИёКЭ Allegro ШэМўЕФЯрЙиЮФЕЕРДСЫНтИќЖрЯъЯИаХЯЂКЭВйзїВНжшЁЃ

Q

вЛЗндРэЭМЯТШчЙћгаЖрЗн .dsn ЮФМўЃЌШчКЮЗжБ№ЕМГіЭјБэЃП

Д№ЃКДђПЊдРэЭМЩшМЦЙЄГЬЃЌдк OrCAD Capture жабЁдёвЊЕМГіЭјБэЕФ .dsn ЮФМўЃК

дкВЫЕЅРИжабЁдё Tools -> Create NetlistЁЃ

дк "Output Options" ВПЗжЃЌбЁдё "Create a new netlist file"ЃЌШЛКѓЮЊУПИі.dsnЮФМўжИЖЈВЛЭЌЕФЕМГіЭјБэЮФМўУћКЭТЗОЖЁЃ

дк "Output File" ВПЗжЃЌЕуЛї "Browse" АДХЅбЁдёЕМГіЭјБэЕФЮФМўУћКЭТЗОЖЁЃ

ЕуЛї "OK" ПЊЪМЕМГіЭјБэЁЃжиИДвдЩЯВНжшЮЊУПИі.dsnЮФМўНјааЭјБэЕМГіЁЃ

ЭЈЙ§вдЩЯВНжшЃЌПЩвдЮЊУПИі.dsnЮФМўЗжБ№ЕМГіЭјБэЃЌШЗБЃУПИіЮФМўЖМгаЖдгІЕФЭјБэЮФМўЁЃЧызЂвтЃЌШЗБЃУПИі.dsnЮФМўдкЕМГіЭјБэЪБЖМЪЙгУВЛЭЌЕФЮФМўУћКЭТЗОЖЃЌвдБмУтЛьЯ§ЛђИВИЧЁЃ

-

дРэЭМ

+ЙизЂ

ЙизЂ

1329ЮФеТ

6415фЏРРСП

241065 -

pcb

+ЙизЂ

ЙизЂ

4371ЮФеТ

23532фЏРРСП

410987 -

зшПЙ

+ЙизЂ

ЙизЂ

17ЮФеТ

974фЏРРСП

47543 -

RK3588

+ЙизЂ

ЙизЂ

7ЮФеТ

428фЏРРСП

6016

ЗЂВМЦРТлЧыЯШ ЕЧТМ

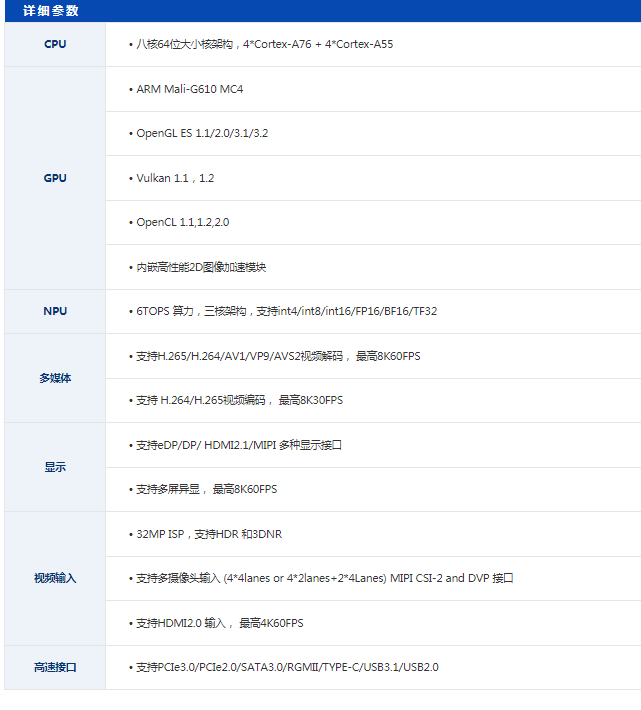

RK3588жїАхЃКЖрдЊГЁОАЕФгВКЫЁАаОЁБСІСП

RK3588 EVBПЊЗЂАхдРэЭМНВНтЁОАЫЁП RK3588 power Tree

RK3588 EVBПЊЗЂАхдРэЭМНВНтЁОЦпЁП

RK3588 EVBПЊЗЂАхдРэЭМНВНтЁОСљЁП

RK3588 EVBПЊЗЂАхдРэЭМНВНтЁОЮхЁП

RK3588 EVBПЊЗЂАхдРэЭМНВНтЁОвЛЁП

PET_RK3588_COREКЫаФАх

RK3588 ДгдРэЭМЧЈвЦЭЌВНЕН PCB ЕФЙиМќВйзїМАММЧЩ

RK3588 ДгдРэЭМЧЈвЦЭЌВНЕН PCB ЕФЙиМќВйзїМАММЧЩ

ЦРТл