近日,PCI 特别兴趣小组 (PCI-SIG) 将在圣克拉拉举办其年度开发者大会。业界卓越的扩展总线的开发人员和生态系统成员的年度聚会为硬件开发人员提供了大量的技术会议,但对于局外人来说,来自该展会的最重要的新闻往往是 SIG 的年度更新状态生态系统。今年也不例外,他们更新了 PCIe 7.0 的开发状态,以及 PCIe 6.0 的采用和布线工作。

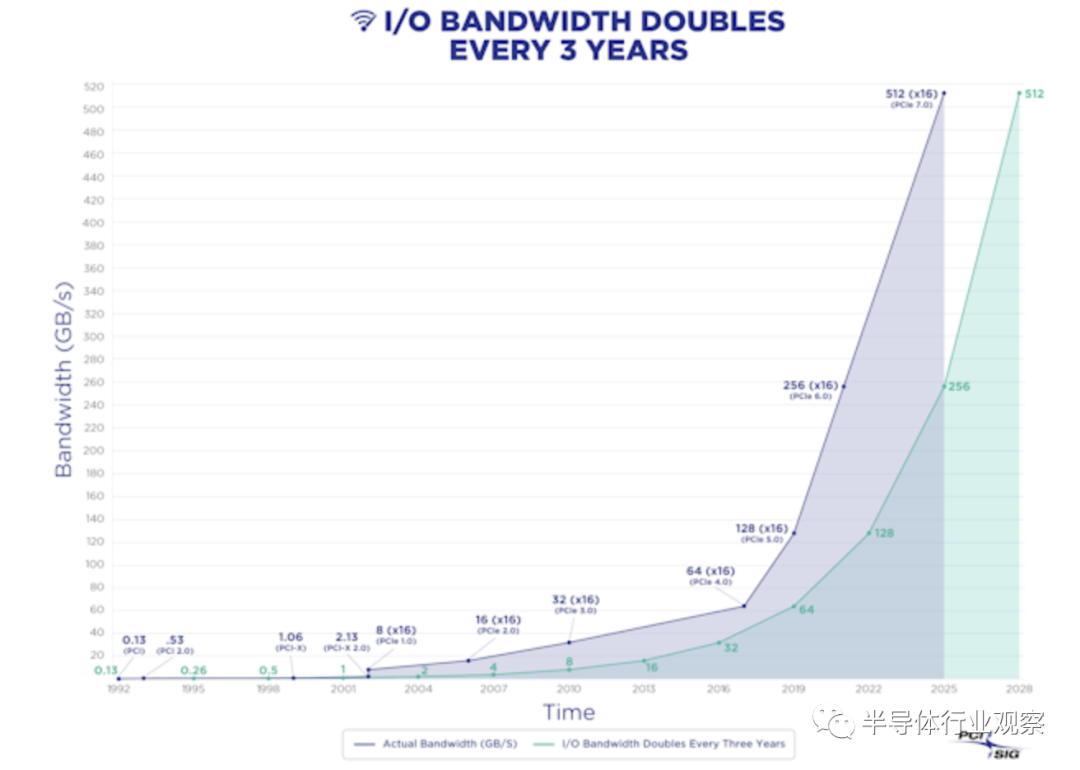

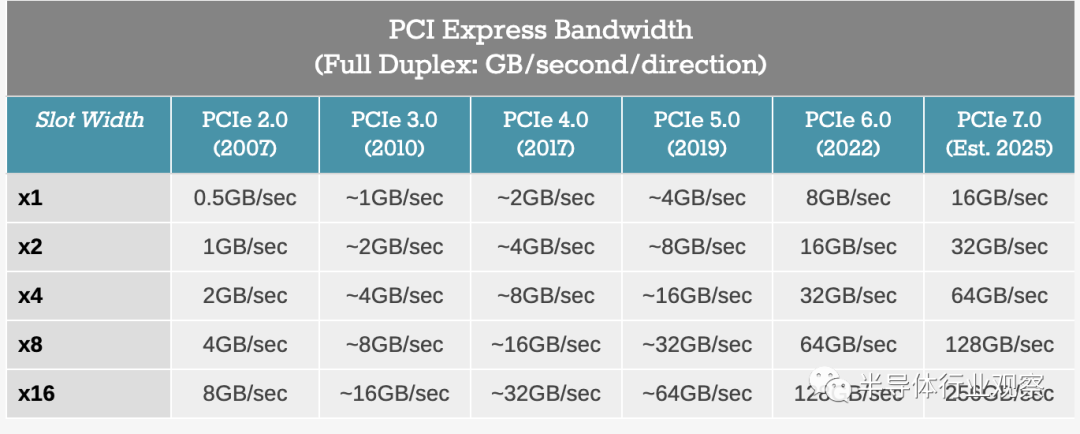

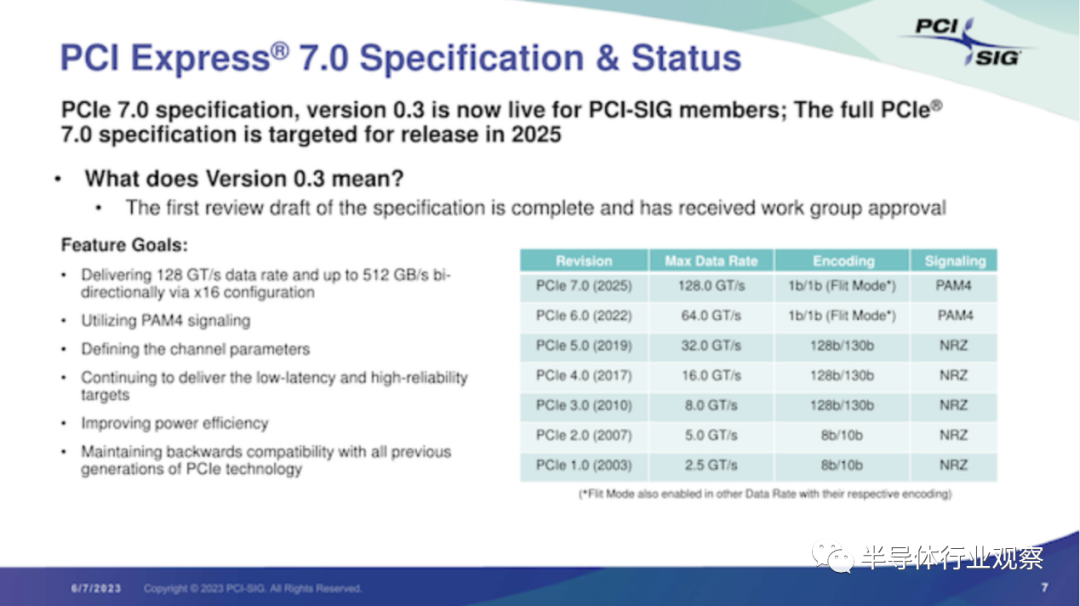

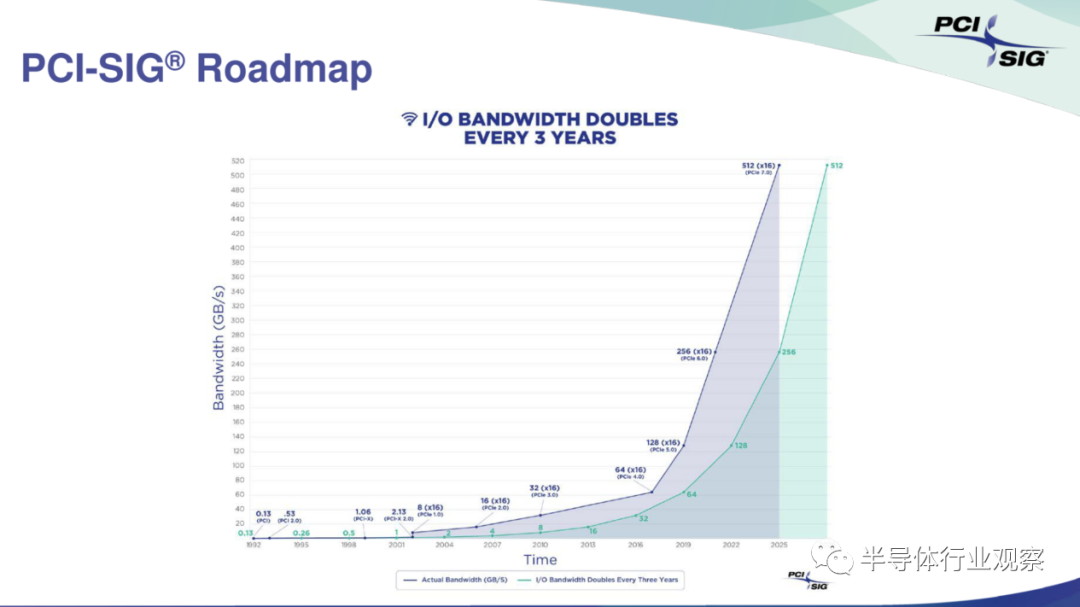

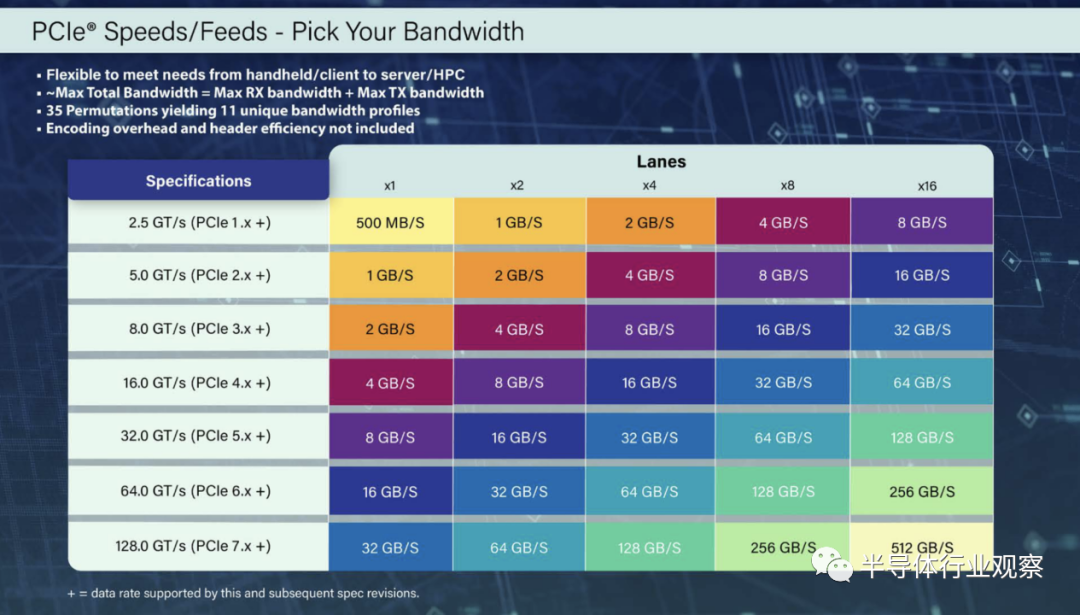

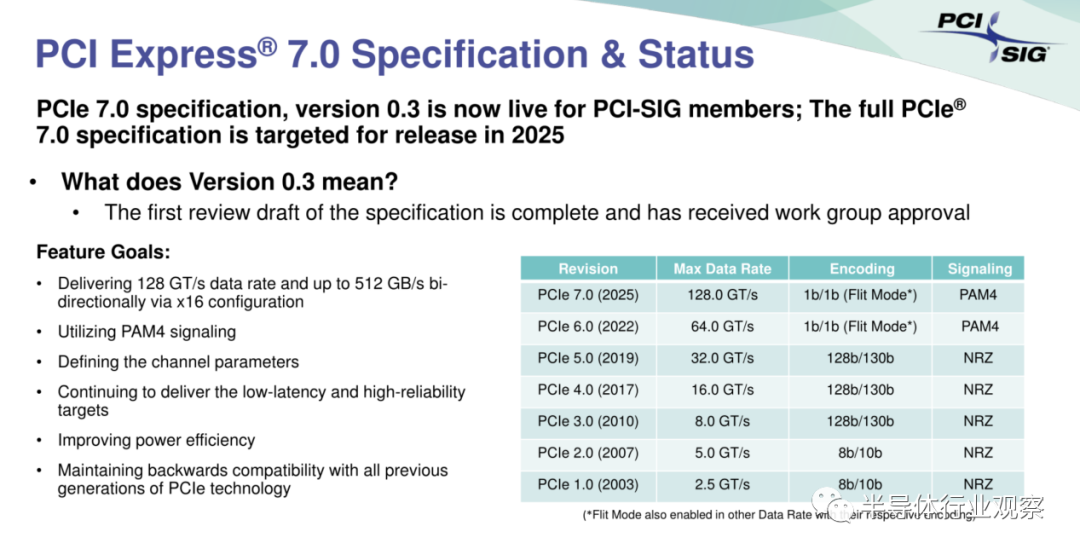

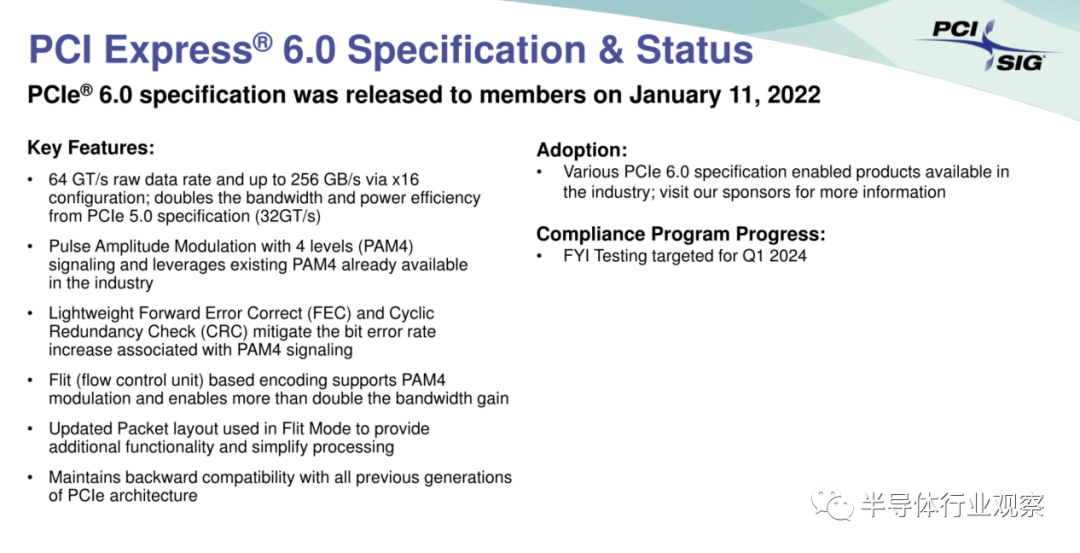

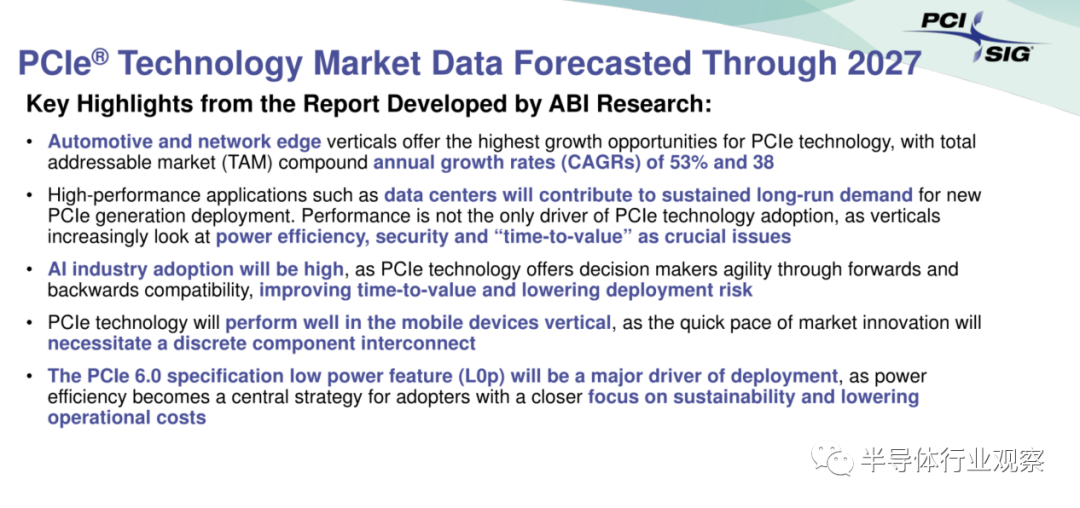

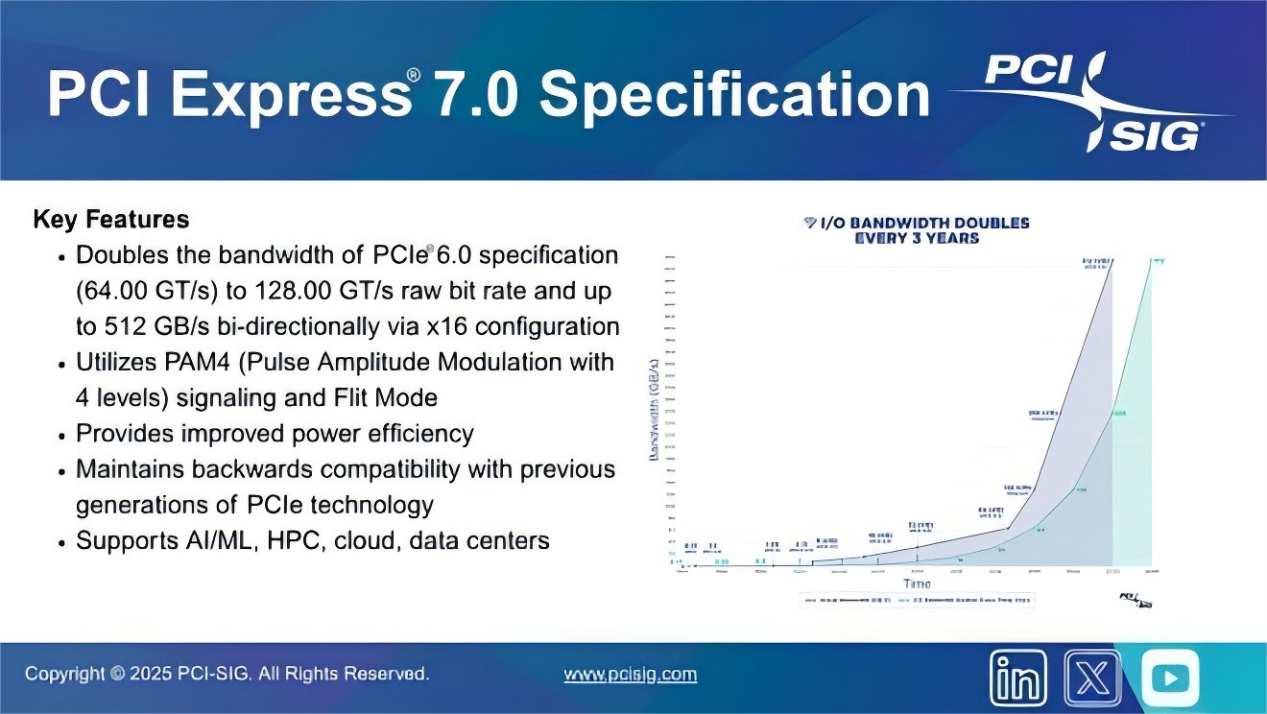

随着PCI Express 6.0 于去年初完成,PCI-SIG 迅速开始着手开发下一代 PCIe 7.0,这在去年的开发者大会上宣布。针对 2025 年的发布,PCIe 7.0 的目标是再次将 PCIe 设备的可用带宽量增加一倍,使单通道的全双工双向带宽高达 16GB/秒——而流行的 x16 插槽在单通道中高达 256GB/秒每个方向。

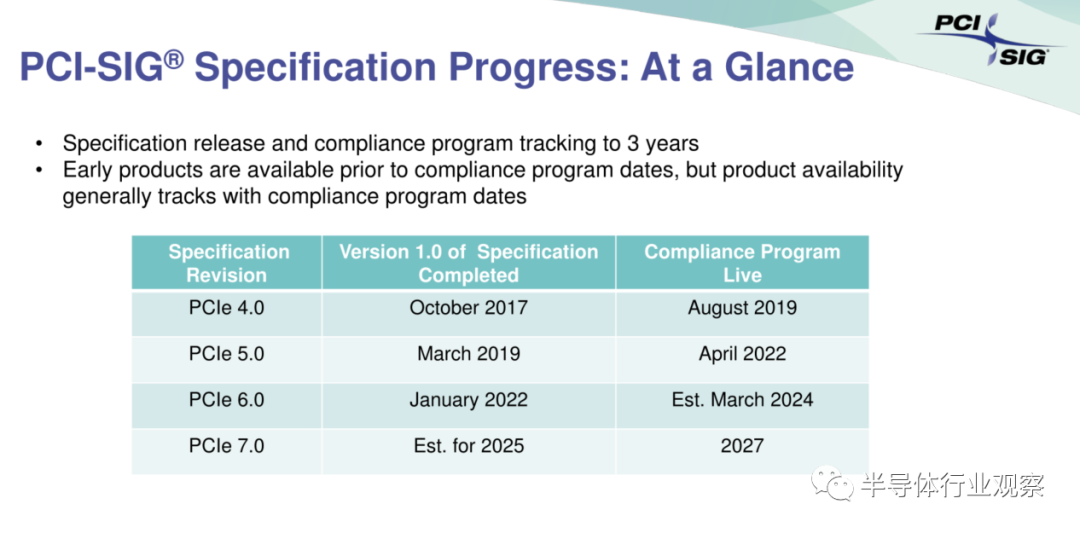

在去年发布公告时,PCIe 7.0 的早期工作才刚刚开始。对于 2023 年会议,PCI-SIG 已经完成了规范的第一个草案版本 0.3 的发布,并准备分发给该组织的成员,这标志着该标准的下一步发展。

PCI-SIG 标准的早期草案往往不关注公共技术细节,PCIe 7.0 v0.3 在这方面也不例外。因此,我们对规范本身知之甚少,而这些规范本身并没有概述去年宣布的目标。

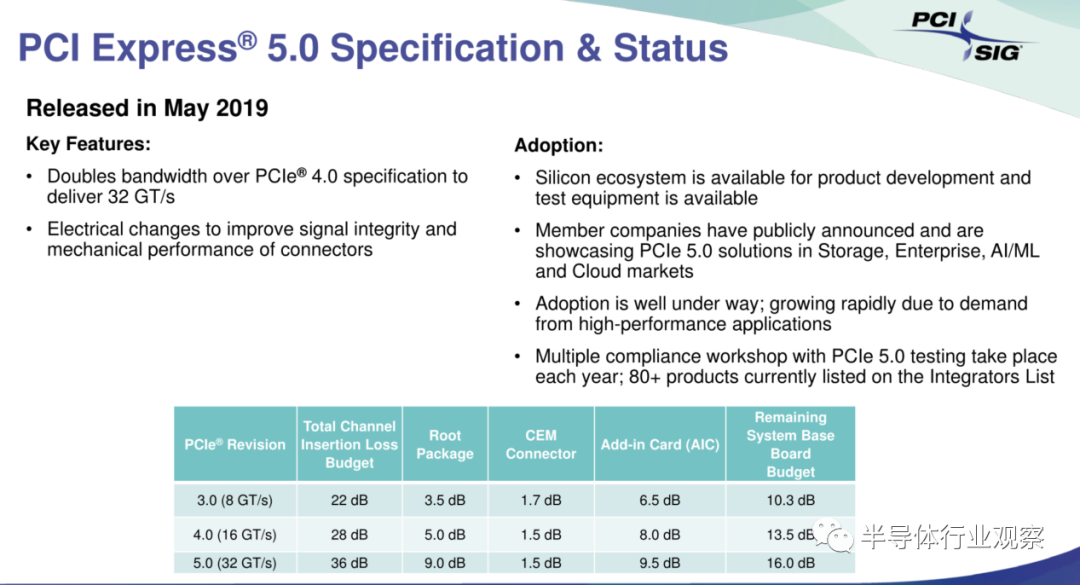

尽管如此,规范初稿的完成仍然很重要,因为它表明该小组已成功开发出更快的 PCIe 通信所需的核心技术基础。这并非易事,因为 PCIe 7.0 需要将物理层的总线频率加倍,这是 PCIe 6.0 使用 PAM4 信令回避的一项重大发展。即便如此,在改进数据信号方面也没有什么是免费的,但是对于 PCIe 7.0,PCI-SIG 可以说是回到了硬模式开发,需要再次改进物理层——这次是为了让它能够在大约30GHz。

在电气方面,PCIe 7.0 与其前身一样坚持使用 PAM4 + FLIT 编码。因此,下一个标准在物理层开发上的花费,将主要用于逻辑层的开发。

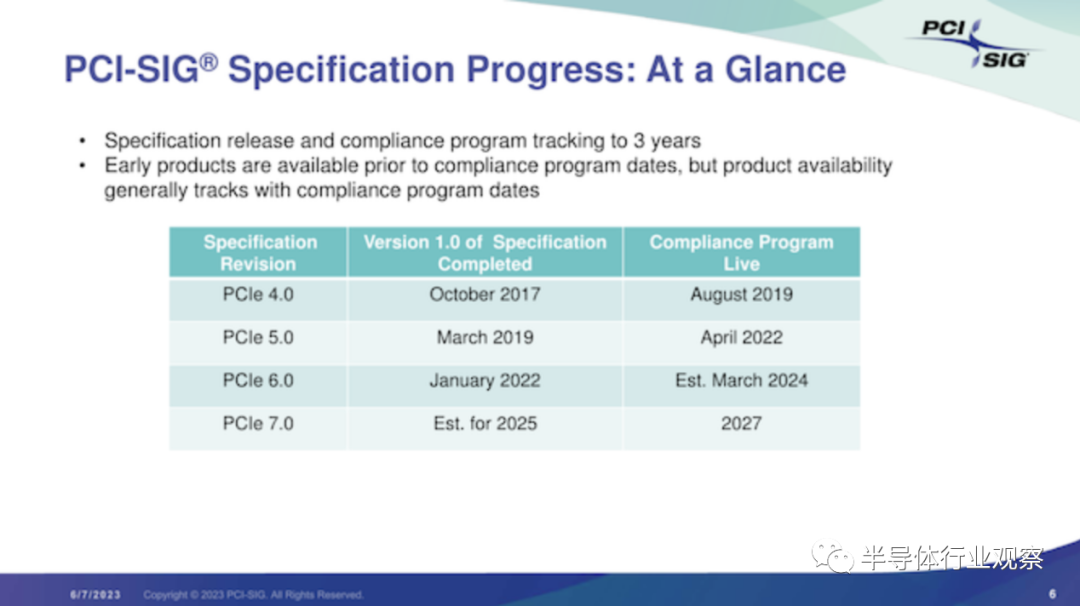

最终,PCI-SIG 的标准节奏基于三年的开发周期。因此,今年的公告草案对于该集团来说如期而至,预计它还有两年的发展时间。假设其余的草案工作进展顺利,PCI-SIG 预计将在 2025 年完成 PCIe 7.0 规范。

反过来,该规范的合规性计划应在 2027 年启动并运行。合规性计划是硬件可用性的功能晴雨表,因为在使用新规范的任何大型商业硬件发货之前,合规性测试和认证实际上是必要的. 除了少数例外,这些通常需要 2 到 2.5 年的时间才能组装起来。所有这一切都表明,首批商用 PCIe 7.0 产品预计至少要到 2027 年——从现在起五年——这表明,在这个初始草案之后,PCIe 7.0 仍有很多工作要做。

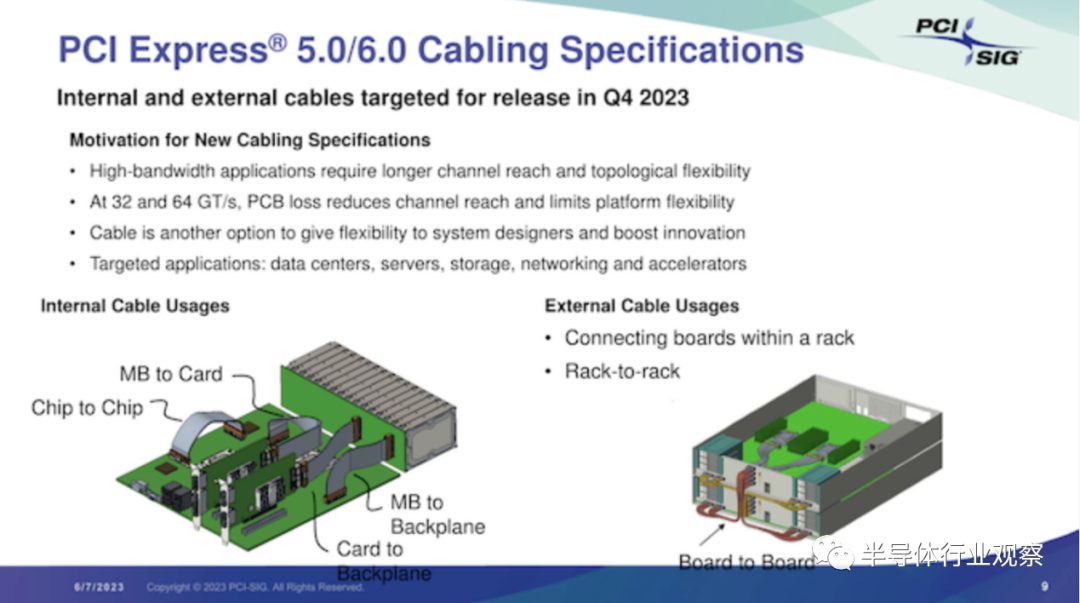

PCIe 5.0/6.0 布线将于 2023 年末推出

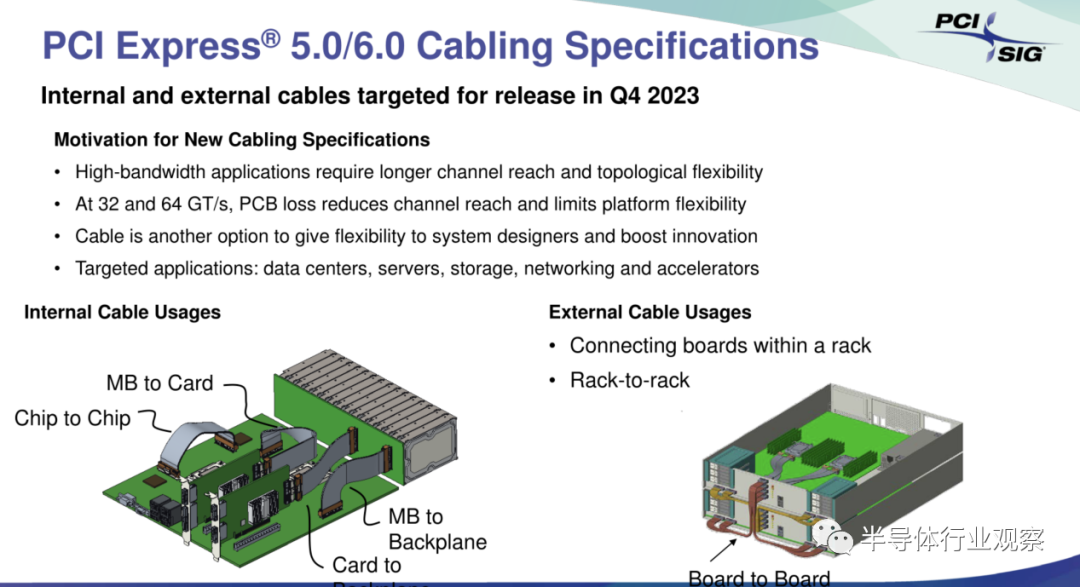

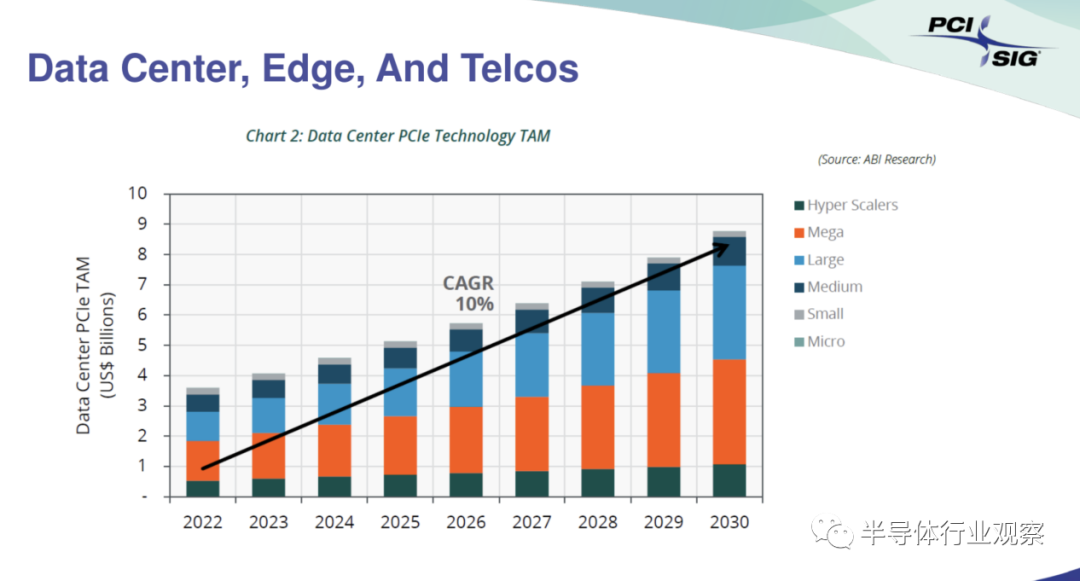

虽然 PCIe 7.0 正在开发中,但 PCIe 6.0 的第一个硬件仍在开发中,甚至 PCIe 5.0 设备也只有不到一年的时间。因此,在开发核心规范的同时,PCI-SIG 还在完成规范的一些辅助领域,特别是布线。

虽然我们传统上首先将 PCIe 视为在印刷电路板上布线的总线,但该标准也始终允许布线。凭借其更新的标准,PCI-SIG 实际上预计在服务器和其他高端设备中布线的使用会增长,这是由于 PCB 的通道范围限制,以及随着信号频率的增加而变得更糟。因此,随着新技术和新材料正在为更好的电缆创造新的选择,布线正在焕然一新,作为根据最新标准维持/扩展信道范围的一种选择。

为此,PCI-SIG 正在制定两项布线规范,预计将于今年第四季度发布。规格将涵盖 PCIe 5.0 和 PCIe 6.0(因为信号频率不变),包括内部和外部电缆的规格。内部布线将把设备连接到系统内的其他部分——包括设备和主板/背板——而外部布线将用于系统到系统的连接。

在信号技术和绝对信号速率方面,PCI Express 落后以太网一代左右。这意味着以太网工作组已经解决了高速铜信号的大部分初始开发问题。因此,尽管仍需努力使这些技术适用于 PCIe,但基本技术已经得到验证,这有助于稍微简化 PCIe 标准和布线的开发。

总而言之,与我们在消费者领域看到的相比,电缆开发无疑是该技术的更多服务器用例。但布线标准仍将是这些用例的重要发展,尤其是随着公司继续将更强大的系统和集群拼接在一起。

附:PCI-SIG 的最新进展

-

PCI

+关注

关注

5文章

679浏览量

132279 -

单通道

+关注

关注

0文章

414浏览量

18666 -

数据信号

+关注

关注

0文章

61浏览量

12153

原文标题:PCIe 7.0标准新进展,速度达到16GB/秒/单通道

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

东风汽车转型突破取得新进展

谷歌Gemini API最新进展

华为公布AI基础设施架构突破性新进展

LPDDR4 16Gb 技术文档详解:SK hynix H9HCNNNBKUMLXR 规格书

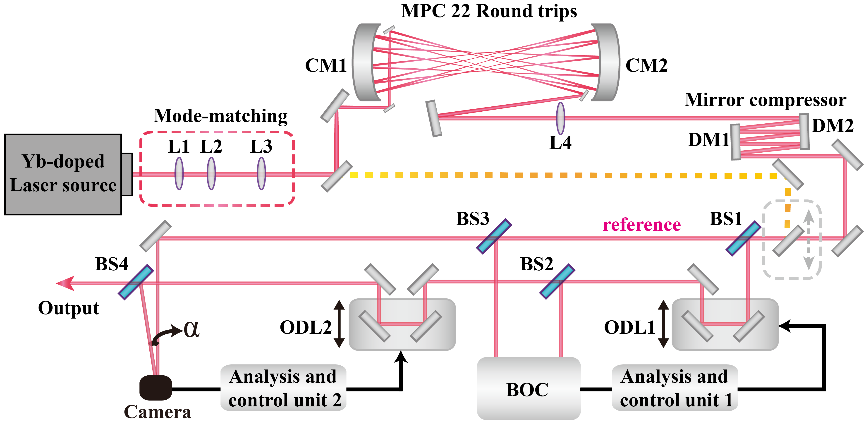

上海光机所在皮秒激光器精密光同步研究方面取得新进展

PCIe 7.0标准新进展,速度达到16GB/秒/单通道

PCIe 7.0标准新进展,速度达到16GB/秒/单通道

评论