python数字除法包括真除法(/)和floor除法(//),并且跟python版本相关。

1.1 python3.0数字除法

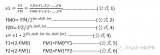

| 序号 | 操作符 | 描述 |

|---|---|---|

| 1 | / | 执行真除法, 结果为浮点数 ,不管操作数类型,商没有余数时,小数部分自动为0;商有余数时,小数部分为真实计算结果,即按除法除出来是多少就是多少。 |

| 2 | // | 执行floor除法。 结果为比商小的整数部分(商向下取整) 。如果操作都是整数,则结果为整数,取商的整数部分。如果任何1个操作是浮点数,则结果为浮点数,取商的整数部分,小数部分为0.商为负数时,需特别注意,并非截断,而是向下取整。 |

示例

# /真除法

>>> 6/2

3.0

>>> 5/2

2.5

>>> 6/2.0

3.0

# //floor除法

>>> 6//2

3

>>> 6//2.0

3.0

>>> 5//2

2

>>> 5//2.0

2.0

# 商为负数

>>> 5//-2

-3

>>> 5//-2.0

-3.0

>>> 5/-2

-2.5

>>> 6/-2

-3.0

1.2 floor除法和截断除法比较

python数字的floor除法,是实际结果向下取整。

而python的截断是直接取实际结果的整数部分。

在实际结果为正数时,floor和截断效果相同。

在实际结果为负数的时候floor除法不是截断,而是向下取整。

示例

>>> import math

>>> math.floor(2.5)

2

>>> math.trunc(2.5)

2

>>> math.floor(-2.5)

-3

>>> math.trunc(-2.5)

-2

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

浮点数

+关注

关注

0文章

61浏览量

16146 -

python

+关注

关注

56文章

4831浏览量

87398

发布评论请先 登录

相关推荐

热点推荐

FPGA怎么实现除法操作?

在FPGA中,我们怎么实现除法操作?最简单的方法当然是调IP Core。在Divider Generator的IP Core中,我们可以选择有/无符号数进行除法,还可以选择除法的延迟。当然,延迟越小

发表于 12-24 16:06

除法器的设计资料分享

4.3 实例九 除法器设计4.3.1. 本章导读要求掌握除法器原理,并根据原理设计除法器模块以及设计对应的测试模块,最后在 Robei可视化仿真软件经行功能实现和仿真验证。设计原理这个除法

发表于 11-12 07:03

定点DSP除法原理及其TMS320C6000 实现

在许多定点DSP芯片中,一般不提供单周期的除法指令;而在实际应用中,又常常要用到除法运算,因此如何利用简单的指令来实现除法是一个非常重要的问题。本文对定点除法算法

发表于 04-16 14:03

?48次下载

基于高速串行BCD码除法的数字频率计的设计

摘要: 介绍了在PPGA芯片上实现数字频率计的原理。对各种硬件除法进行了比较,提出了高速串行BCD码除法的硬件算法,并将其应用在频率计设计中。

发表于 06-20 14:48

?1483次阅读

并行除法器 ,并行除法器结构原理是什么?

并行除法器 ,并行除法器结构原理是什么?

1.可控加法/减法(CAS)单元 和阵列乘法器非常相似,阵列式除法器也是一种并行运算部件,采用大规模集成

发表于 04-13 10:46

?1.6w次阅读

高效的C编程之除法运算

14.2 除法运算 因为ARM体系结构本身并不包含除法运算硬件,所以在ARM上实现除法是十分耗时的。ARM指令集中没有直接提供除法汇编指令,当代码中出现

发表于 10-17 17:22

?5次下载

实例九— 除法器设计

4.3 实例九 除法器设计4.3.1. 本章导读要求掌握除法器原理,并根据原理设计除法器模块以及设计对应的测试模块,最后在 Robei可视化仿真软件经行功能实现和仿真验证。设计原理这个除法

发表于 11-07 10:51

?18次下载

FPGA基于线性迭代法的除法器设计

FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个共同的问题——都是黑盒子,在进行时序违例处理时,往往不好操作,比如想打打拍改善下时序都不知从何下手。

剖析python数字除法、floor除法

剖析python数字除法、floor除法

评论