用工具建工程对Verilog进行仿真、综合或者其它操作时,在写脚本的时候常常需要工程中Veriog文件的列表,若工程中.v文件过多,则常常需要手动编写文件列表。本文教给大家用C语言简单写的一个自动生成某个文件夹下所有.v文件列表的方法。

使用说明

环境:Windows 7操作系统或其它常用Windows操作系统

编译器:DEV C++或其它

使用方法:随便找个C语言的编译器,静态编译生成exe文件后,可随意拷贝至某文件夹下,双击运行,等待输出rtl.f文件即可。

使用举例:将生成的exe文件拷贝至C:modeltech64_10.4目录下,双击运行,如下动图。

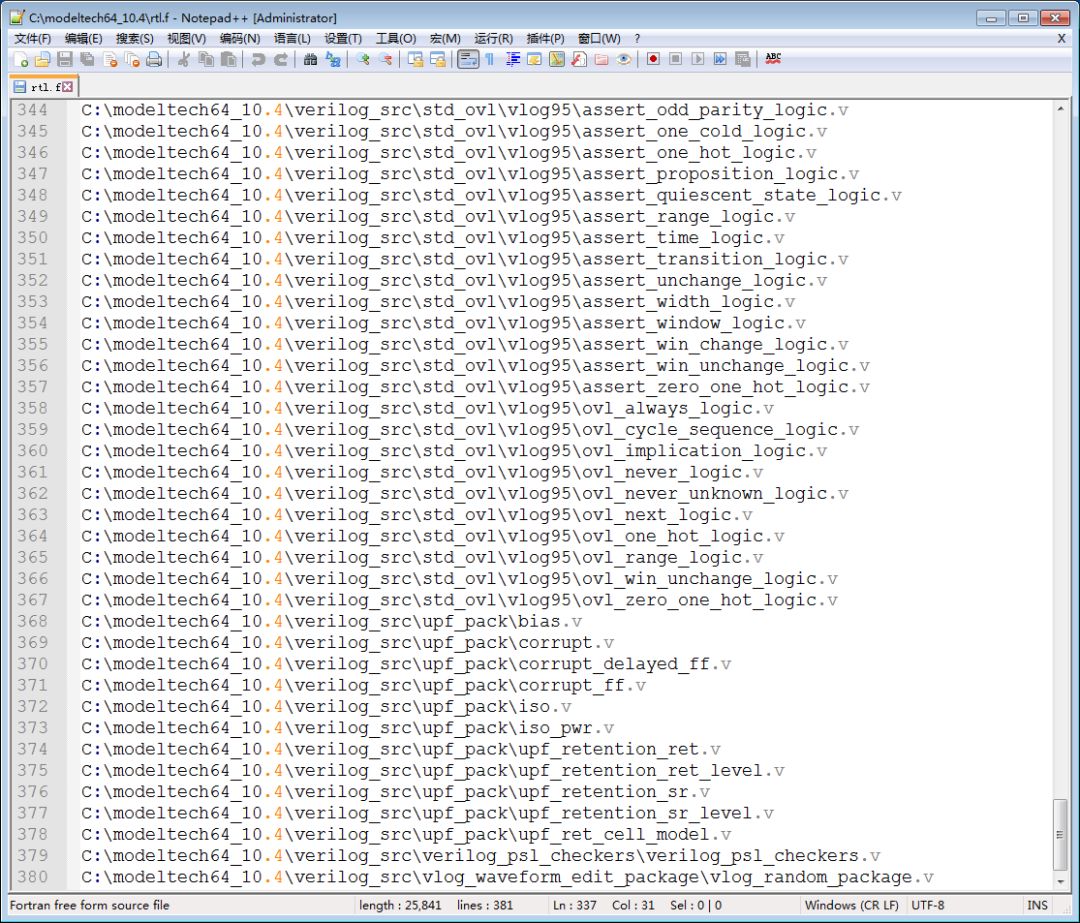

生成的rtl.f打开后如下图所示。

另外,该代码提供了一种操作Windows系统路径的操作方法,可以简单修改一下,用作它用。如找到某种类型的文件或某个文件进行拷贝、转移、修改、删除等操作。

源代码

#includememset (buf1,0,800);

strcpy(buf1,files[i].name);

type=0;

k=strlen(buf1);

//printf("

k=%d;",k);

for(j=0;j<=k;j++)

????????{

????????????if((buf1[j]=='.')&&((buf1[j+1]=='v')||(buf1[j+1]=='V'))&&(j==k-2))

//if((buf1[j]=='.')&&(j==k-2))

{

//printf("

j=%d

",j);

type=1;

files[i].vtype=1;

fprintf(fp1,"%s

",files[i].name);

}

}

}

getch();

fclose(fp1);

return0;

}

版本更新记录

版本号:V1.1.2

更新日期:2013-07-17

1446 修改代码,扩展name的长度为800,可以处理长路径的情况

版本号:V1.1.1

更新日期:2013-05-18

1038 修改代码,添加判断语句&& (j==k-2),避免.vhd等文件也被列出来

版本号:V1.1.0

更新日期:2013-02-10

1455 已添加对文件名进行判断,能够自动的将当前路径下的所有文件及子文件夹下的.v文件列举出来。

审核编辑 :李倩

-

操作系统

+关注

关注

37文章

7173浏览量

125862 -

Verilog

+关注

关注

29文章

1367浏览量

112417 -

代码

+关注

关注

30文章

4905浏览量

70958

原文标题:如何快速生成Verilog代码文件列表(附开源C代码)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

用CubeMX生成代码时会将main.c文件中的汉字变成乱码,怎么解决?

cunbemx生成RTthread代码疑似漏复制文件怎么解决?

STM32CubeMX生成代码就会覆盖CMakeLists.txt文件,怎么解决?

Verilog 与 ASIC 设计的关系 Verilog 代码优化技巧

Verilog 测试平台设计方法 Verilog FPGA开发指南

Verilog与VHDL的比较 Verilog HDL编程技巧

探索设计稿自动生成Flutter代码的技术方案

如何快速生成Verilog代码文件列表

如何快速生成Verilog代码文件列表

评论