由于传统微缩(scaling)技术系统的限制,DRAM的性能被要求不断提高,而HKMG(High-k/Metal Gate)则成为突破这一困局的解决方案。SK海力士通过采用该新技术,并将其应用于全新的1anm LPDDR5X DRAM, 即便在低功率设置下也实现了晶体管性能的显著提高。本文针对HKMG及其使用益处进行探讨。

厚度挑战: 需要全新的解决方案

组成DRAM的晶体管(Transistor)包括存储数据的单元晶体管(Cell Transistor)、恢复数据的核心晶体管(Core Transistor),以及涉及控制逻辑和数据输入和输出的外围晶体管(Peripheral Transistor)。随着技术的进步,单元电容器和单元晶体管在提高DRAM存储容量方面取得了一些技术突破。另一方面,对于外围晶体管,重点是实现工艺尺寸微缩以提高性能。

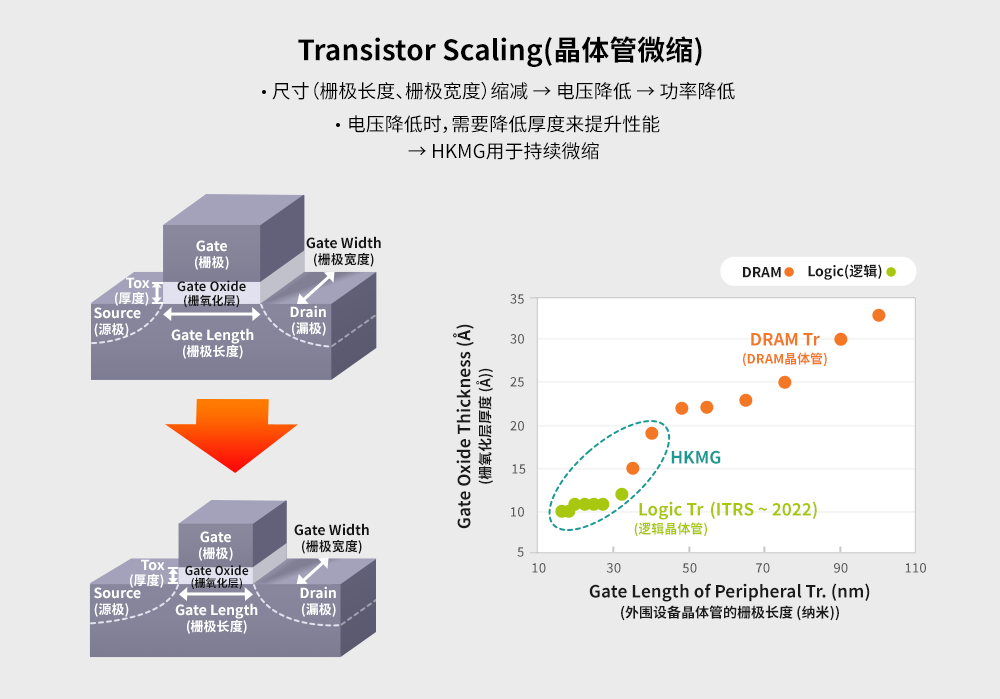

栅极由绝缘膜(栅氧化层, gate oxide)和电极(栅电极, gate electrode)组成,在晶体管开关功能中发挥主要作用。栅氧化层由SiON氧化物绝缘体和聚硅基电极组成。随着晶体管微缩的提升,源极和漏极之间的距离越来越近,电流移动速度加快,但施加在栅极上的电压也会降低,以降低功耗。

但还存在一个问题:为了在较低电压下提高性能,必须减小栅氧化材料(SiON)的厚度(Tox)。但随着厚度不断减小,栅氧化层的可靠性也会降低,从而导致功率损耗,这限制了厚度的进一步减小。

图1:Transistor Scaling(晶体管微缩)

HKMG: 微缩与性能的突破

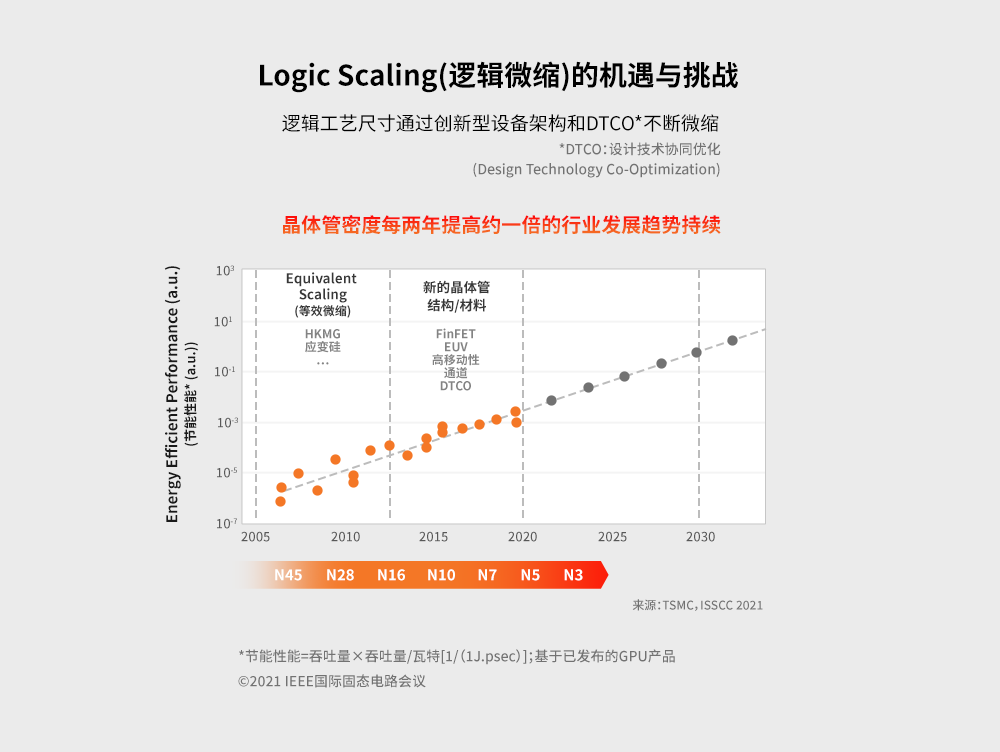

在2005年前后,逻辑半导体中基于多晶硅栅极(Poly-Si Gate)/SiON氧化物(poly/SiON)的传统微缩在性能改进方面开始表现出局限性,因为它无法减小SiON栅氧化层的厚度。为了克服这些局限性,根据逻辑晶体管行业发展趋势,许多具有颠覆性的创新技术被开发出来。

同样明显的是,外围/核心晶体管特性正成为DRAM的瓶颈,在需要快速提高性能的高端产品中尤为如此。因此,需要一种全新的解决方案来克服微缩基于多晶硅栅极/SiON氧化物的晶体管时存在基本限制,并且需要在DRAM中采用高k/金属栅极(HKMG)技术,这促使逻辑晶体管技术实现了最重大的创新。

图2:Logic Scaling(逻辑微缩)的机遇与挑战

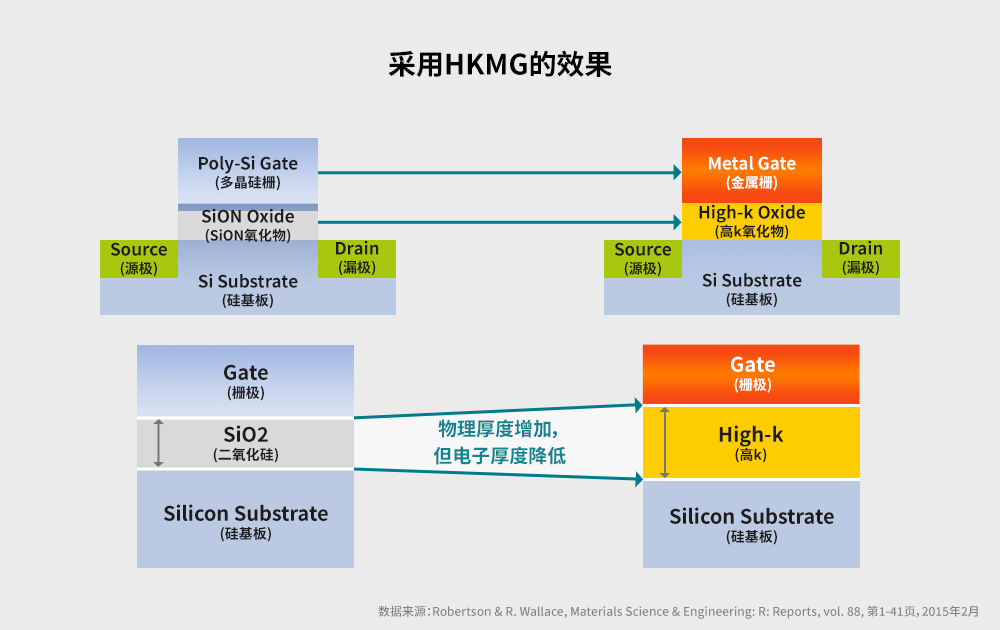

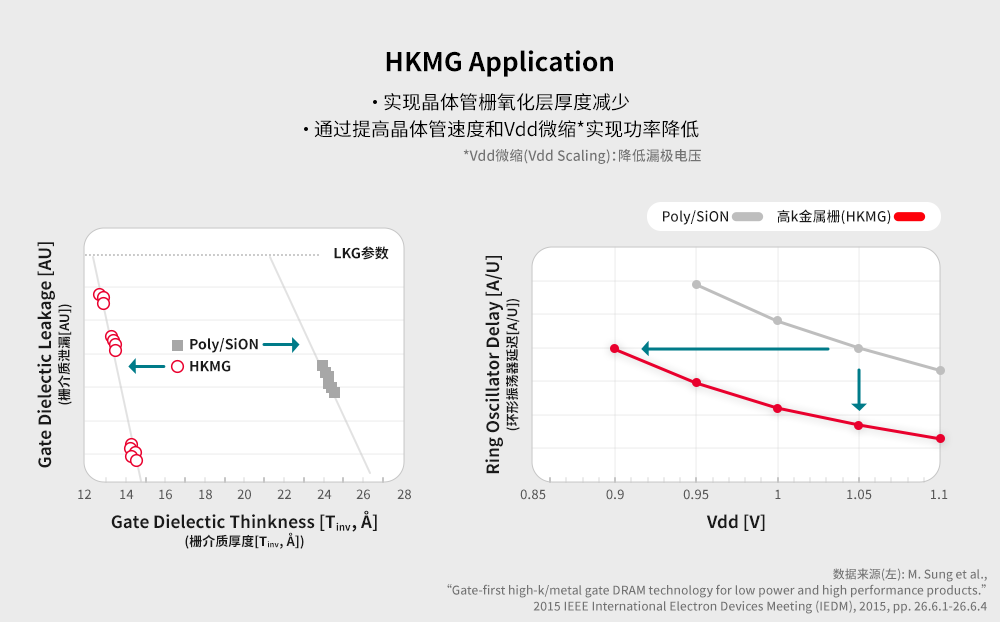

借助HKMG,一层薄薄的高k薄膜可取代晶体管栅极中现有的SiON栅氧化层,以防止泄漏电流和可靠性降低。此外,通过减小厚度,可以实现持续微缩,从而显著减少泄漏,并改善基于多晶硅/SiON的晶体管的速度特性。

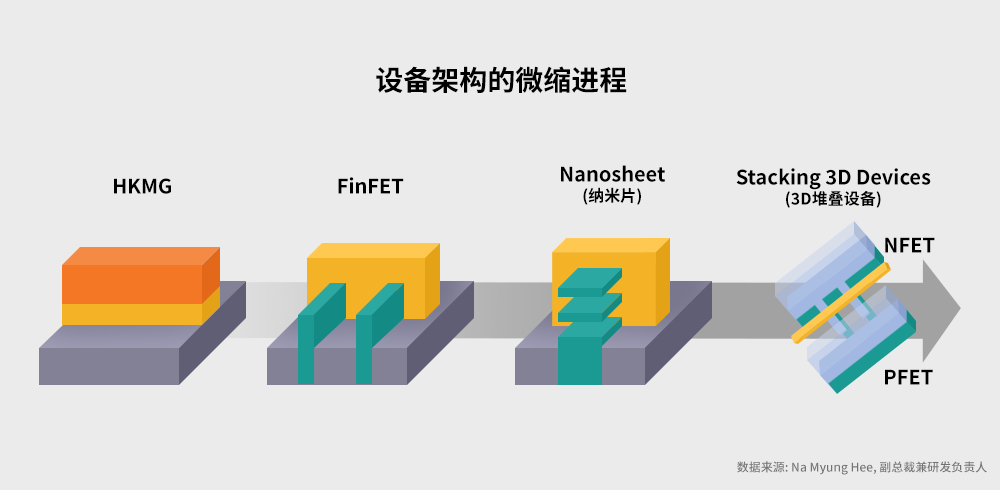

图3:设备架构的微缩进程

在学术界和工业界,研究人员研究了多种高k薄膜材料。通常情况下,基于Hf的栅氧化层用于高温半导体制造工艺,因为它们可以确保自身和硅的热稳定性。为了防止现有多晶硅电极材料与高k栅氧化层之间的相互作用,必须引入金属电极来代替多晶硅。这使得名为高k/金属栅极的集成解决方案应运而生,该解决方案将高介电常数栅氧化层与金属电极相结合。

图4:采用HKMG的效果

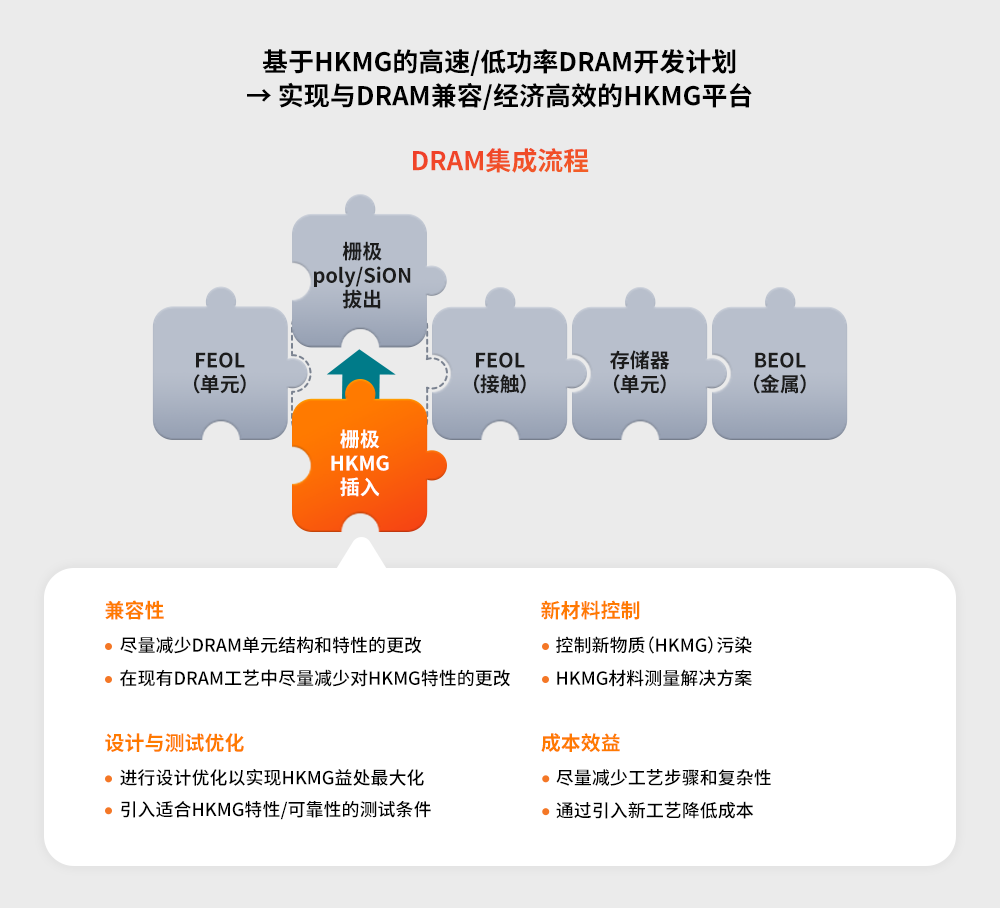

为了将SiON/Poly栅极转换为HKMG栅极,对相关工艺的几个部分进行了更改,包括在DRAM工艺流程中形成外围电路(外围晶体管)的栅极材料(SiON/Poly栅极拔出→HKMG电极插入)。然而,必须对HKMG材料、工艺和集成流程进行优化,以适合新材料和新工艺的构建块。因此,需要利用复杂的开发工艺来应对以下挑战。

图5:HKMG让DRAM开发更加有效且经济

1.兼容性:与SiON/Poly栅极相比,HKMG的热稳定性相对较弱。具体来说,DRAM需要在高温下进行额外处理,以实现单元阵列结构,与后续工艺流程中对通用逻辑半导体的处理方式截然不同。由于这个原因,HKMG本身的可靠性下降,导致在传统逻辑半导体中未出现相互作用。因此,必须对HKMG工艺本身和现有DRAM集成工艺进行优化,以了解新交互带来的新问题并找到解决方案。

2.新材料控制:需要引入工艺控制措施,例如针对新物质的测量解决方案,以防止现有设备和产品受到新物质和新工艺的影响。

3.设计与测试优化:随着栅极材料的变化,晶体管特性和可靠性表现与传统的poly/SiON栅极截然不同,为了最大限度地发挥HKMG的优势,增强不同于poly/SiON栅极的可靠性特征,有必要应用新设计和设计方案,并优化此类测试。

4.经济高效的工艺解决方案:最后,必须提供经济高效的解决方案,通过工艺集成优化,最大限度地减少因引入新材料和新工艺而增加的成本。通过这种方法,可以控制因引入新工艺、新设备和新工艺步骤而增加成本。

图6:HKMG Application

领先的低功耗解决方案

SK海力士通过将HKMG工艺整合为适用于DRAM工艺的形式,进行了平台开发。尽管面临极端的技术挑战,但公司通过识别与DRAM流相互作用相关的任何潜在风险,并通过包括试点操作在内的预验证工艺来确保解决方案,成功开发和批量生产HKMG。公司的目标是通过推进从SiON/Poly栅极到升级构件HKMG的过渡,为下一代技术节点和产品带来卓越的技术创新。

SK海力士的LPDDR5X DRAM是首款在低功耗应用中使用HKMG成功批量生产的产品,通过大尺度微缩,同时利用全新HKMG晶体管构建块的优势了,晶体管的性能获得显著提升;考虑到HKMG的固有特性和针对HKMG优化的设计方案,可以有效控制泄漏电流,较之poly/SiON,速度提高33%,功耗降低25%。SK海力士的技术不仅达到行业的目标标准,还因为最低功耗而实现ESG价值最大化。

为此,SK海力士还将HKMG技术平台扩展至可支持低功耗和高性能产品,增强了在下一代HKMG技术方面的技术竞争力。

最后希望特别指出的是,近期在HBM、PIM、AiM等逻辑半导体架构和存储器半导体架构之间的融合上呈现出技术创新之势,而HKMG工艺在DRAM中的应用正契合了这一趋势。这表明,在半导体制造过程中,逻辑半导体的先进技术解决方案与DRAM工艺技术之间的融合正在全面展开。

审核编辑 :李倩

-

DRAM

+关注

关注

40文章

2354浏览量

186089 -

晶体管

+关注

关注

77文章

10052浏览量

142628 -

SK海力士

+关注

关注

0文章

998浏览量

39829

原文标题:海力士:引领High-k/Metal Gate工艺变革

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

SK海力士在微细工艺技术领域的领先实力

SK海力士HBM技术的发展历史

SK海力士强化HBM业务实力的战略规划

SK 海力士发布2024财年财务报告

集成电路新突破:HKMG工艺引领性能革命

海力士:引领High-k/Metal Gate工艺变革

海力士:引领High-k/Metal Gate工艺变革

评论