概述

随着数据中心、人工智能、自动驾驶、5G、计算存储和先进测试等应用的数据量和数据流量不断增大,不仅需要引入高性能、高密度FPGA来发挥其并行计算和可编程硬件加速功能,而且还对大量数据在FPGA芯片内外流动提出了更高的要求。于是,在FPGA芯片中集成包括片上二维网络(2D NoC)和各种最新高速接口的新品类FPGA芯片应运而生,成为FPGA产业和相关应用的新热点。

拉开这场FPGA芯片创新大幕的是全球最大的独立FPGA技术和产品提供商Achronix半导体公司,其采用7nm工艺打造的Achronix Speedster7t FPGA不仅拥有诸多高性能外围Hard IP,而且是全球第首次在FPGA的逻辑阵列上集成了2D NoC,一经推出就在市场得到了积极的响应,并引来竞争对手的模仿和跟随。

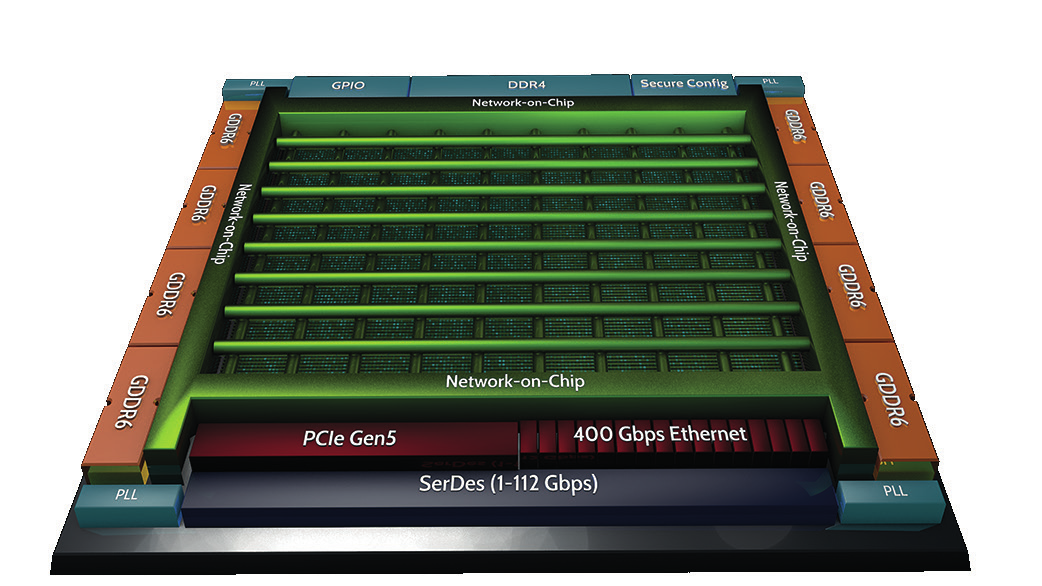

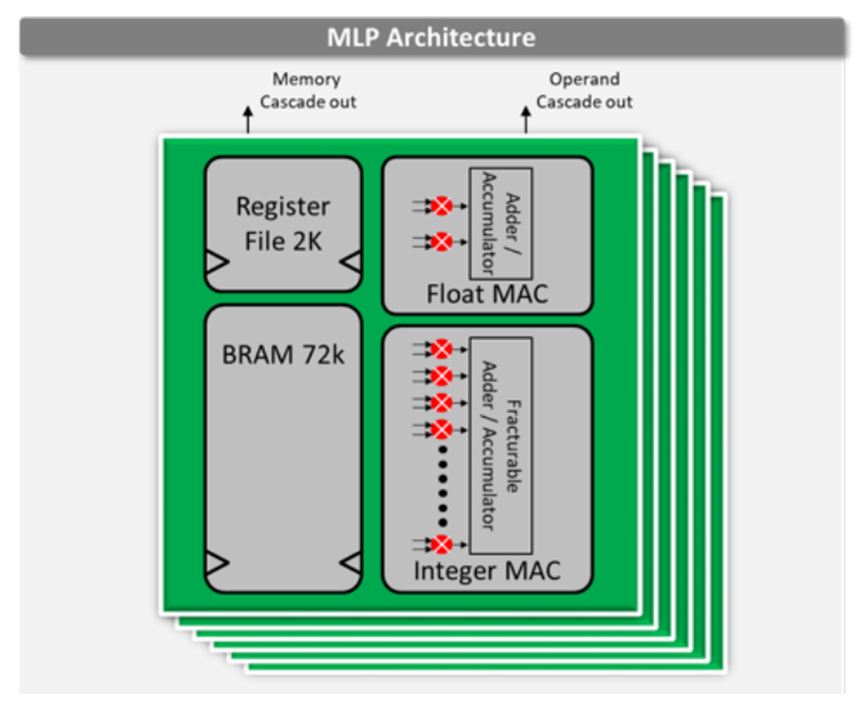

Speedster7t这款专门针对人工智能/机器学习(AI / ML)和高带宽应用进行优化的高性能、高密度FPGA,包括了革命性的二维片上网络(2D NoC)、新型机器学习处理器(MLP)、400G以太网和PCIe Gen5端口,以及高带宽GDDR6和DDR4/5存储控制器。Speedster7t FPGA架构如图1所示。

图1 Speedster7t FPGA结构图

Achronix Speedster7t FPGA除了在外围Hard IP上都采用目前业内领先的大带宽高速率IP,在内部的可编程逻辑的架构中也做了大量的优化去进一步提高内部可编程逻辑的性能,从而适配外围IP超高带宽需求。本文首先谈谈Speedster7t FPGA的片上SRAM,也就是Block RAM针对传统的结构所做出的一些优化。

Speedster7t FPGA中可编程逻辑的架构

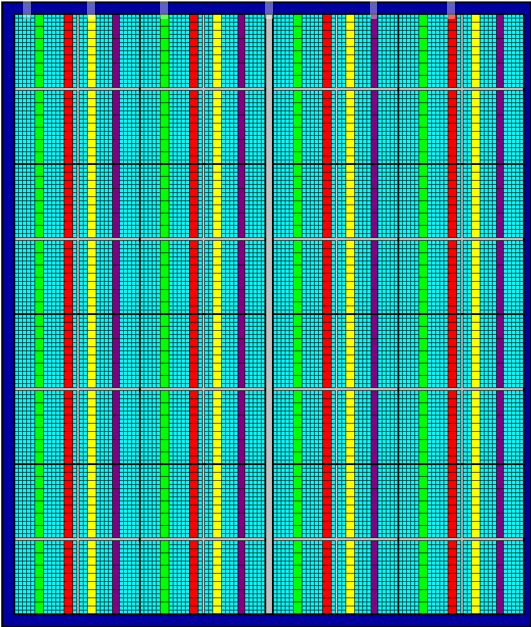

Speedster7t FPGA中内部的可编程资源是按列排布,包括LUT、FF、ALU、MUX、MLP、Block RAM、Logic RAM。如图2所示。

图2 Speedster7t FPGA可编程逻辑结构

其中MLP、Block RAM、Logic RAM是集成在一起,他们之间的连接用的是专有的走线,不占用可编程逻辑走线资源,这样做的目的主要是为了提高性能,同时也可以节省可编程逻辑走线资源,这个架构对于AI,还有需要用到MLP的一些复杂算法的性能优化是非常明显的,在我们的MLP系列文章中会详细讲到,这里我们只重点说一下Block RAM。 Speedster7t FPGA的Block RAM特点 Speedster7t FPGA内部的Block RAM是一个容量为72k bit的简单双端口RAM,有一个读端口,一个写端口。两个端口的时钟完全独立,并且可以完全独立的配置读写位宽。它可以灵活的配置成简单双端口RAM或者ROM。

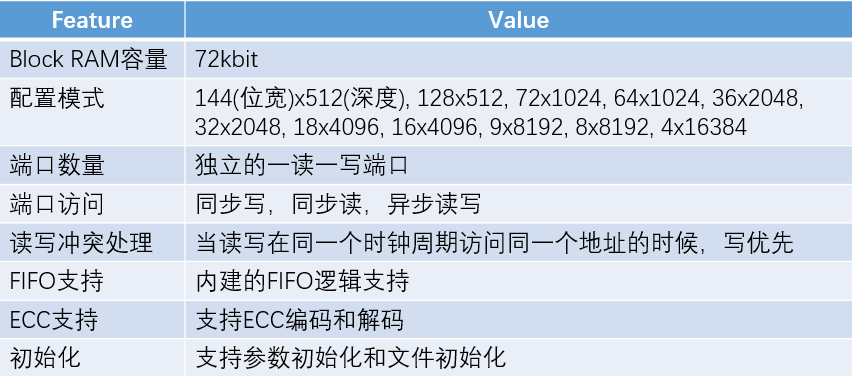

Block RAM的主要特性如表1所示。

表1 Block RAM的关键特性

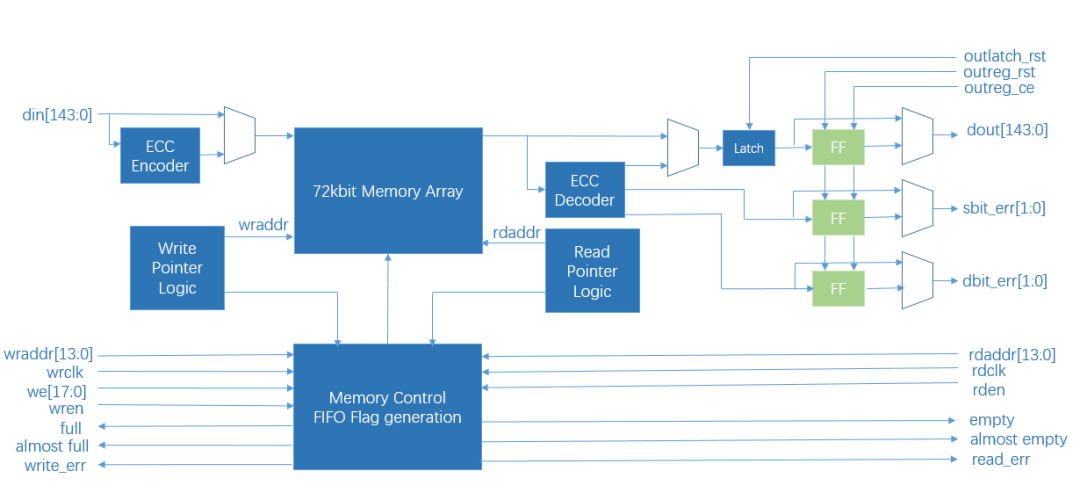

Block RAM框图如图3所示。

图3 Block RAM内部结构

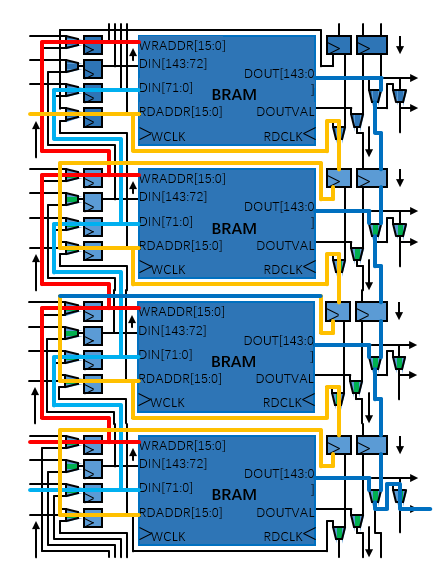

Speedster7t FPGA的Block RAM级联结构

Speedster7t FPGA的Block RAM最大的特点是增加了Block RAM间的级联走线,级联走线是BRAM间专有的连线,不占用可编程逻辑的走线资源,可以极大的提升多个Block RAM级联的性能。图4显示了Block RAM间级联走线的架构。

图4 Block RAM级联结构

由图4可以看出,读写地址线和数据线都有专有的级联线连接。这样的架构在一些场景中都会有应用,比如:需要从外部端口接收数据或者从GDDR6读数据去初始化大量Block RAM的场景,AI的神经网络就是一个典型的应用,在每一层的卷积算法中,系统都会从GDDR6读出图像数据和权重数据放入每个引擎的Block RAM中,引擎计算完毕以后再存入到GDDR6中供下一次运算使用。

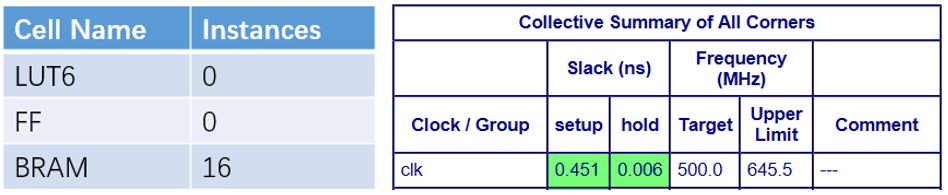

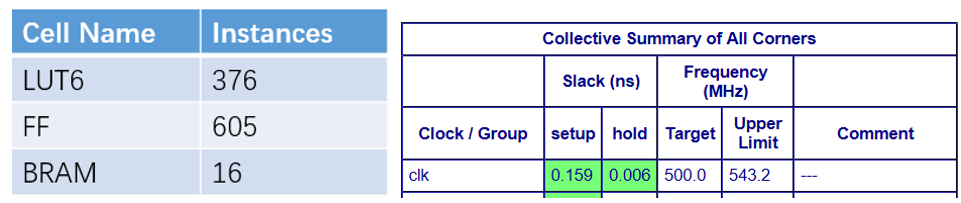

有了这样的级联架构,我们在写入数据去初始化大量Block RAM的时候不需要外部数据有很大的扇出,直接通过同一列Block RAM的级联线就可以轻松完成,具体实现可以参考Achronix MLP_Conv2D参考设计。另外一个例子就是在需要多个Block RAM去构成更大容量的RAM的时候,如果利用级联线可以大大提升系统的性能。我们针对这个专门做了一个工程比较一下,生成一个位宽64bit,深度16384的一个简单双端口RAM,需要用到16个Block RAM。我们分别用专有级联线和内部可编程逻辑去拼深度两种方法来对比。可以看到用专有的级联线资源更省,而且性能有了很大的提高。

使用专有的级联线资源占用和性能:

使用可编程逻辑资源占用和性能:

后面我们会继续深入了解Speedster7t FPGA可编程逻辑的各种特性,并且会用一些例子来说明如何更高效的利用这些特性,以将Speedster7t这款业界首创的高数据带宽FPGA芯片与更多的创新智能化应用结合起来。

此外,Achronix也提供Speedcore嵌入式FPGA硅知识产权(IP)产品,用来帮助用户在应用规模进一步扩大后,去开发带有eFPGA逻辑阵列的ASIC或者SoC产品,它们由Achronix的ACE FPGA开发工具提供支持,从而可以重用FPGA开发成果,这是Achronix在率先引入2D NoC和MLP之外,另一个层面上的创新。

审核编辑 :李倩

-

FPGA

+关注

关注

1646文章

22072浏览量

619831 -

芯片

+关注

关注

460文章

52624浏览量

442783 -

机器学习

+关注

关注

66文章

8510浏览量

134895

原文标题:超高数据流通量FPGA新品类中的Block RAM级联架构

文章出处:【微信号:Achronix,微信公众号:Achronix】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

5CEBA4F23C8NQS现场可编程门阵列(FPGA)芯片

fpga和cpu的区别 芯片是gpu还是CPU

可编程交流负载标准

可编程混合信号技术弥补逻辑IC的成本与密度空白

Achronix与BigCat Wireless建立战略合作伙伴关系

德州仪器推出全新可编程逻辑产品系列

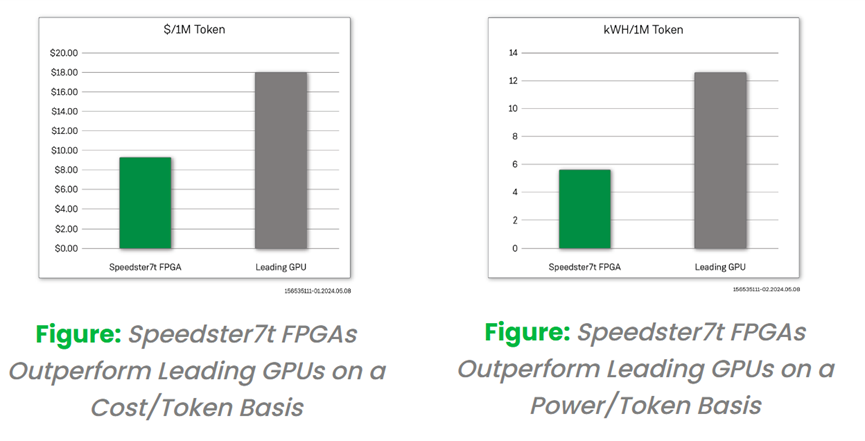

Achronix Speedster7t FPGA与GPU解决方案的比较

基于Achronix Speedster7t FPGA器件的AI基准测试

用TMAG5328电阻器和电压可编程霍尔效应开关实现可编程性和诊断

Speedster7t FPGA中可编程逻辑的架构

Speedster7t FPGA中可编程逻辑的架构

评论