以下为台积电芯片封装技术演讲PPT:

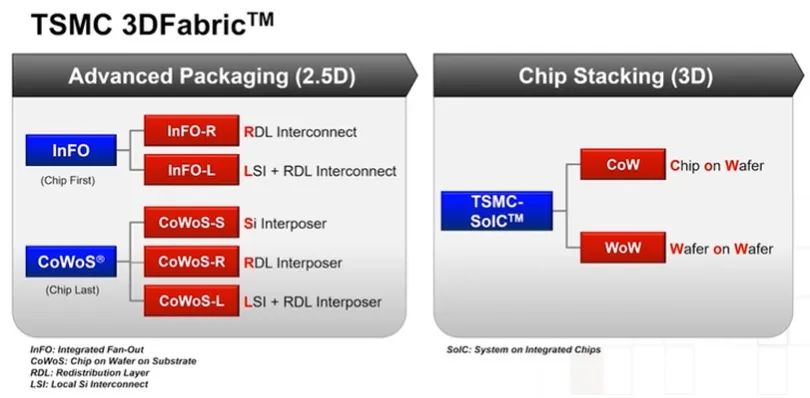

3DFabric概述

台积电3D Fabric先进封装技术涵盖2.5D和垂直模叠产品,如下图所示。

集成的FanOut (InFO)封装利用了由面朝下嵌入的模具组成的重构晶圆,由成型化合物包围。 在环氧晶片上制备了再分布互连层(RDL)。(InFO- l是指嵌入在InFO包中的模具之间的硅“桥晶片”,用于在RDL金属化间距上改善模具之间的连接性。) 2.5D CoWoS技术利用microbump连接将芯片(和高带宽内存堆栈)集成在一个插入器上。最初的CoWoS技术产品(现在的CoWoS- s)使用了一个硅插入器,以及用于RDL制造的相关硅基光刻;通过硅通道(TSV)提供与封装凸点的连接。硅插入器技术提供了改进的互连密度,这对高信号计数HBM接口至关重要。最近,台积电提供了一种有机干扰器(CoWos-R),在互连密度和成本之间进行权衡。 3D SoIC产品利用模块之间的混合粘接提供垂直集成。模具可能以面对面的配置为向导。TSV通过(减薄的)模具提供连接性。

InFO和CoWoS产品已连续多年大批量生产。CoWoS开发中最近的创新涉及将最大硅插入器尺寸扩展到大于最大光罩尺寸,以容纳更多模具(尤其是HBM堆栈),将RDL互连拼接在一起。

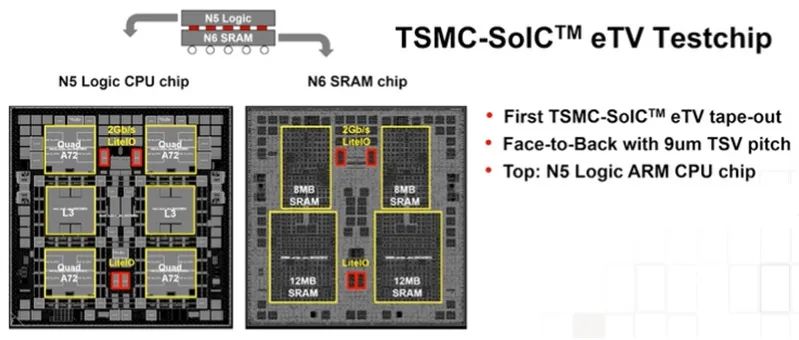

SoIC Testchip

台积电分享了最近的SoIC资格测试工具的结果,如下所示。

使用的配置是(N5)CPU裸片与(N6)SRAM裸片在面对背拓扑中的垂直接合。(事实上,一家主要的CPU供应商已经预先宣布了使用台积电的SoIC将垂直“最后一级”SRAM缓存芯片连接到CPU的计划,该芯片将于2022年第一季度上市。)

SoIC设计流程

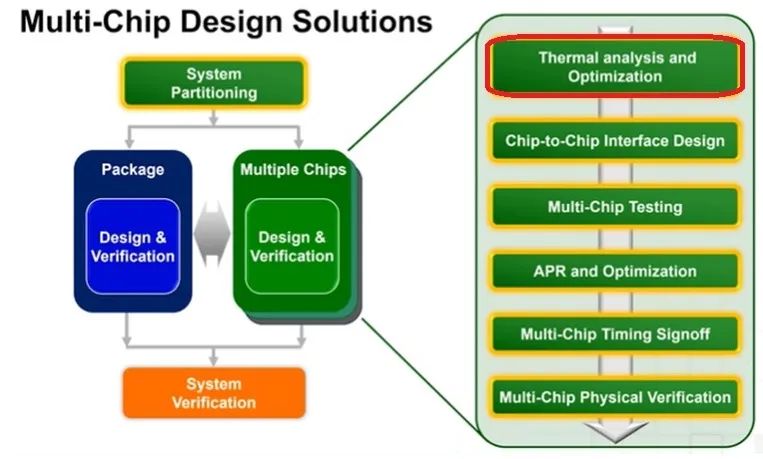

垂直模具集成的高级设计流程如下图所示:

该流程需要同时关注自上而下的系统划分为单独的芯片实施,以及对复合配置中的热耗散的早期分析,如上所述。

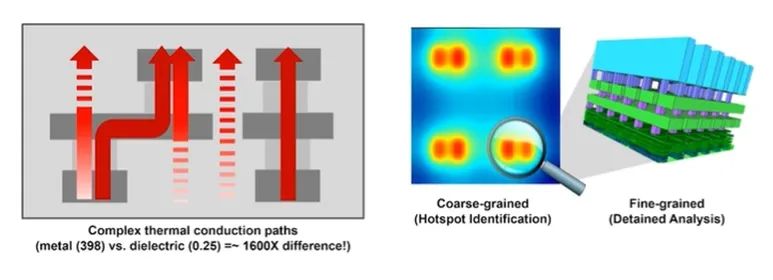

热分析的讨论强调了BEOL PDN和互连的低热阻路径与周围电介质相比的“chimney”性质,如上所示。具体而言,台积电与EDA供应商合作提高SoIC模型离散化技术的准确性,在最初通过粗网格分析确定的特定“热点”区域应用更详细的网格。 台积电还提出了一种方法,将热分析结果纳入SoIC静态时序分析降额因子的计算。就像片上变化(OCV)依赖于(时钟和数据)时序路径所跨越的距离一样,SoIC路径的热梯度也是一个额外的降额因素。台积电报告说,一个路径的模上温度梯度通常为~5-10C,一个小的平滑降额温度时间裕度应该足够了。对于SoIC路径,~20-30C的大梯度是可行的。对于温差较小的路径,覆盖此范围的平坦降额将过于悲观——应使用 SoIC 热分析的结果来计算降额因子。

SoIC测试

IEEE 1838标准化工作与模对模接口测试(link)的定义有关。 与用于在印刷电路板上进行封装到封装测试的芯片上边界扫描链的IEEE 1149 标准非常相似,该标准定义了每个芯片上用于堆栈后测试的控制和数据信号端口。该标准的主要重点是验证在SoIC组装过程中引入的面对面键合和TSV的有效性。 对于SoIC芯片之间的低速I/O,这个定义已经足够了,但是对于高速I/O接口,需要更广泛的BIST方法。

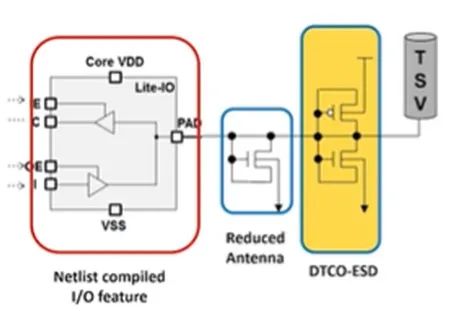

用于SoIC的TSMC Foundation IP–LiteIO

TSMC的库开发团队通常为每个硅工艺节点提供通用I/O单元(GPIO)。对于SoIC配置中的die-to-die连接,驱动程序负载较少,台积电提供了“LiteIO”设计。如下图所示,LiteIO设计侧重于优化布局以减少寄生ESD和天线电容,从而实现更快的裸片之间的数据速率。

EDA启用

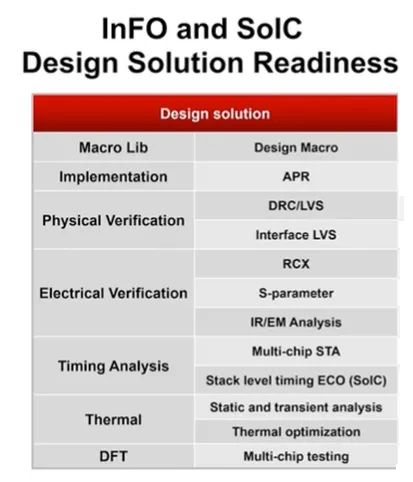

下图列出了最近与主要EDA供应商合作为InFO和SoIC封装技术开发的关键工具功能。

总结

台积电继续大力投资2.5D/3D先进封装技术开发。最近的主要举措集中在3D SoIC直接芯片贴装的方法上——即分区、物理设计、分析。具体来说,早期热分析是必须的步骤。此外,台积电还分享了他们的SoIC eTV资质测试芯片的测试结果。2022年将见证3D SoIC设计的快速崛起。

审核编辑 :李倩

-

台积电

+关注

关注

44文章

5760浏览量

170150 -

封装技术

+关注

关注

12文章

580浏览量

68652

原文标题:详解台积电3DFabric封装技术

文章出处:【微信号:today_semicon,微信公众号:今日半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

台积电3D Fabric先进封装技术详解

台积电3D Fabric先进封装技术详解

评论