DP1363F是高度集成的收发器芯片,用于13.56Mhz的非接触式通讯。DP1363F收发器DP1363F支持下列操作模式

? 兼容CLRC663/RC663

? 读写模式支持 ISO/IEC 14443A/MIFARE

? 读写模式支持 SO/IEC 14443IB

? JIS X 6319-4 读写模式支持(等效于FeliCa1方案)

? 相应于 ISO/IEC 18092 的被动发起方模式

? 读写模式支持 ISO/IEC 15693

? 读写模式支持 ICODE EPC UID/EPC OTP

? 读写模式支持 ISO/IEC 18000-3 mode 3/ EPC Class-1 HF

DP1363F芯片特性

? 高射频输出功率的前端IC,传输速度高达848 kbit/s

? 支持ISO/IEC 14443A/MIFARE,ISO/IEC 14443B和FeliCa

? 相符于ISO/IEC 18092的P2P被动发起方模式

? 支持ISO/IEC 15693,ICODE EPC UID和ISO/IEC 18000-3模式3/ EPC Class-1 HF

? 以读写模式支持MIFARE经典加密

? 低功耗卡片检测

? 符合“EMV非接触式协议规范V2.0.1“所要求的发射功率

? 天线连接仅需用用最少量的外部元件

? 支持的主机接口:

- SPI高达10 Mbit/s

- I2C总线接口,高速模式可达400 kBd,超高速模式则可高达1000 kBd

- RS232串行UART,最高至1228.8 kBd,电压水平由引脚电源电压决定

? 独立 I2C总线接口用于连接安全访问模块(SAM)

- 512字节大小的FIFO缓冲器提供最高通信性能

- 灵活和高效的省电模式,包括断电模式,待机模式和低功耗卡片检测

? 由27.12 MHz晶振源通过集成的PLL产生系统时钟,从而节省成本

? 3.3V 至 5V 的电源

? 多达8个可自由编程的输入/输出引脚

? 与ISO/IEC 14443A/MIFARE卡的读写通信模式典型操作距离可达12厘米,取决于天线的尺寸和调谐

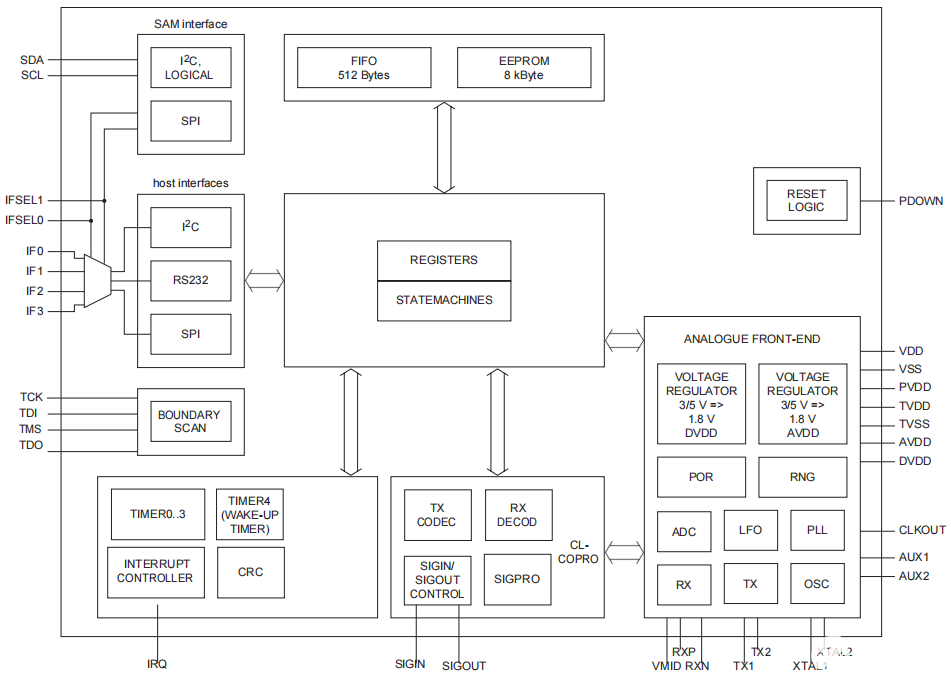

DP1363F结构框图

-

读写器

+关注

关注

3文章

710浏览量

39813 -

收发器芯片

+关注

关注

0文章

14浏览量

8432

发布评论请先 登录

DP4363 一款高性能、低电流的Sub-GHz收发芯片

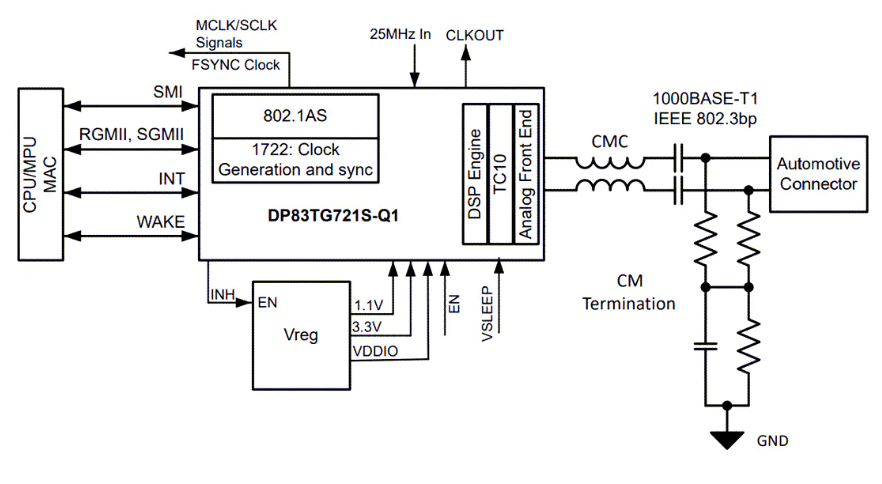

Texas Instruments DP83TG721-Q1 1000Base-T1以太网物理层收发器数据手册

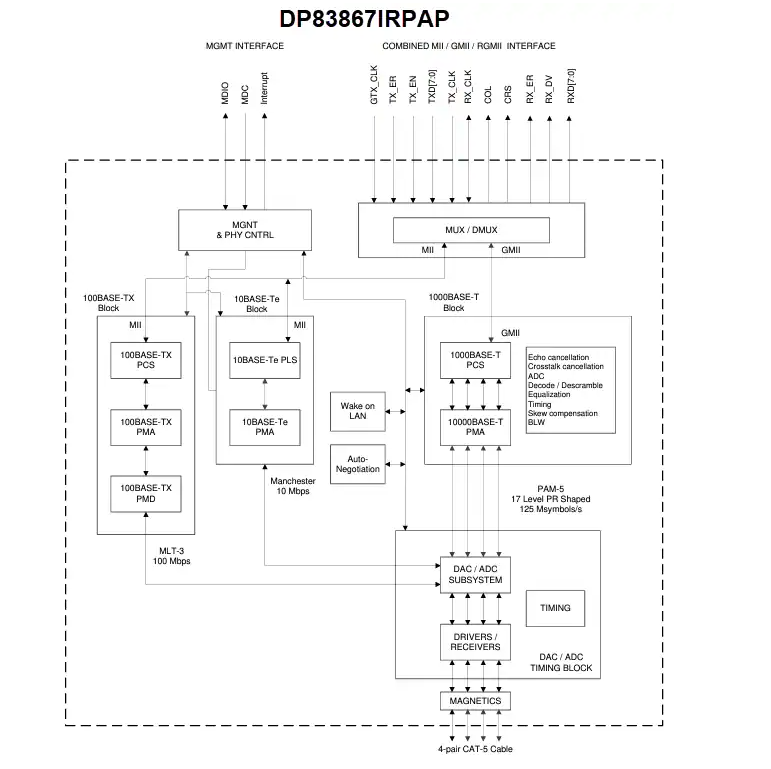

Texas Instruments DP83867IR/DP83867CR以太网PHY收发器数据手册

光纤收发器与IO-Link收发器的区别

无线收发器工作原理,无线收发器怎么使用

DP1363F是一款非接触读写芯片,高性能、多协议NFC读卡IC

单端K总线收发器DP9637兼容L9637

常用于OBD系统的CSM9241总线收发器芯片选型

DP1363F收发器芯片的操作模式及特性

DP1363F收发器芯片的操作模式及特性

评论