FPGAЕФВМОжВМЯпШэМўЯђРДХмЕУКмТ§ЁЃЪТЪЕЩЯЃЌFPGAЙЉгІЩЬвбОЛЈСЫКмДѓЕФОЋСІЪЙЦфЩшМЦШэМўдкЖрКЫДІРэЦїЩЯдЫааЕУИќПьЁЃ

зюНќЃЌдкACMЕФFPGA 2022ЛсвщЩЯЗЂБэСЫвЛЦЊЬтЮЊЁАRapidStream: FPGA HLSЩшМЦЕФВЂааЮяРэЪЕЯжЁБЕФТлЮФЃЌТлЮФжаУшЪіСЫвЛжжЗЧГЃгаШЄЕФЗНЗЈЃЌЭЈЙ§FPGAЩшМЦШэМўЭЦЖЏHLSЩшМЦИќПьЕидЫаадкЖрКЫДІРэЦїЩЯЁЃ

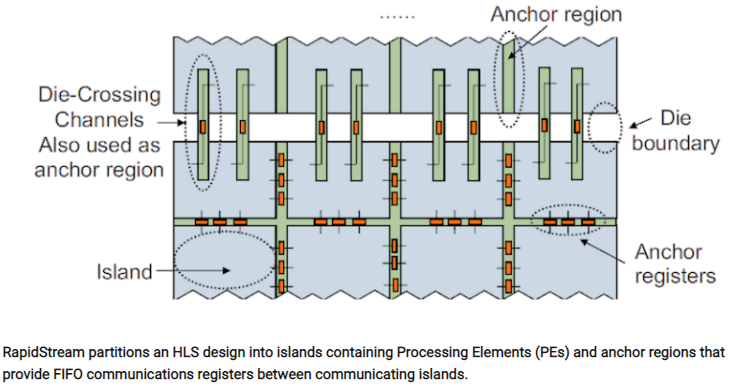

етЦЊТлЮФгЩUCLAЁЂAMD-XilinxЁЂИљЬиДѓбЇКЭПЕФЮЖћДѓбЇЕФбаОПЭХЖгзЋаДЃЌУшЪіСЫRapidStreamздЖЏЗжЧјЫуЗЈЃЌНЋЪ§ОнСїЩшМЦЗжИюГЩЖрИіЁАislandЁБЃЌдкЛЎЗжЕФislandжЎМфВхШыЁАanchor regionsЁБЃЌШЛКѓЭЈЙ§anchor regionsжаЕФМФДцЦїНЋУПИіislandЕФаХКХСЌЦ№РДећКЯЕНећИіЩшМЦжаЁЃ

ЫљгаетаЉЛЎЗжКЭЦДНгБГКѓЕФФПЕФЪЧНЋHLSЩшМЦЗжИюГЩаЁПщЃЌНЛИЖИјЯжДњЗўЮёЦїжаЕФЖрИіКЫаФЁЃетжжВпТдвбОгагЦОУЕФРњЪЗЃЌЯждкБЛгУгкМгЫйFPGAЕФПЊЗЂЁЃ

етИіЙ§ГЬгаШ§ИіжївЊЕФHLSМЖдМЪј:

1ЁЂЗЧжиЕўЗжЧјЁЊЁЊВЂааЛЏВЛЭЌislandЕФЮяРэЪЕЯжЃЛ

2ЁЂСїЫЎЯпЛЏЕФislandМфСЌНгЁЊЁЊУПИіislandМфСЌНгЖМСїЫЎЯпЛЏЃЌвдТњзуЪБађвЊЧѓЃЛ

3ЁЂжБНгСЌНгЁЊЁЊУПИіislandжЛФмгыЯрСкЕФislandжБНгСЌНгЁЃЕБВЂааЛЏЩшМЦВМОжВМЯпЪБЃЌетИідМЪјЪЧжСЙиживЊЕФЁЃ

(зЂвт:етаЉдМЪјгыгУгкПижЦТпМзлКЯЕФИїжждМЪјЭъШЋВЛЭЌЃЌЫќДІгквЛИіИќИпЕФВуДЮЁЃ)

RapidStreamЕФПЊЗЂепНЋЪ§ОнСїЩшМЦЖЈвхЮЊвЛзщВЂааДІРэдЊЫи(processing elementЃЌМђГЦPE)КЭвЛзщИљОнЩшМЦЕФЪ§ОнСїашЧѓНЋPEСЌНгЦ№РДЕФFIFOЁЃPEФкВППЩвдКмИДдгЃЌЕЋжЛФмЭЈЙ§FIFOНгПкгыЦфЫћPEНјааЪ§ОнЭЈаХЁЃ

ШчЩЯЫљЪіЃЌRapidStreamНЋFPGA fabricЛЎЗжЮЊСНжжregionЃКДѓаЁЯрЭЌЕФregionКЭдкЯрСкregionжЎМфвдеСаКЭааЗХжУЕФanchor regionЁЃгаШЄЕФЪЧЃЌRapidStreamЫЦКѕЪЧзЈУХЮЊAMD-Xilinx Virtex UltraScale+ FPGAЙЙНЈЕФЃЌетЪЧгЩFPGAchipletЃЈAMD-XilinxгябджаЕФГЌМЖТпМЧјгђЃЌМђГЦSLRЃЉжЦГЩЕФ2.5DЦїМўЁЃ

етЦЊТлЮФАќКЌСЫМИИіУшЪіRapidStreamЙЄзїадФмЕФЭМБэЁЃЯТЭМЯдЪОСЫдкЗжЧјКѓЃЌСљжжВЛЭЌЕФЪ§ОнСїЩшМЦгыУЛгаЗжЧјЕФСїЫЎЯп/ЗЧСїЫЎЯпАцБОЪБжгЫйТЪЕФБШНЯЁЃ

ДгЩЯЭМПЩвдПДГіЃЌRapidStreamБШЫљгаЗЧСїЫЎЯпАцБОЕФЪБжгЫйТЪИќИпЁЃетЪЧвтСЯжЎжаЕФЃЌвђЮЊСїЫЎЯпЪЧFPGAЪБжгЫйЖШИФНјЕФКЫаФЁЃШЛЖјЃЌСљжжЧщПіжаЃЌгаЮхжжЧщПіRapidStreamЕФНсЙћБШЯрЭЌЩшМЦЕФСїЫЎЯпRTLАцБОвЊКУЃЌетИіНсЙћвЊв§Ц№ЮвУЧЕФзЂвтЁЃ

ЯТУцЪЧВМОжВМЯпЕФЪБМфНсЙћЖдБШ:

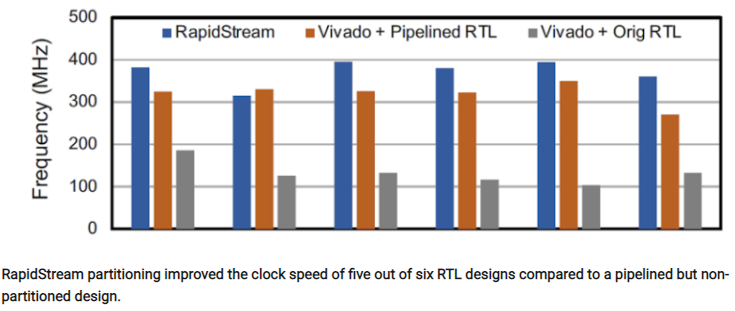

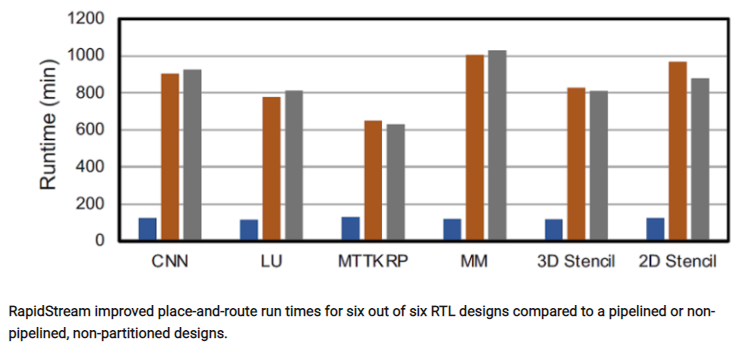

RapidStreamЕФВМОжВМЯпдЫааЪБМфБШЮДЗжЧјЩшМЦЕФНсЙћвЊКУЕУЖрЁЃетЪЧвђЮЊRapidStreamПЩвдНЋУПИіЗжЧјЫЭИјВЛЭЌЕФДІРэЦїКЫаФРДВМОжВМЯпЁЃ

ЫфШЛFPGAЙЉгІЩЬЪдЭМШУВМОжВМЯпЫуЗЈдкЖрКЫДІРэЦїЩЯЙЄзїЕУИќПьЃЌЕЋRapidStreamЕФПЊЗЂШЫдБИљОнОбщЗЂЯжЃЌШчЙћFPGAЩшМЦУЛгаЗжЧјЃЌдкГЌЙ§СНИіДІРэЦїКЫаФЩЯдЫааAMD-Xilinx VivadoЩшМЦЙЄОпЪБВЂУЛгаЬЋДѓИФЩЦЁЃ

ШчЙћгаЖСепе§дкгУFPGAПЊЗЂHLSЩшМЦЁЊЁЊЬиБ№ЪЧAMD-Xilinx FPGAЃЌФЧУДгІИУЛсЖдRapidStreamИааЫШЄЁЃИќЯИНкЕФФкШнПЩвддкGitHubЩЯевЕНЁЃ

дЮФБъЬтЃКHLSЗжЧјМгЫйFPGAВМОжВМЯпЃЁ

ЮФеТГіДІЃКЁОЮЂаХЙЋжкКХЃКSSDFansЁПЛЖгЬэМгЙизЂЃЁЮФеТзЊдиЧызЂУїГіДІЁЃ

ЩѓКЫБрМЃКЬРшїКь

-

FPGA

+ЙизЂ

ЙизЂ

1646ЮФеТ

22070фЏРРСП

619738 -

Xilinx

+ЙизЂ

ЙизЂ

73ЮФеТ

2185фЏРРСП

125726 -

ВМОжВМЯп

+ЙизЂ

ЙизЂ

1ЮФеТ

89фЏРРСП

15396 -

HLS

+ЙизЂ

ЙизЂ

1ЮФеТ

133фЏРРСП

24960

дЮФБъЬтЃКHLSЗжЧјМгЫйFPGAВМОжВМЯпЃЁ

ЮФеТГіДІЃКЁОЮЂаХКХЃКSSDFansЃЌЮЂаХЙЋжкКХЃКSSDFansЁПЛЖгЬэМгЙизЂЃЁЮФеТзЊдиЧызЂУїГіДІЁЃ

ЗЂВМЦРТлЧыЯШ ЕЧТМ

ЛљгкFPGAЕФбЙЫѕЫуЗЈМгЫйЪЕЯж

ШчКЮдкUnified IDEжаДДНЈЪгОѕПтHLSзщМў

ЪЙгУAMD Vitis Unified IDEДДНЈHLSзщМў

ШчКЮЪЙгУAMD Vitis HLSДДНЈHLS IP

LinuxЯЕЭГжаЭЈЙ§дЄСєЮяРэФкДцЪЕЯжARMгыFPGAИпаЇЭЈаХЕФЗНЗЈ

Vivado HLSЩшМЦСїГЬ

ШчКЮЪЙгУFPGAЧ§ЖЏВЂааADCКЭDACаОЦЌЃЌЪЙгУВЛЭЌБрТыЗНЪНЕФADCгыDACЪБЕФзЂвтЪТЯю

FPGA+AIЭѕеЈзщКЯШчКЮжиЫмЮДРДЪРНчЃКПДПДDeepSeekЖЋЗНЩёУиСІСПШчКЮдЄВт......

ЪЙгУHLSСїГЬЩшМЦКЭбщжЄЭМЯёаХКХДІРэЩшБИ

ЛљгкFPGAЪЕЯжЭМЯёжБЗНЭМЩшМЦ

RapidStream:FPGA HLSЩшМЦЕФВЂааЮяРэЪЕЯж

RapidStream:FPGA HLSЩшМЦЕФВЂааЮяРэЪЕЯж

ЦРТл