PCIe Express Gen6 基本规范已经发布,供应链与我写上一篇文章时大不相同。所以现在是重新审视“面向未来”的好时机。当系统设计人员谈论未来的验证时,我们指的是为多代产品重复使用设计的尝试。有时这意味着预测某些技术的发展,这样一个人的项目就不会过早地过时。也就是说,有些事情是无法预料的。对于瑞萨来说,当前供应链环境中的未来验证包括为新设备选择具有足够上行能力的工艺节点。

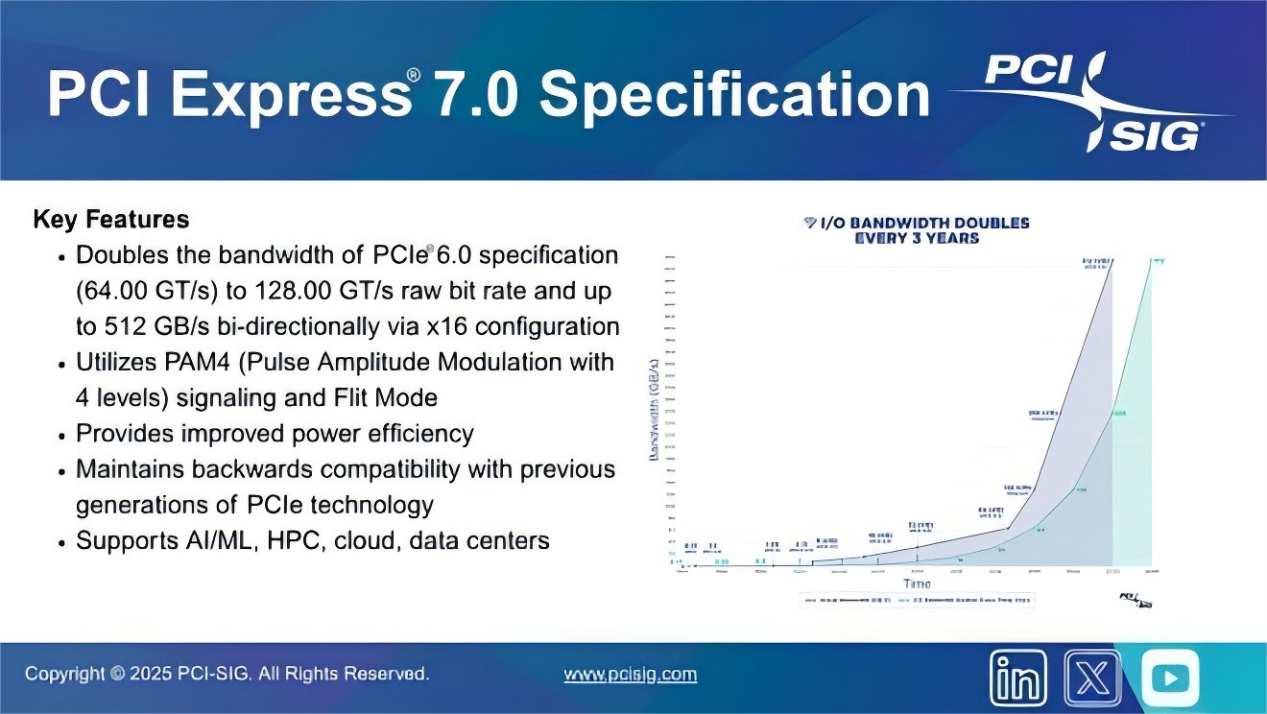

在之前的博客文章中,比较和对比 PCIe 和以太网时钟抖动规范,我提到 PCI SIG 正在以更快的速度发布新规范。Gen3 和 Gen4 规范发布之间的 7 年间隔长得令人无法接受。Gen5 规范在 Gen4 之后不到 2 年发布,Gen6 规范在 2022 年 1 月发布,距离 Gen5 规范发布不到 3 年。

这种更快的速度如何影响未来的打样?在 PCIe Gen3 系统上市之前,PCIe Gen2 系统中使用的计时设备可以使用近十年。十年的重复使用非常具有成本效益。新 PCIe 规范的更快发布意味着支持新规范的系统的更快发布。这意味着设计很可能可以在更短的时间内重复使用。当瑞萨电子设计 PCIe 时钟芯片时,我们总是试图超越提出的性能规格。我们为 PCIe Gen3 ( 9FGL02 / 04 / 06 / 08 ) 设计的几个时钟支持 PCIe Gen4 和 Gen5。我们的许多 PCIe Gen4 时钟支持 PCIe Gen5 和 PCIe Gen6 ( 9FGV1002 /9FGV1006)。我们新的9SQ440服务器主时钟,旨在支持 PCIe Gen5,还支持 PCIe Gen6,有余量(40fs RMS 相对于 100fs RMS 规格限制)。由于较新的 PCIe 代始终向后兼容较旧的代,因此这些较新的设备也可用于支持较旧的设计。瑞萨电子和我们的客户都享有以下优势:

客户可以提高当今系统的性能余量,并可以继续将这些部件用于下一代设计。这降低了采购成本、鉴定工作和设计时间。

瑞萨电子可以增加时钟芯片的使用寿命,提高可靠性并带来额外的供应链优势,这些优势也惠及我们的客户。

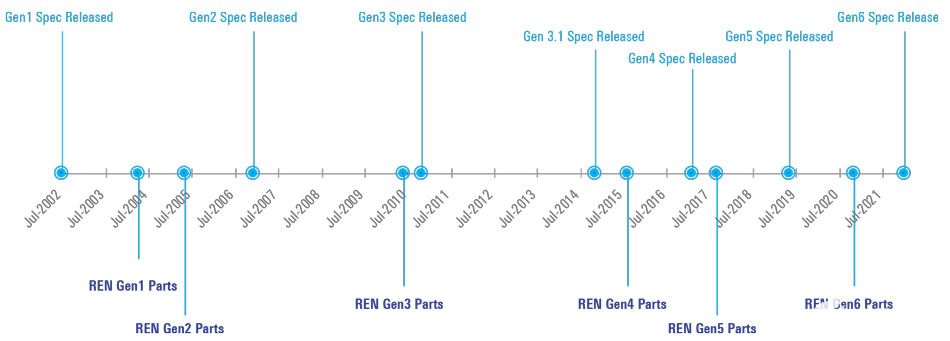

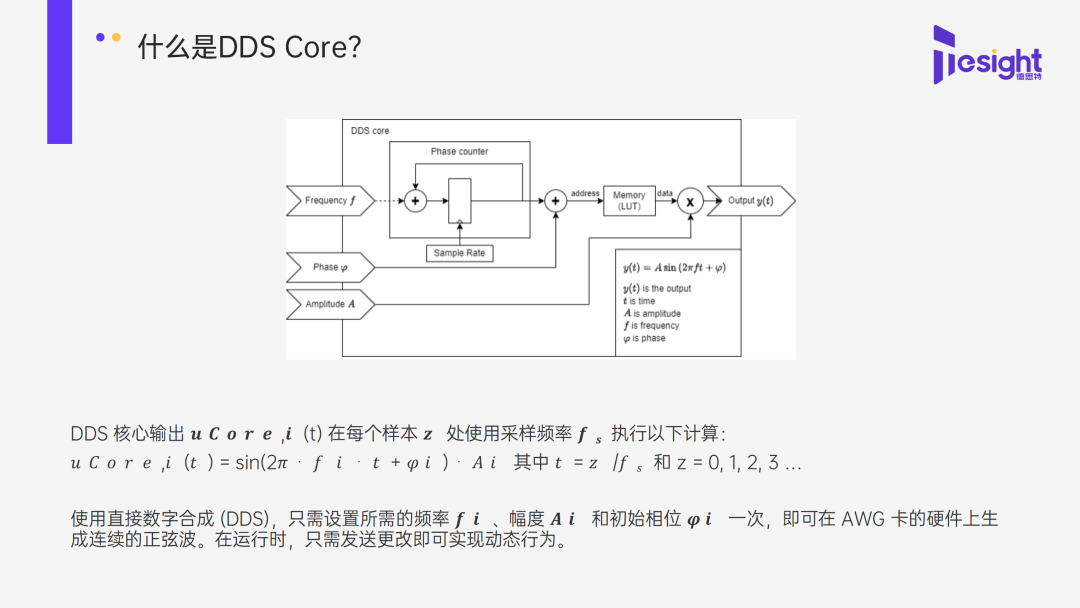

图 1 显示了 PCI Express 自开发以来的时间线。时间线的上半部分列出了每个 PCIe 规范的发布日期。下半部分显示了瑞萨电子每代符合 PCIe 标准的时钟的上市日期。一般来说,时钟在规格发布之前就已经可用。迄今为止,PCIe Gen1 是个例外,当时整个行业都在将全新的技术生态系统推向市场。

图像

图 1:PCI Express 开发时间表

从发布 PCI Express 规范到部署兼容系统之间的时间可能很长,在某些情况下可能需要数年。如图 1 所示,瑞萨在 2015 年底推出了符合 PCIe Gen4 标准的部件,PCIe Gen4 规范于 2017 年底发布,PCIe Gen4 系统于 2019 年年中开始出货。当我们拥有符合未发布规范的设备时,我们注意到它们已为下一代做好准备。我们在 2015 年底推出的设备被描述为支持 Gen4。2017 年,我们发布了支持 Gen5 的设备,并在 2020 年推出了支持 Gen6 的部件。今天,我们推出了符合 Gen6 标准的设备,并且正在关注 Gen7!

时钟芯片不仅仅是抖动性能。为了说明这一点,我想用一个跑车类比。跑车比马力更重要。制动能力、转向和牵引力都会影响汽车在赛道上的速度。德国有一条公路赛道,叫做纽博格林。高性能汽车制造商在这条赛道上开发汽车。快速跑步需要动力、制动、转向、牵引力和可预测的行为。来自特定制造商的 2015 年型号在 7 分 20 秒 (7:20) 内完成了课程。这辆车的发动机产生了 368kW(493hp)的功率。同一辆车的 2018 年车型配备可产生 383 千瓦(513 马力)的发动机,并在制动、操控和牵引力方面进行了多项改进。它在 6:56.4 运行相同的课程!

类比适用于瑞萨的时序。时钟芯片还有更多的抖动性能。在异常条件下提供可预测行为的特性、减少的传播延迟、严格的输出到输出偏差和出色的抖动性能都有助于实现面向未来的时钟设计。查看新的RC19024 / 20 / 16 / 13 / 08 / 04系列时钟缓冲器和RC19216 / 08 / 04 / 02系列时钟多路复用器,了解一些出色的示例。

关于作者:罗恩·韦德

审核编辑:郭婷

-

芯片

+关注

关注

460文章

52616浏览量

442701 -

PCIe

+关注

关注

16文章

1350浏览量

85567

发布评论请先 登录

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

nvme IP开发之PCIe上

Diodes公司PCIe 6.0时钟缓冲器介绍

面向未来 三星构建移动安全防护体系

面向Switchtec和数据中心应用的预配置时钟发生器器件编号

面向科学计算,第五代英特尔至强可扩展处理器优势何在

面向未来的低压侧数智电网监控方案

PCIe的最新发展趋势

PCIe 4.0与PCIe 3.0的性能对比

Cadence展示完整的PCIe 7.0 IP解决方案

PCIe助于实现面向未来的时钟设计

PCIe助于实现面向未来的时钟设计

评论