STM32中的GPIO

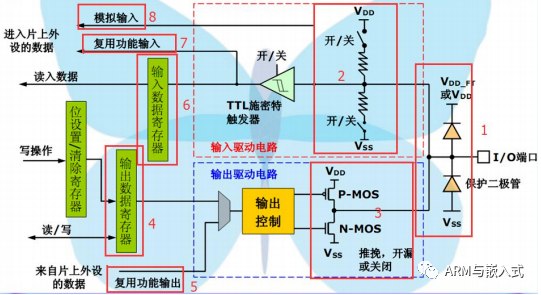

以STM32中的GPIO为例,如上图是GPIO的结构图。

从上图中标号2处可以看到,上拉和下拉电阻上都有一个开关,通过配置上下拉电阻开关,可以控制引脚的默认电平,这里有三种状态:

开启上拉时,引脚默认电压为高电平

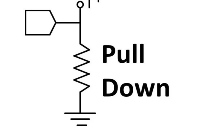

开启下拉时,引脚默认电压为低电平

上拉和下拉不开启时,这种状态我们称为浮空模式

关于STM32的GPIO文章,请移步此处:STM32的GPIO电路原理。STM32上下拉及浮空模式的配置是通过GPIOx_CRL和GPIOx_CRH寄存器控制的,可以通过《STM32F1xx 中文参考手册》查阅。

开启上拉电阻或下拉电阻的作用

STM32内部的上拉其实是一个弱上拉,也就是说通过此上拉电阻输出的电流很小,如果想要输出一个大电流。那么就需要外接上拉电阻了,其实就是增加导线的输出电流。

下拉电阻情况相反,让STM32的CPU引脚输出低电平,结果由于后续电路影响输出的低电平达不到GND。所以接个下拉电阻,其实就是为了降低导线的输出电流。

另外当上下拉电阻都不开启,此时是浮空模式,引脚的电压是不确定的,此模式下的管脚电压会时不时改变。

所以为了防止引脚悬空,产生积累电荷、静电荷,造成电路不稳定。一般情况下,我们都会给引脚设置成上拉或者下拉模式,使它有一个确定的默认电平状态。

以上拉电阻举例,在STM32刚上电的时候,芯片引脚电平是不确定的。特别引脚是接按键的时候,必须给他个确定的电平。下拉电阻的作用就是,强制让电平保持在低电平。

上下拉电阻阻值的大小

根据拉电阻的阻值大小,可以分为强拉或弱拉(weak pull-up/down)。拉电阻阻值越小则表示电平能力越强,为强拉,可以抵抗外部噪声的能力也越强,相应的功耗也越大。

举个例子:

按键的上拉电阻可以选择3.3k、4.7k、5.1k、10k等,但是电阻越小,电流越大,功耗也越大。10k的上拉电阻带来的电流,是大多数芯片所能识别到的引脚电流,如果电阻太大,电流太小,引脚识别不了,所以10k是个折中的方案。这里的电流,简单来说是根据公式VDD/R拉电阻计算出来的。

编辑:jq

-

电阻

+关注

关注

87文章

5637浏览量

175563 -

STM32

+关注

关注

2295文章

11035浏览量

366026 -

GPIO

+关注

关注

16文章

1283浏览量

54297

原文标题:通俗理解STM32中的上/下拉电阻

文章出处:【微信号:c-stm32,微信公众号:STM32嵌入式开发】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CYW5557x 上的内部上拉/下拉电阻值是多少?

浮思特 | 电子电路下拉电阻详解:原理、计算与应用指南

请问ADS1278配置管脚的上拉下拉电阻阻值选择多少?

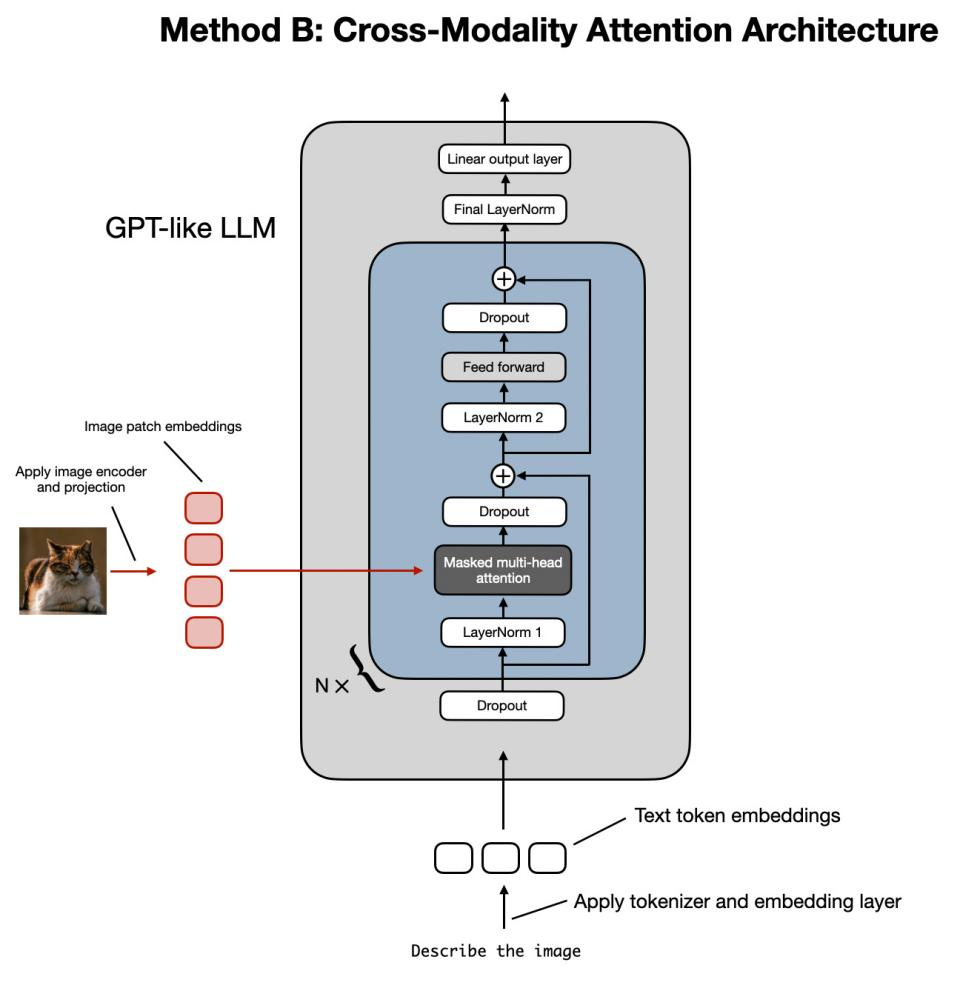

一文理解多模态大语言模型——下

DAC101S101初次上电瞬间下拉电阻的开关是默认闭合的吗?

【RS-485总线】详解RS-485上下拉电阻的选择

一文快速理解STM32中的上/下拉电阻

一文快速理解STM32中的上/下拉电阻

评论