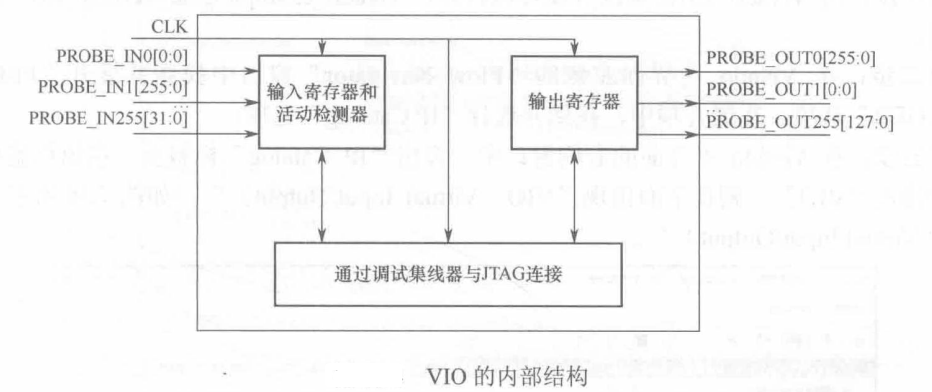

可以定制VIO的输入和输出端口的数量与宽度,用于和FPGA设计进行连接。由于VIO核与被监视和驱动的设计同步,因此应用于设计的时钟约束也适用于VIO核内的元件。当使用这个核进行实时交互时,需要使用Vivado逻辑分析特性。

接下来将介绍VIO的原理及应用,内容主要包括设计原理、添加VIO核、生成比特流文件和下载并调试设计。

设计原理

设计以下源码的工程,并添加VIO核:

`timescale1ns/1ps

//////////////////////////////////////////////////////////////////////////////////

//Company:

//Engineer:

//

//CreateDate:2021/08/222358

//DesignName:

//ModuleName:top

//ProjectName:

//TargetDevices:

//ToolVersions:

//Description:

//

//Dependencies:

//

//Revision:

//Revision0.01-FileCreated

//AdditionalComments:

//

//////////////////////////////////////////////////////////////////////////////////

moduletop(

inputclk,

inputa,

inputb,

outputreg[5:0]z

);

reg[5:0]z_tmp;

wire[5:0]z_vio;

rega_tmp,b_tmp;

wirea_in,b_in;

wiresel;

wirea_vio,b_vio;

assigna_in=sel?a:a_vio;

assignb_in=sel?b:b_vio;

assignz_vio=z;

vio_0Inst_vio(

.clk(clk),//inputwireclk

.probe_in0(z),//inputwire[5:0]probe_in0

.probe_out0(sel),//outputwire[0:0]probe_out0

.probe_out1(a_vio),//outputwire[0:0]probe_out1

.probe_out2(b_vio)//outputwire[0:0]probe_out2

);

always@(posedgeclk)

begin

a_tmp<=a_in;

?b_tmp<=b_in;

end?

always?@(*)

begin

?z_tmp[0]=a_tmp?&?b_tmp;

?z_tmp[1]=~(a_tmp?&?b_tmp);

?z_tmp[2]=a_tmp?|?b_tmp;

?z_tmp[3]=~(a_tmp?|?b_tmp);

?z_tmp[4]=a_tmp?^?b_tmp;

?z_tmp[5]=a_tmp?~^?b_tmp;

end?

always?@(posedge?clk)

begin

z<=z_tmp;

end?

endmodule

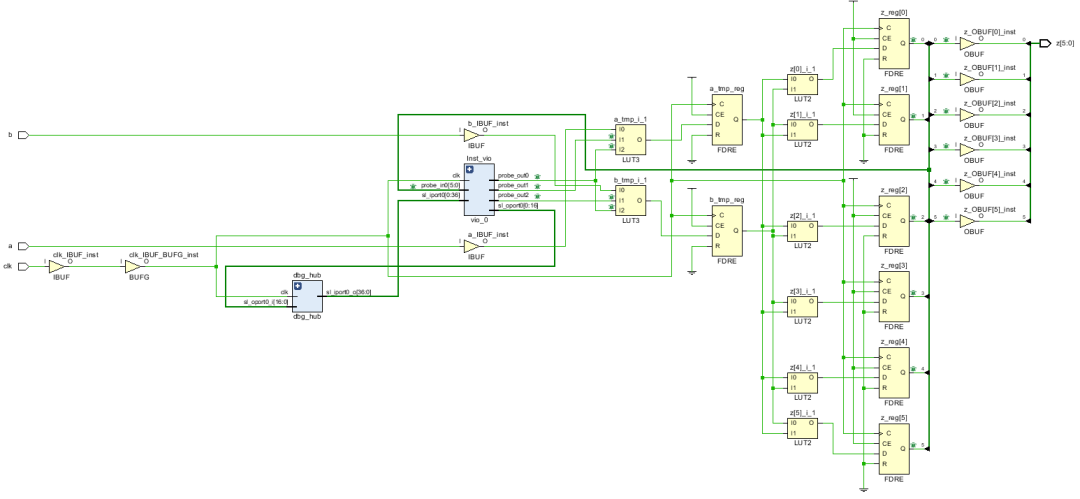

添加VIO后的整体设计如下:

如上图所示,在该设计中添加一个vio核,该IP提供3个输出端口,其中probe_out0端口用于选择进入寄存器a_tmp_reg和寄存器b_tmp_reg的信号。当probe_out0输出1时,将外部端口a和b提供的信号分别连接到寄存器a_tmp_reg和寄存器b_tmp_reg;当probe_out0输出0时,将vio输出端口probe_outl和probe_out2信号连接到寄存器a_tmP_reg和b_tmp_reg。这样就可以通过vio提供的端口来控制整个FPGA的设计。此外,FPGA设计的最终输出z可以连接到vio模块的probe_in0输入端口。

添jia VIO核

本节将添加VIO核,主要步骤如下所示。

第一步:用Vivado集成开发环境打开需要添加的工程。

第二步:在Vivado主界面左侧的“Flow Navigator”窗口中找到并展开PROJECT MANAGER选项。在展开项中,找到并选择“IP Catalog”选项。

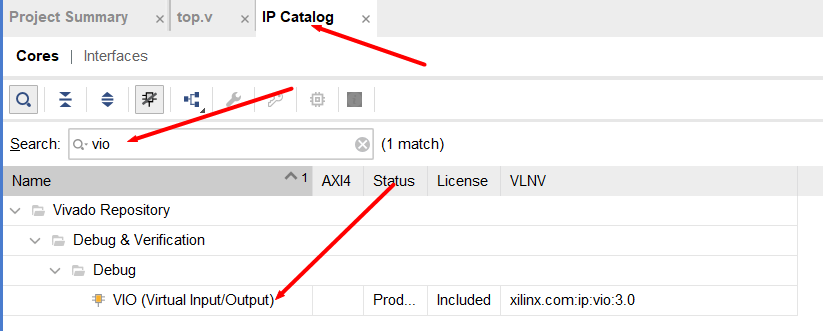

第三步:在Vivado主界面的右侧窗口中,弹出“IP Catalog”标签页。在该标签页的搜索框中输入“VIO”,则在下面出现“VIO(Virtual Input/Output)”,如图所示,双击“VIO(Virtual Input/Output)”。

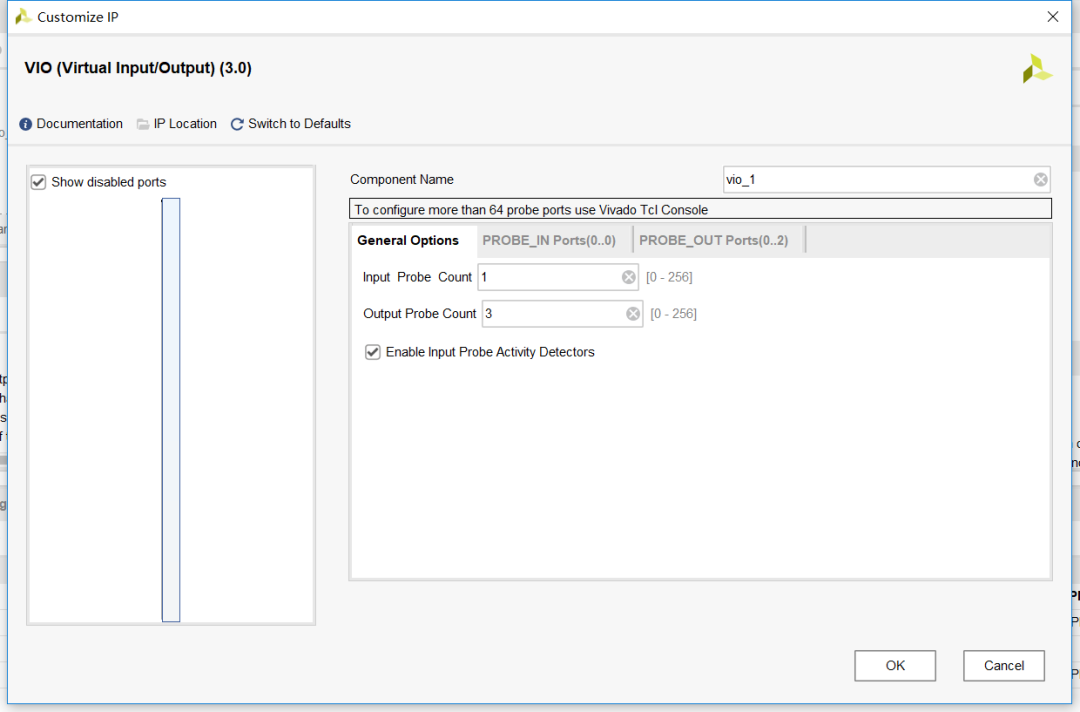

第四步:弹出“Customize IP-VIO(VirtualInput/Output)”对话框。

(1)单击“General Options”标签,如图所示,在该标签页中,按如下参数进行设置。

Input ProbeCount:1。

Output ProbeCount:3。

勾选 Enable Input Probe Activity Detectors前面的复选框。

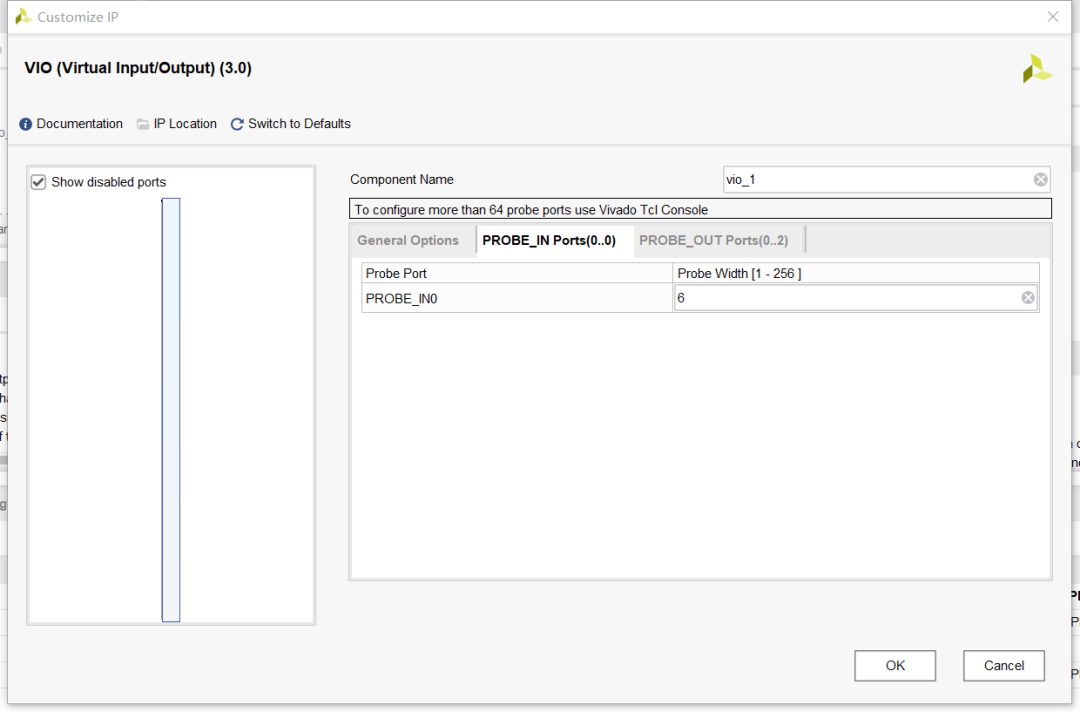

(2)单击“PROBE_IN Ports(0..0)”标签,如图所示,在该标签页中,按如下参数进行设置

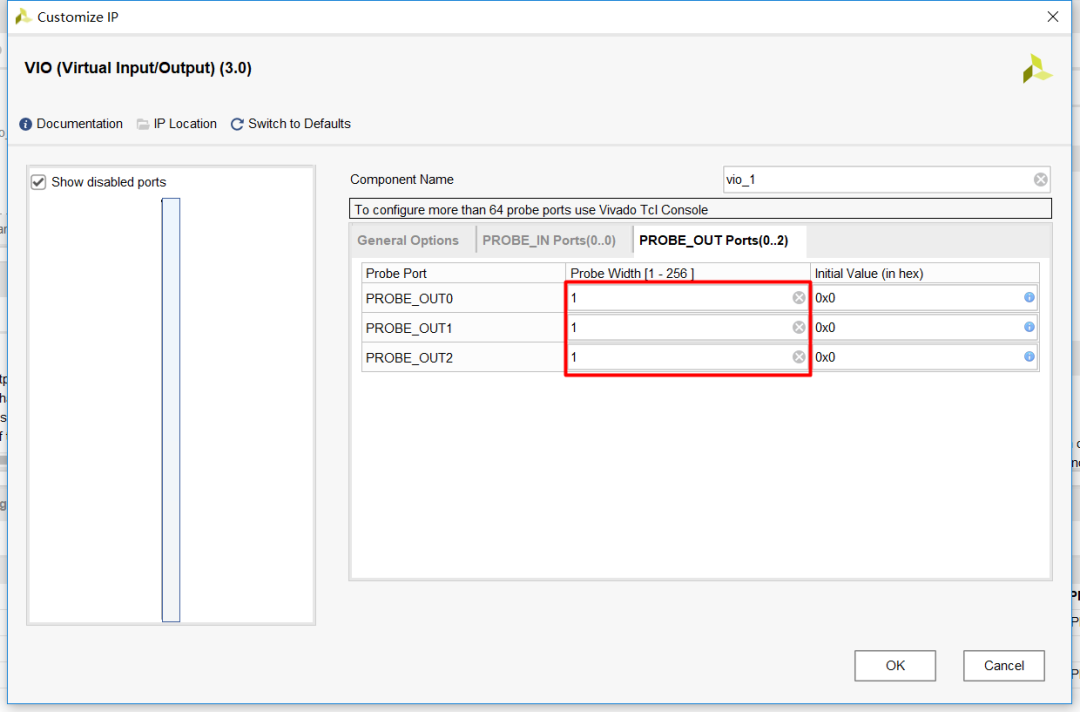

(3)单击“PROBE_OUTPorts(0..2)”标签,如图所示,在该标签页中,按如下参数进行设置。

第五步:单击【OK】按钮,退出“Customize IP”对话框。

第六步:弹出“Generate Output Products”对话框。

第七步:单击【Generate】按钮,退出“Generate Output Products”对话框。

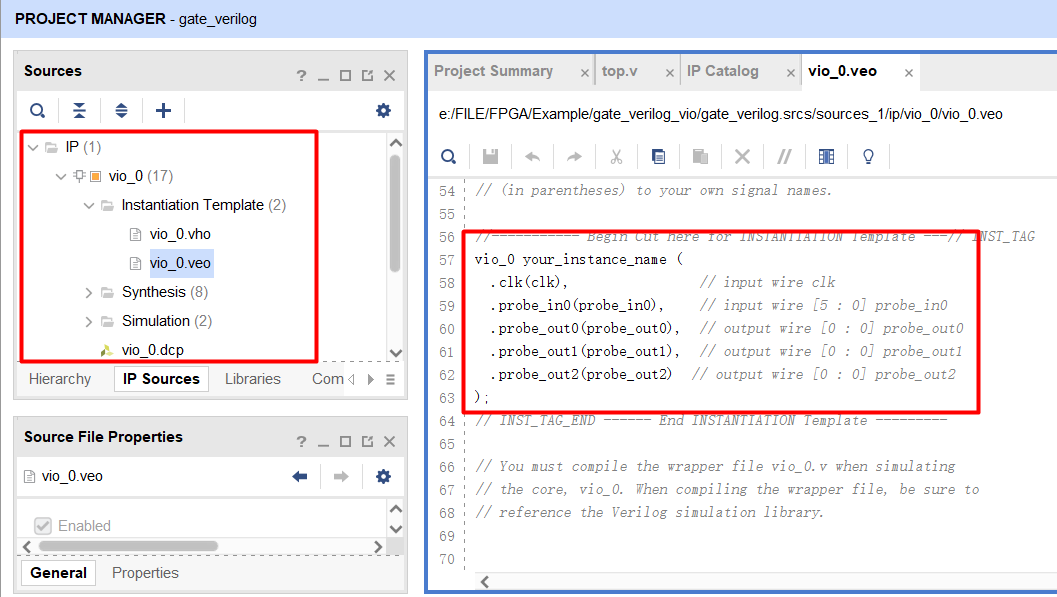

第八步:在“Sources”窗口中,单击“IP Sources”标签。在该标签页中,可以看到添加了名字为“vio_0”的IP核实例,如图所示。找到并展开“vio_0”选项。在展开项中,找到并展开“Instatiation Template”选项。在展开项中,选择并用鼠标左键双击vio_0.veo,打开其例化模板,如下述代码所示。

//-----------BeginCuthereforINSTANTIATIONTemplate---//INST_TAG

vio_0your_instance_name(

.clk(clk),//inputwireclk

.probe_in0(probe_in0),//inputwire[5:0]probe_in0

.probe_out0(probe_out0),//outputwire[0:0]probe_out0

.probe_out1(probe_out1),//outputwire[0:0]probe_out1

.probe_out2(probe_out2)//outputwire[0:0]probe_out2

);

第九步:在“Sources”窗口中,单击“Hierarchy”标签。在该标签页中,找到并展开“Design Sources”选项。在展开项中,找到并用鼠标双击top.v文件,按下述代码修改设计代码,并添加vio的例化代码。

`timescale1ns/1ps

//////////////////////////////////////////////////////////////////////////////////

//Company:

//Engineer:

//

//CreateDate:2021/08/222358

//DesignName:

//ModuleName:top

//ProjectName:

//TargetDevices:

//ToolVersions:

//Description:

//

//Dependencies:

//

//Revision:

//Revision0.01-FileCreated

//AdditionalComments:

//

//////////////////////////////////////////////////////////////////////////////////

moduletop(

inputclk,

inputa,

inputb,

outputreg[5:0]z

);

reg[5:0]z_tmp;

wire[5:0]z_vio;

rega_tmp,b_tmp;

wirea_in,b_in;

wiresel;

wirea_vio,b_vio;

assigna_in=sel?a:a_vio;

assignb_in=sel?b:b_vio;

assignz_vio=z;

vio_0Inst_vio(

.clk(clk),//inputwireclk

.probe_in0(z),//inputwire[5:0]probe_in0

.probe_out0(sel),//outputwire[0:0]probe_out0

.probe_out1(a_vio),//outputwire[0:0]probe_out1

.probe_out2(b_vio)//outputwire[0:0]probe_out2

);

always@(posedgeclk)

begin

a_tmp<=a_in;

?b_tmp<=b_in;

end?

always?@(*)

begin

?z_tmp[0]=a_tmp?&?b_tmp;

?z_tmp[1]=~(a_tmp?&?b_tmp);

?z_tmp[2]=a_tmp?|?b_tmp;

?z_tmp[3]=~(a_tmp?|?b_tmp);

?z_tmp[4]=a_tmp?^?b_tmp;

?z_tmp[5]=a_tmp?~^?b_tmp;

end?

always?@(posedge?clk)

begin

z<=z_tmp;

end?

endmodule

第 十 步 :保 存 该 设 计 文 件 。

生成比特流文件

下载并调试设计

将生成的比特流文件下载到开发板上的FPGA元器件中,并通过VIO对设计进行监控,主要步骤如下所示。

第一步:将JTAG和FPGA板卡链接并和PC连接。

第二步:给开发板上电。

第三步:在“HARDWARE MANAGER”对话框中,单击【Open target】按钮,出现浮动菜单。在浮动菜单内,执行菜单命令【AutoConnect】。

第四步:在“Hardware”窗口中,选择FPGA,单击鼠标右键,出现浮动菜单。在浮动菜单内,执行菜单命令【Program Device】。

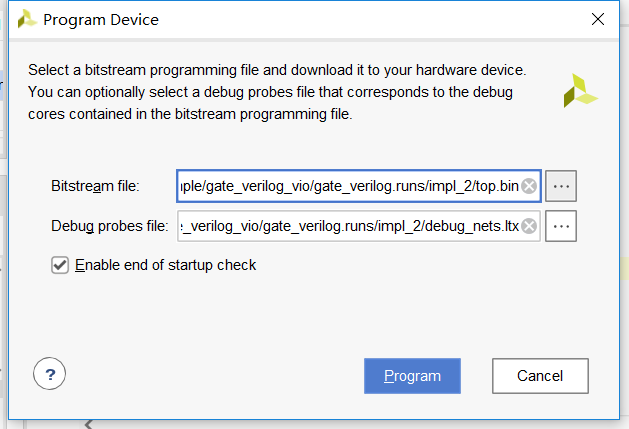

第五步:弹出“Program Device”对话框,如图所示。在该对话框中,选择合适的“Bit stream file”和“Debug probes files”。

第六步:单击【Program】按钮。

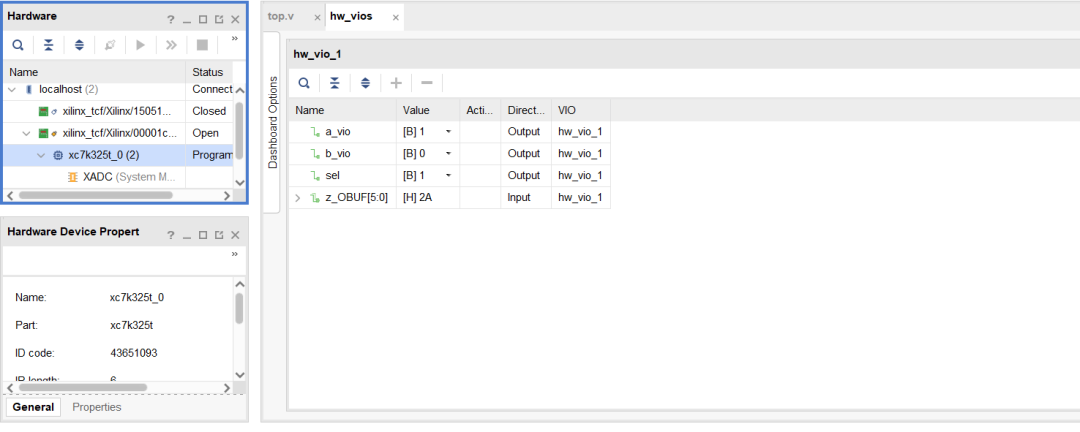

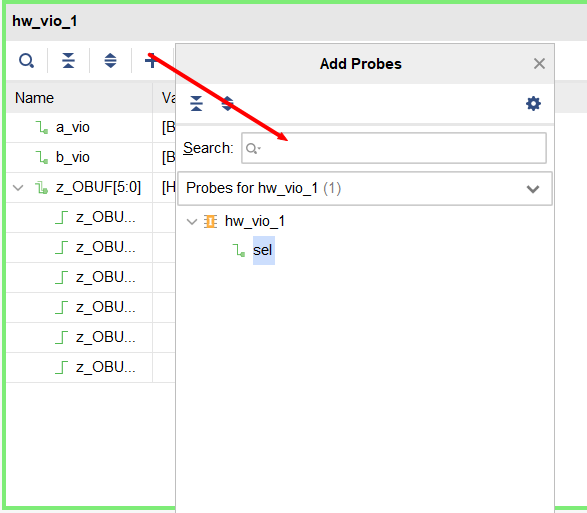

第七步:在Vivado主界面右侧的窗口中,弹出“hw_vio_l”对话框,如图所示。在该对话框中,单击+按钮。出现浮动菜单。在浮动菜单内,分别双击a_vio、b_vio、sel和z_OBUF[5:0],将其添加到“hw_vio_l”对话框中,如图所示。

第八步:在图所示的对话框中,先将sel的“Value”设置为1,此时a_vio和b_vio的值将送给FPGA设计。

第九步:在图所示的对话框中,将“sel”的“Value”设置为0,此时由开发板上开关的设置状态确定a和b的值,并将其送给FPGA设计。

第十步:关闭并退出设计。

-

FPGA

+关注

关注

1646文章

22072浏览量

619834 -

JTAG

+关注

关注

6文章

404浏览量

73472 -

代码

+关注

关注

30文章

4906浏览量

71030 -

VIO

+关注

关注

0文章

11浏览量

10436

原文标题:【Vivado那些事儿】-VIO原理及应用

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Vivado无法选中开发板的常见原因及解决方法

FPGA调试方式之VIO/ILA的使用

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

Vivado Design Suite用户指南:逻辑仿真

TCAN1051HGV VIO管脚作用是什么?

一种降低VIO/VSLAM系统漂移的新方法

每次Vivado编译的结果都一样吗

Vivado使用小技巧

深入了解基于CANoe的VIO系统应用

Vivado之VIO原理及应用

Vivado之VIO原理及应用

评论