“先进封装”是半导体产业近年来的热词之一,也掀起了封装技术发展史上的第三次技术跃进。有人对它有一个形象比喻“摊大饼不行了,做一下千层饼试试吧”。 为什么这么说?以2.5D、3D封装为代表的、结合了芯片堆叠和异构封装等技术的先进封装,正在为摩尔定律指挥棒下的芯片实现争取更优方案。<与非网>对话英特尔院士/封装研究与系统解决方案总监Johanna Swan,就先进封装的关键技术、发展方向等问题进行了深入交流。

为什么需要先进封装?

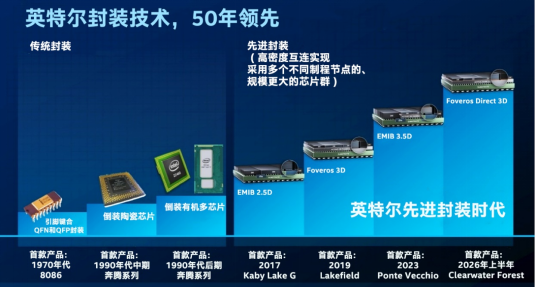

多年来,业界并没有在先进封装上投入太多精力,但近年来情况发生了变化。Johanna Swan指出,由于先进封装技术能够集成多种制程工艺的计算引擎,实现类似于单晶片的性能,但其平台范围远远超过单晶片集成的晶片尺寸限制。这些技术将大大提高产品级性能和功效,缩小面积,同时对系统架构进行全面改造。正因如此,先进封装成为各公司打造差异化优势的一个重要领域,以及提升性能、提高功率、缩小外形尺寸和提高带宽的机会。

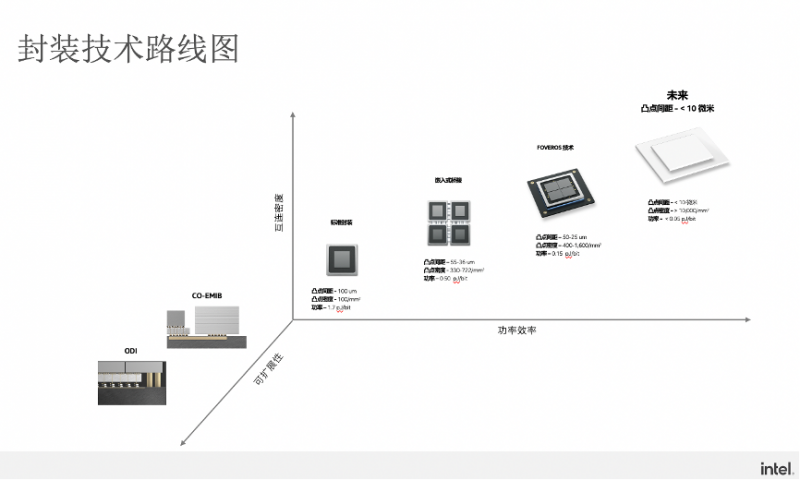

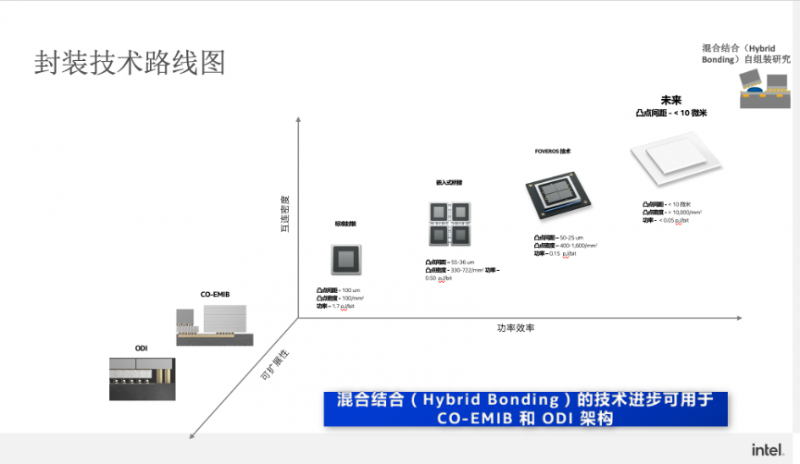

从Intel 的先进封装技术路线图可以看出,三大维度是未来方向:X轴代表功率效率,Y轴代表互连密度,Z轴代表可扩展性。

多区块异构集成提升功率效率

Johanna Swan介绍,单独IP的异构集成能够带来更大量的更小区块,它们可以大量重复使用,开发时间从单片式集成SoC的3-4年、多晶片2-3年缩短至1年,并且芯片缺陷率进一步降低。这样一来,便于根据客户的独特需求定制产品,满足产品快速的上市需求。

多区块异构集成能够解决芯片设计和制造的诸多限制,但与此同时,它所带来的影响也是深远的,主要体现在两方面:一是晶片间互连的微缩从焊接转到混合结合(Hybrid Bonding),二是大量区块转变到按批次组装的精确放置,这样又带来了新的挑战。

大量区块如何保持制造流程以相同的速度进行?有更多的晶片需要放置,能否在一次只放置一个晶片的基础上加快速度?英特尔正在考虑的解决方案是批量组装/自组装。

目前,英特尔正在与法国原子能委员会电子与信息技术实验室(CEA-LETI)合作,研究一次放置多个晶片,进行确定性对齐,并使用超小的晶片,进行快速放置,通过批次组装,实现拾取更多、并放置更多晶片。Johanna Swan通过一个视频介绍了自组装的大概机制:把晶片放在一个能够将自身恢复到最低能量状态的位置,这时就不需要设备,只需要让它足够接近、试图达到最低限度的能量状态时,就会自己组装、放置到位。在英特尔的封装技术路线图中,最新增加了混合结合自组装研究为未来的方向。

为异构计算而生的混合结合技术

在英特尔的封装技术路线中,混合结合是一种在相互堆叠的芯片间获得更密集互连的方法,并且能够帮助实现更小的外形尺寸。

当前的Foveros技术能实现的是凸点间距 50 微米,这将使每平方毫米有大约 400 个凸点。 由于面积随着凸点间距在微缩,未来,英特尔希望能缩减到大约 10 微米的凸点间距,达到每平方毫米 10000 个凸点。 这样,就可以实现更小、更简单的电路,更低的电容和功耗,实际上可以进行相互叠加,不必做扇入(fan-in)和扇出(fan-out)。

Johanna Swan表示,混合结合可以说是为异构计算而生的,主要有两大原因:第一,大多数封装技术中使用的是传统的“热压结合(thermocompression bonding)”技术,而混合结合技术是这一技术的替代品。这项新技术能够加速实现10微米及以下的凸点间距,提供更高的互连密度、带宽和更低的功率。

第二,先进的处理系统需要高带宽和子系统(处理器、片上网络和处理元件)之间的低功耗互连。传统上,这些子系统都是单片集成在一个芯片上。随着异构集成技术的发展,单片集成已经不再适用。扩大芯片之间的互连间距对于异构计算的发展非常重要,而混合结合技术就是解决这一问题的重要技术之一。

混合结合技术已经应用于诸如像图像传感器和非易失性存储器等应用,目前,它的商业应用还局限于晶圆与晶圆之间的结合,并且只能在低能耗的系统中。未来,混合结合会扩展到晶片与晶圆的应用中,以支持计算chiplet、内存chiplet的灵活异构集成,以及未来更高能耗的系统中。

Johanna Swan强调,定制将是下一阶段异构集成的重要驱动力。通过将更多不同的节点或 IP 组合,在不同的制程或节点上进行集成,通过这种混合搭配,可以为特定客户进行深度定制。

可扩展性是先进封装的重要维度

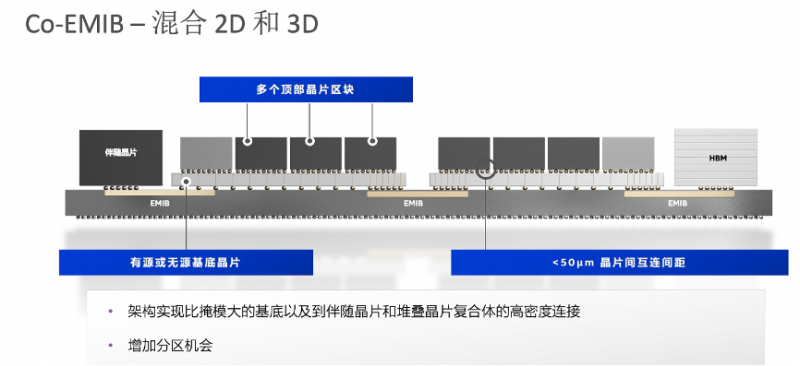

可扩展性是英特尔先进封装路线的又一个维度,在这个维度上,ODI和CO-EMIB是两大关键技术。

英特尔构建高密度MCP的关键基础技术包括EMIB、Foveros和Co-EMIB。其中,EMIB(嵌入式多芯片互连桥接)2D封装和Foveros 3D封装技术利用高密度的互连技术,能够实现高带宽、低功耗,并实现相当有竞争力的I/O密度。Co-EMIB则融合了2D和3D,将更高的计算性能和能力连接起来,基本达到单晶片性能。

FOVEROS技术前文已提到过,它作为当前的混合结合技术方式,能够为密度更高的垂直互连实现更小的尺寸。

那么,ODI又是什么技术呢?它是英特尔全新的全方位的互连技术,能够为封装中小芯片之间的全方位互连通信提供灵活性。顶部芯片可以像EMIB技术下与其他小芯片进行水平通信;同时还可以像Foveros技术下,通过硅通孔(TSV)与下面的底部裸片进行垂直通信。这种方法减少了基底晶片中所需的硅通孔数量,为有源晶体管释放了更多的面积,并优化了裸片的尺寸。

极致的异构集成是半导体封装未来趋势

谈到先进封装,小芯片Chiplet是一个必须要探讨的话题。Johanna Swan认为,小芯片最重要的事情是它能够帮助我们获得越来越小的IP。一旦拥有较小的 IP,它就可以混合在众多产品中,这可以具有非常高的重用水平,可以根据放入封装中的产品进行深度定制。

而定制将是实现下一阶段异构集成的驱动力,通过将更多不同的节点或 IP 组合,在不同的制程或节点上进行集成, 通过这种混合搭配,可以为特定客户进行深度定制。

她强调,极致的异构集成是方向,也是封装技术的未来趋势。封装技术将继续具有缩小尺寸的特征,能够将越来越小的 IP 和越来越小的区块集合在一起。归根结底,我们拥有的发展机会是在每毫米立方体上提供最多的区块并获得每毫米立方体最多的功能,所以我们还没有走到极限。封装将继续小型化和缩小尺寸,以便获取有限体积内的最大功能。

-

异构集成

+关注

关注

0文章

39浏览量

2108

发布评论请先 登录

英特尔先进封装,新突破

英特尔先进封装:助力AI芯片高效集成的技术力量

详细解读英特尔的先进封装技术

英特尔代工在IEDM 2024展示多项技术突破

英特尔展示互连微缩技术突破性进展

半导体三巨头格局生变:英特尔与三星面临挑战,台积电独领风骚

英特尔分析新质生产力发展的趋势和机遇

英特尔获78.6亿美元美国芯片补贴

英特尔王锐:算力驱动数字经济发展 成都封装厂扩容加强本土供应链和客户支持

英特尔院士Johanna Swan:极致的异构集成是半导体封装未来趋势

英特尔院士Johanna Swan:极致的异构集成是半导体封装未来趋势

评论