最近,关于台积电的先进封装有很多讨论,让我们透过他们的财报和最新的技术峰会来对这家晶圆代工巨头的封装进行深入的介绍。

资料显示,在张忠谋于2011年重返公司之后,就下定决定要做先进封装。而1994年加入公司的余振华就是台积电这个“秘密”项目的带头人。CoWoS技术则是台积电在这个领域的小试牛刀。他们这个技术首先在Xilinx的FPGA上做了实现,而基于此衍生的InFO封装则在苹果处理器上大放异彩,并从此让台积电的封装名扬天下。

台积电先进封装技术科普

据Semiwiki报道,去年,台积电将他们的 2.5D 和 3D 封装产品合并为一个单一的、全面的品牌3DFabric。

其中,2.5D封装技术CoWoS可分为 CoWoS 和 InFO 系列。首先看CoWoS技术,可以分为以下几种:

1、CoWoS-S

用于die到die再分布层 (redistribution layer:RDL) 连接的带有硅中介层的“传统”基板上晶圆上芯片(chip-on-wafer-on-substrate with silicon interposer )正在庆祝其大批量制造的第 10 年。

2、CoWoS-R

CoWoS-R 选项用有机基板中介层取代了跨越 2.5D die放置区域范围的(昂贵的)硅中介层。CoWoS-R 的折衷是 RDL 互连的线间距较小——例如,与 CoWoS-S 的亚微米间距相比,有机上的间距为 4 微米。

3、CoWoS-L

在硅 –S 和有机 –R 中介层选项之间,TSMC CoWoS 系列包括一个更新的产品,具有用于相邻die边缘之间(超短距离)互连的“本地”硅桥。这些硅片嵌入有机基板中,提供高密度 USR 连接(具有紧密的 L/S 间距)以及有机基板上(厚)导线和平面的互连和功率分配功能。

请注意,CoWoS 被指定为“chip last”组装流程,芯片连接到制造的中介层。

再看2.5D封装技术InFO。

据介绍,InFO 在载体上使用(单个或多个)裸片,随后将这些裸片嵌入molding compound的重构晶圆中。随后在晶圆上制造 RDL 互连和介电层,这是“chip first”的工艺流程。单die InFO 提供了高凸点数选项,RDL 线从芯片区域向外延伸——即“扇出”拓扑。如下图所示,多die InFO 技术选项包括:

InFO-PoP:“package-on-package”InFO-oS:“InFO assembly-on-substrate”

台积电的3D封装技术则是SoIC。

据台积电介绍,公司的3D 封装与 SoIC 平台相关联,该平台使用堆叠芯片和直接焊盘键合,面对面或面对背方向 -表示为 SoIC 晶圆上芯片(chip on wafer)。硅通孔 (TSV) 通过 3D 堆栈中的die提供连接。

SoIC 开发路线图如下所示——例如,N7-on-N7 芯片配置将在 21 年第四季度获得认证。

台积电对先进封装的看法

据台积电介绍,晶圆级系统整合技术(WLSI)在日益复杂的应用领域中藉由混合与匹配不同平台而迅速发展。这些包含在晶圆级系统整合范围内的技术被命名为3DFabric,因为它能够实现精细间距的芯片到芯片连接,以及利用现有晶圆制程的统合制造理念。

在3DFabric下,先嵌入芯片再做导线互连的所有制程都称为整合型扇出(InFO)。而先做线路重布层(RDL),然后再将芯片嵌入预制的RDL上就称为CoWoS(Chip-on-Wafer-on-Substrate)。这个新的命名系统真实反映了制程的本质并指向将来的技术推进轨迹。与同级制程系统整合芯片(System on Integrated Chips, SoIC)、SoW(System on Wafer)和SoIS(System on Integrated Substrate)结合在一起,它们形成了通用的晶圆级系统整合技术家族,将推动产业界在面对更具挑战和多样化的运算系统整合需求下,满足未来的系统级微缩需求。

台积电进一步指出,系统整合芯片(TSMC-SoIC)是创新的晶圆级前段三维芯片(3DIC)堆栈平台,具有卓越的接合密度、互连频宽、功耗效率和薄形轮廓,可透过系统级微缩来延续摩尔定律,具有持续性的效能提升和成本优势。系统整合芯片接下来可以使用传统封装或台积公司新的3DFabric技术。

例如,CoWoS或整合型扇出来做封装,支援下一代高效能运算(HPC)、人工智能(AI)和行动应用产品。目前台积公司已使用微米级接合间距制程完成了芯片对晶圆(Chip on Wafer, CoW)和晶圆对晶圆(Wafer on Wafer, WoW)堆栈制程的验证,具有令人满意的电性良率和可靠性结果。

台积公司将继续追求系统整合芯片技术的微缩,以与台积公司先进的硅技术保持一致,进一步提高晶体管密度、系统功耗、性能和面积(Power, Performance, Area,PPA)与成本竞争力。

在台积电看来,智能产品应用的2.5D领先技术。此技术具有一个大型的硅中介层,该中介层具有次微米级的绕线层和整合电容(integrated capacitors, iCap),因此可以在其上面放置系统单芯片(SoC)和高频宽存储器(HBM)等各种小芯片。正在开发的第五代CoWoS具有创纪录的硅中介层面积,高达2,400平方毫米,相当于三个全光罩(full-reticle)尺寸。此技术预计于2021年上半年完成验证。

他们表示,2020年,台积公司持续领先全球大量生产第五代整合型扇出层叠封装技术(InFO-PoP Gen-5)以支援行动应用,并大量生产第二代整合型扇出暨基板封装技术(InFO-oS Gen-2)支援高效能运算晶粒分割的应用。

第六代InFO-PoP已成功通过认证支援行动应用和增强散热性能。如期开发完成的第三代InFO-oS提供了更多的芯片分割,整合于更大的封装尺寸和更高的频宽。为了满足HPC应用的需求,台积公司开发了超高频宽整合型扇出暨局部硅互连技术(InFO Local Silicon Interconnect, InFO_LSI),其中系统单芯片小芯片(Chiplet)藉由超高密度局部硅互连(LSI)整合到三维InFO封装中。无基板InFO使用多芯片异质整合与更细间距的芯片到芯片互连技术,已成功完成验证以满足消费性电子产品的应用。

最新一代整合式被动元件技术(Integrated Passive Device, IPD)提供高密度电容器和低有效串联电感(Effective Series Inductance, ESL)以增强电性,并已在InFO-PoP上通过认证。AI与5G行动应用将受惠于此增强的InFO-PoP技术。最新一代IPD预计于2021开始大量生产。

台积电先进封装的新进展

在台积电的最新技术研讨会上,公司发布了在封装方面的一些新进展。

1、最大封装尺寸和 RDL 增强

对集成到单个封装中的大量 2.5D 裸片的需求推动了对更大面积的 RDL 制造的需求,无论是在中介层还是重组晶圆上。台积电继续将互连的“拼接”扩展到超过单次曝光最大光罩尺寸。同样,需要额外的 RDL 层(具有激进的线距)。

更大封装尺寸和 RDL 层的路线图包括:

CoWoS-S:3X 标线(2021 年认证);

CoWoS-R:45X 掩模版(2022 年为 3X),有机基板上的 4 个 RDL 层(W/S:2um/2um),使用 SoC + 2 HBM2 die堆栈进行可靠性认证;

CoWoS-L:1.5X 掩模版尺寸的可靠性评估测试工具,在 1 个 SoC 和 4 个 HBM2 芯片堆栈之间有 4 个本地互连桥;

InFO_oS:5X 掩模版(51mm x 42mm,在 110mm x 110mm 封装上),5 个 RDL 层(W/S:2um/2um),目前在可靠性评估中;

下图说明了一种潜在的 InFO_oS 配置,其中逻辑芯片被 I/O SerDes 小芯片包围,以支持高速/高基数网络交换机。

2、InFO_B(底部)

上面显示的 InFO_PoP 配置描述了一个 InFO 组件,其顶部连接了一个 DRAM 模块,在 DRAM 和 RDL 互连层之间有过孔。

TSMC 正在更改此 InFO_PoP 产品,以使 (LPDDR DRAM) 封装组装能够在外部合同制造商/OSAT 上完成,InFO_B 表示一个选项,如下所示。

相应地,台积电将“开放创新平台”扩展到包括符合 InFO_B 总装条件的 3DFabric 合作伙伴。(目前,3DFabric 合作公司有:Amkor Technology、ASE Group、Integrated Service Technology、SK Hynix。)

3、CoWoS-S“标准架构”(STAR)

CoWoS-S 的流行设计实现是将单个 SoC 与多个高带宽存储器 (HBM) die堆栈集成。逻辑芯片和 HBM2E(第二代)堆栈之间的数据总线宽度非常大,即 1024 位。

通过 RDL 将 HBM堆栈连接到 SoC 的路由和信号完整性挑战是相当大的。TSMC 正在为系统公司提供多种标准 CoWoS-S 设计配置,以加快工程开发和电气分析进度。下图说明了一些不同的 CoWoS-S 选项,范围从 2 到 6 个 HBM2E 堆栈。

台积电预计 2021 年这些标准设计实施的采用率会很高。

4、新TIM材料

热界面材料 (hermal interface material:TIM) 薄膜通常包含在高级封装中,以帮助降低从有源die到周围环境的总热阻。(对于非常高功率的器件,通常应用两层 TIM 材料层——die和封装盖之间的内层以及封装和散热器之间的一层。)

对应于更大封装配置的功耗增加,台积电先进封装研发团队正在寻求新的内部 TIM 材料选项,如下所示。

5、先进封装(AP)制造能力扩张

预计 3DFabric 封装的完整补充将越来越多地采用,台积电正在大力投资扩大先进封装 (AP) 制造能力,如下图所示。

声明

来源:半导体行业观察

版权归原作者所有,若侵权请联系删除

编辑:jq

-

芯片

+关注

关注

460文章

52624浏览量

442788 -

台积电

+关注

关注

44文章

5760浏览量

170179 -

单芯片

+关注

关注

3文章

462浏览量

35384 -

晶圆代工

+关注

关注

6文章

868浏览量

49270 -

3D封装

+关注

关注

9文章

141浏览量

27880

原文标题:科技前沿 | 台积电的先进封装

文章出处:【微信号:siid_inno,微信公众号:深圳创新设计研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

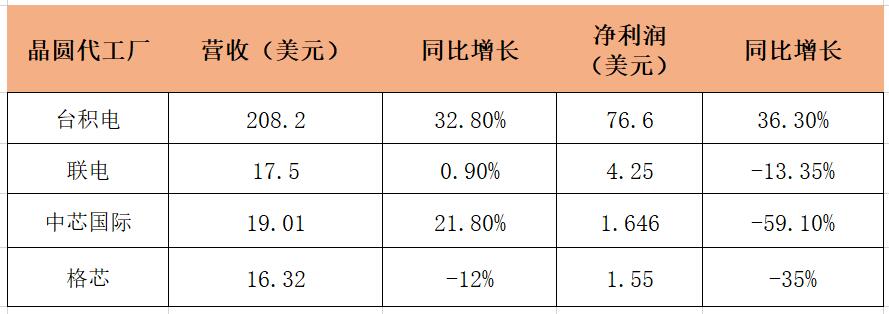

722.9亿美元!Q1全球半导体晶圆代工2.0市场收入增长13%

2024年晶圆代工市场年增长22%,台积电2025年持续维持领头羊地位

台积电扩大先进封装设施,南科等地将增建新厂

被台积电拒绝代工,三星芯片制造突围的关键在先进封装?

三星电子晶圆代工副总裁:三星技术不输于台积电

台积电引领全球晶圆代工热潮,明年产值料增逾二成

晶圆出货量增长!台积电Q2营收飙涨,四大芯片代工厂财报有何亮点?

深入介绍晶圆代工巨头台积电的先进封装

深入介绍晶圆代工巨头台积电的先进封装

评论