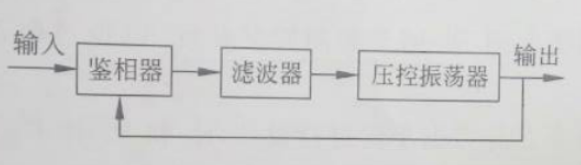

一、锁相环组成

锁相环一般由三部分组成压控振荡器、滤波器和鉴相器。最终使得输入和输出两个频率同步,且具有稳定的相位差。

二、锁相环作用

用来把输入的时钟频率进行倍频。

三、锁相环各个部分介绍

压控振荡器:电压变化控制输出的振荡器,输入电压越高,输出频率越大!

鉴相器:鉴定两个输入波形的相位,输出占空比稳定的波形。

滤波器:把鉴相器输出的或高或低的方波电压,经过滤波器变成平稳的直流电压。

四、如何具体实现输出信号的分频和倍频

如果想要倍频,只需要将压控振荡器的输出进行分频,比如二分频,其中一部分分频和输入频率得一样,那么对应输出的频率就是输入频率的二倍了。

编辑:jq

-

滤波器

+关注

关注

162文章

8154浏览量

182369 -

压控振荡器

+关注

关注

10文章

166浏览量

29776 -

鉴相器

+关注

关注

1文章

62浏览量

23629

原文标题:关于锁相环(PLL)必须要知道的事

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

锁相环(PLL)电路设计与应用(全9章)

锁相环是什么意思

可编程晶振的锁相环原理

锁相环PLL的噪声分析与优化 锁相环PLL与相位噪声的关系

锁相环PLL的常见故障及解决方案

锁相环PLL在无线电中的应用 锁相环PLL与模拟电路的结合

锁相环PLL与频率合成器的区别

锁相环PLL技术在通信中的应用

锁相环PLL的工作原理 锁相环PLL应用领域

将 Hercules 锁相环(PLL)咨询SSWFO21#45的影响降至最低

CDC509高性能、低偏斜、低抖动、锁相环(PLL)时钟驱动器数据表

简述锁相环的基本结构

关于锁相环(PLL)你知道哪些?

关于锁相环(PLL)你知道哪些?

评论