模块是Verilog 的基本描述单位,用于描述某个设计的功能或结构及其与其他模块通信的外部端口。一个设计的结构可使用开关级原语、门级原语和用户定义的原语方式描述; 设计的数据流行为使用连续赋值语句进行描述; 时序行为使用过程结构描述。一个模块可以在另一个模块中使用。

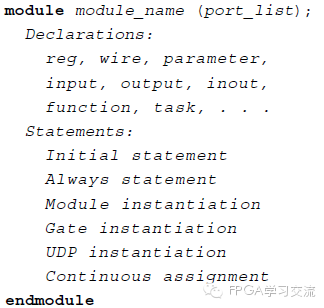

一个模块的基本语法如下:

说明部分用于定义不同的项,例如模块描述中使用的寄存器和参数。语句定义设计的功能和结构。说明部分和语句可以散布在模块中的任何地方;但是变量、寄存器、线网和参数等的说明部分必须在使用前出现。为了使模块描述清晰和具有良好的可读性, 最好将所有的说明部分放在语句前。本书中的所有实例都遵守这一规范。

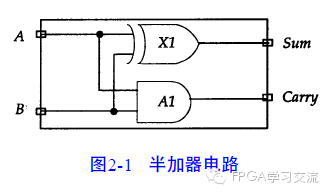

图2 - 1为建模一个半加器电路的模块的简单实例。

模块的名字是H a l f A d d e r。模块有4个端口: 两个输入端口A和B,两个输出端口S u m和C a rry。由于没有定义端口的位数, 所有端口大小都为1位;同时, 由于没有各端口的数据类型说明, 这四个端口都是线网数据类型。模块包含两条描述半加器数据流行为的连续赋值语句。从这种意义上讲,这些语句在模块中出现的顺序无关紧要,这些语句是并发的。每条语句的执行顺序依赖于发生在变量A和B上的事件。

在模块中,可用下述方式描述一个设计:

1) 数据流方式;

2) 行为方式;

3) 结构方式;

4) 上述描述方式的混合。

原文标题:Verilog HDL硬件描述语言-模块

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

模块

+关注

关注

7文章

2799浏览量

51055 -

HDL

+关注

关注

8文章

330浏览量

48248

原文标题:Verilog HDL硬件描述语言-模块

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文详解Verilog HDL

千兆网络PHY芯片RTL8211E的实践应用

Verilog HDL硬件基本描述单位模块

Verilog HDL硬件基本描述单位模块

评论