SPI是单片机外设电路中常用的一种通讯方式,适用于近距离通信,通常用于芯片间的通讯,有四根线。在SPI通讯中总线时钟和总线相位也两个比较重要的概念,一般在使用SPI通信时都使用默认设置,所以容易把这两个参数忽略。和大家分享一下SPI通讯、时钟极性以及时钟相位的基础知识。 什么是SPI通讯总线 SPI总线的英文全称为S“Serial Periphral Interface”,意思是串行外设接口,由于通讯距离比较短,适用于芯片级别的短距离通讯。SPI的通讯分为主机和从机,属于高速全双工的总线通讯方式,SPI有四根线,分别为:

MISO:主设备输入与从设备输出线;

MOSI:主设备输出与从设备输入线;

SCK:串行同步时钟信号线;

SS:从机片选信号线,也用CS来表示。

SPI总线的主机和从机的系统连接图如下图所示。

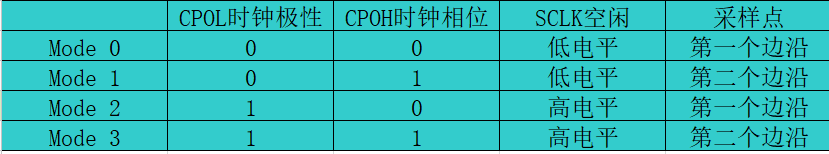

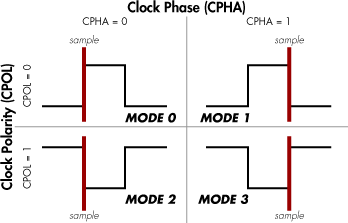

SPI总线时钟的极性含义解释 SPI的时钟极性用CPOL来表示。SPI总线通讯的时基基准是时钟信号线SCK,SCK既有高电平,又有低电平,SPI的时钟极性用来表示时钟信号在空闲时是高电平还是低电平。情况说明如下:

当CPOL=0:SCK信号线在空闲时为低电平;

当CPOL=1:SCK信号线在空闲时为高电平;

SPI总线时钟的相位含义解释

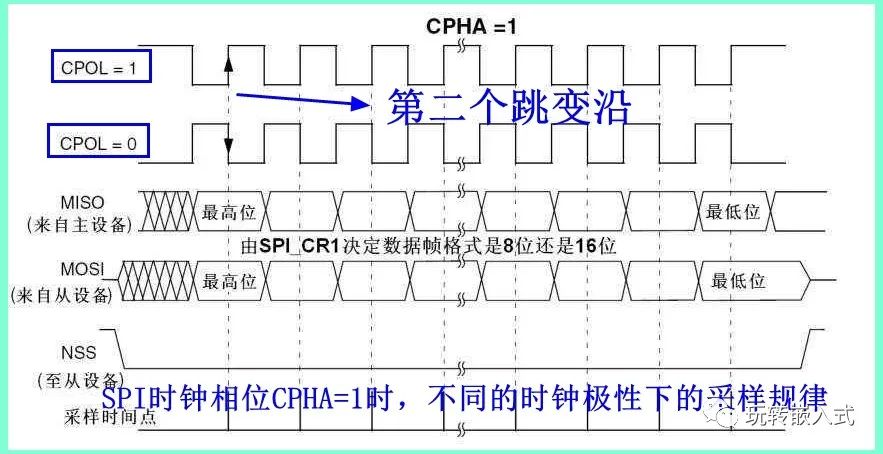

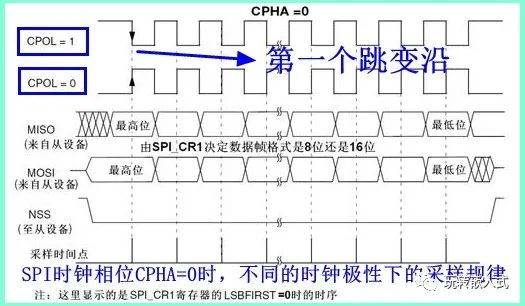

时钟的相位用CPHA来表示,用来决定何时进行信号采样,在第一个跳变沿还是第二个跳变沿,至于是上升沿还是下降沿则由CPOL相位极性来表示。下面分两种情况来介绍。如下图所示。

上图表示CPHA=1时的情形,即在SCK时钟的第二个边沿进行数据的采样,至于是上升沿采样还是下降沿采样取决于时钟极性CPOL的值。如果CPHA=1,CPOL=1,则在SCK时钟的第二个边沿为上升沿时进行数据采样。如果CPHA=1,CPOL=0,则在SCK时钟的第二个边沿为下降沿时进行数据采样。 CPHA=0时的情形如下图所示。

上图表示CPHA=0时的情形,即在SCK时钟的第一个边沿进行数据的采样,至于是上升沿采样还是下降沿采样取决于时钟极性CPOL的值。如果CPHA=0,CPOL=1,则在SCK时钟的第一个边沿为下降沿时进行数据采样。如果CPHA=0,CPOL=0,则在SCK时钟的第一个边沿为上升沿时进行数据采样。 总结一下,SPI的时钟极性决定了SCK在空闲时是低电平还是高电平;而相位极性则决定了在第一个边沿还是第二个边沿进行数据采样。SPI的时钟极性CPOL和相位极性CPHA是相互影响相互决定的,以上概念可能很绕口难以理解,但是对SPI进行一次编程之后,所有的内容都好理解了。

责任编辑:xj

原文标题:SPI编程时,时钟相位(CPHA)和时钟极性(CPOL)怎么理解?

-

时钟

+关注

关注

11文章

1903浏览量

133363 -

SPI

+关注

关注

17文章

1806浏览量

96323 -

编程

+关注

关注

88文章

3689浏览量

95388

原文标题:SPI编程时,时钟相位(CPHA)和时钟极性(CPOL)怎么理解?

文章出处:【微信号:gh_c472c2199c88,微信公众号:嵌入式微处理器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

当波特率设置为高时,SPI 时钟延长,数据丢失问题怎么解决?

FPGA时序约束之设置时钟组

AD9547双路/四路输入网络时钟发生器/同步器技术手册

AD9559双路PLL四通道输入多服务线路卡自适应时钟转换器技术手册

AD9554四路PLL、四通道输入、八通道输出多服务线路卡自适应时钟转换器技术手册

白话理解RCC时钟树(可下载)

通信协议之SPI总线硬件篇

请问LMK05318BEVM如何实现输入和输出时钟的相位同步?

飞凌嵌入式ElfBoard ELF 1板卡-spi编程示例之spi硬件原理

时钟产品参数解读

SPI编程时,如何理解时钟相位和时钟极性

SPI编程时,如何理解时钟相位和时钟极性

评论