Andes公司推出了Linux友好型A25 CPU内核的新A25MP和AX25MP版本,这些内核被称为是首个带有“综合” DSP的RISC-V内核。1GHz以上的内核提供了缓存一致性,并支持SMP和多达四核设计。

在台湾RISC-V研讨会上,Andes技术公司宣布了其Linux友好型,兼容RISC-V ISA的第二代A25(32位)和AX25(64位)CPU内核。Andes说,32位,28nm的A25MP和64位AX25MP是首批具有全面DSP指令扩展功能的商业RISC-V内核。与早期的A25代(请参阅下文)不同,它们也是第一个提供缓存一致性以支持多核和多处理器支持的产品。但是,最初的产品将是单核设计。

A25MP / AX25MP DSP(数字信号处理器)ISA基于Andes捐赠给RISC-V基金会的RISC-V P扩展草案(PDF)。台湾的Andes公司说,DSP在加速语音,音频和图像处理方面特别有用。该公司还指出了“增强人工智能和高级驾驶员辅助系统(ADAS)等应用程序的功能”。

与该公司的编译器,DSP库和模拟器一起使用时,A25MP / AX25MP DSP“在PNET中为MtCNN(多任务级联卷积网络)人脸检测和对齐算法提供了超过7倍的加速,” Andes说。DSP还据称在CIFAR10图像分类基准上提供了“数量级性能提升”,用于训练机器学习和计算机视觉算法。

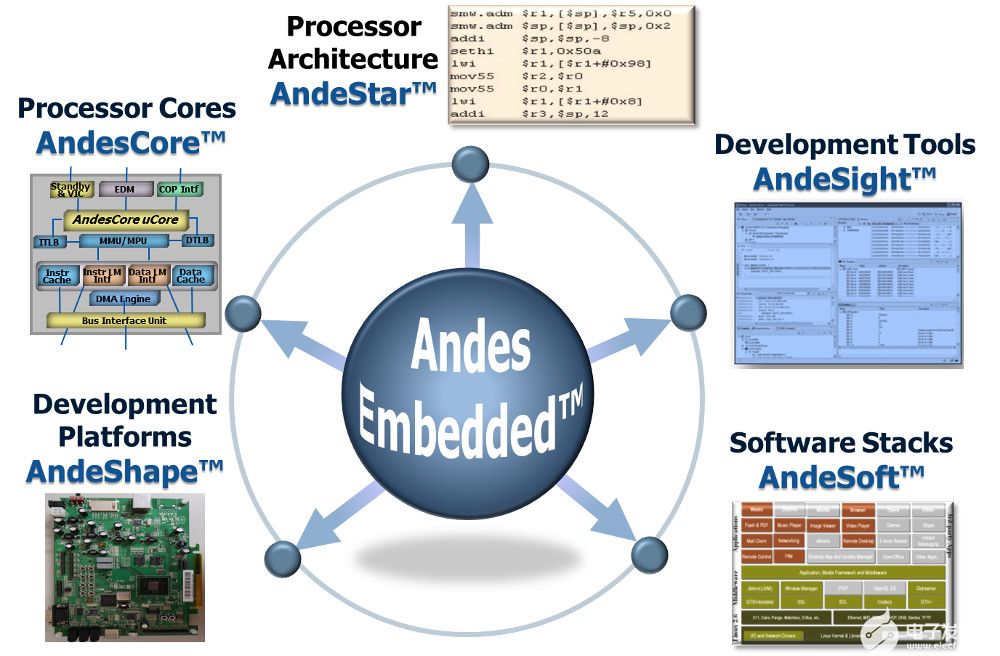

适用于Linux的A25 / AX25芯片的安第斯山脉CPU IP生态系统

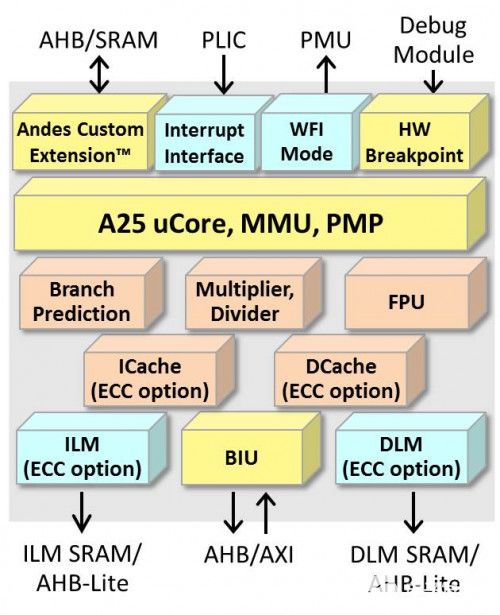

体系结构图构成了新A25MP和AX25MP的基础

SoC设计人员可以使用DSP ISA升级其现有的,具有Linux功能的A25和AX25芯片,Andes说。此外,安第斯山脉宣布了不具备Linux功能的32位D25F处理器,“这是不带MMU和S模式支持的A25”,它还提供了DSP ISA。该公司表示,所有安第斯山脉的新处理器IP都“享受25系列处理器相同的有效基准管线以及用于定制指令设计的强大ACE工具”。

Andes公司早期的A25和AX25

在2018年10月,提供广泛的类似于MCU的RISC处理器的安第斯山脉(Andes)宣布了其首个具有开源RISC-V ISA的内核。其中包括其微小的,非Linux兼容的N22和N25系列内核以及其首个Linux就绪的RISC-V IP:32位A25和64位AX25。

新的启用了DSP和多核的A25MP和AX25MP尚无文档,但它们可能会提供类似的单核非DSP A25和AX25上的所有功能。与Andes的基于RISC-V的N22和N25系列内核以及早期的非RISC-V部件一样,A25系列也是AndesCore系列的一部分,该系列“采用RISC-V作为第五代产品的子集” AndeStar V5体系结构。

A25和AX25看起来几乎完全相同,只是它们的32位和64位体系结构不同。Andes说,64位AX25支持需要访问地址空间超过4GB的高性能嵌入式应用程序。我们在比较规格表时看到的唯一区别是64位AX25在0.174平方毫米处相对于0.147平方毫米更大,而在22uW / MHz处则比17吸收更大的动态功率。

A25和AX25采用与新的多核DSP型号相同的台积电28nm HPC +工艺制造,具有5级流水线并支持高达1.2GHz,3.5 CoreMark / MHz的性能。该处理器设计支持单精度和双精度浮点指令,半精度加载/存储,以及针对基于Linux的应用程序的MMU和Supervisor模式(S模式)。

A25和AX25提供分支预测,指令和数据缓存,用于低延迟访问的本地存储器以及对L1存储器软错误保护的ECC支持。其他功能包括PLIC和向量中断,AXI 64位或AHB 64/32位总线,以及用于低功耗和电源管理的PowerBrake和WFI模式。

开发工具包括AndeSight IDE,用于ACE的“ COPILOT”工具以及JTAG和ICE调试。Andes为某些AndesCore IP提供了AndesShape硬件开发平台,但到目前为止,这些都不支持A25系列。

SoC设计人员似乎可以使用A25和AX25 IP,但是目前尚不清楚是否有任何基于A25的SoC交付。今年1月,该公司宣布,2018年内核已交付10亿片SoC,累计总计35亿片。但是,大多数(如果不是全部)都不使用RISC-V。

其他Tuxified RISC-V芯片

A25内核家族加入了少量已发布的Linux就绪RISC-V内核,这些内核主要来自SiFive。该公司已将其内核扩展为对Linux友好的Freedom U540 SoC,并宣布了下一代U74和U74-MC设计。

Microchip的Microsemi部门宣布了部分基于SiFive的U54-MC内核的Linux友好型PolarFire SoC。它被称为世界上第一个RISC-V FPGA SOC。Shakti芯片是另一款受Linux支持的RISC-V芯片,该芯片部分由印度政府资助。

Andes Technology没有为新的A25MP和AX25MP RISC-V内核提供可用性信息。

-

dsp

+关注

关注

557文章

8166浏览量

359169 -

cpu

+关注

关注

68文章

11113浏览量

218208 -

Linux

+关注

关注

88文章

11534浏览量

214810 -

ADS1255

+关注

关注

0文章

16浏览量

12053 -

DSP芯片

+关注

关注

9文章

154浏览量

30863 -

数字信号处理器

+关注

关注

5文章

484浏览量

27945

发布评论请先 登录

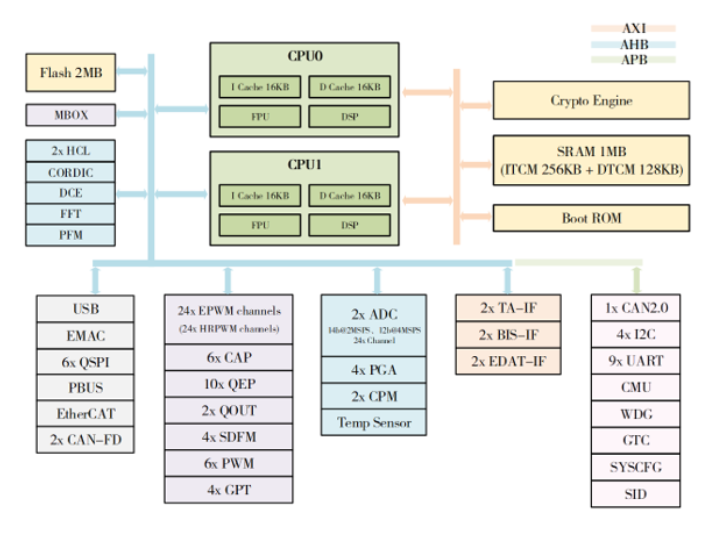

HXS320F28027数字信号处理器(32位RISC-V DSP)

DietPi 9.10:带来 RISC-V 升级与树莓派内核迁移

SOPHGO RISC-V SoC Linux Kernel 社区邮件列表建立,欢迎加入开源社区为RISC-V生态完善添砖加瓦

Imagination放弃RISC-V处理器内核开发

基于risc-v架构的芯片与linux系统兼容性讨论

《RISC-V能否复制Linux 的成功?》

RISC-V发展及FPGA厂商为什么选择RISC-V

来真的?Milk-V 即将推出的 RISC-V 设备已经能使用 AMD 卡皇 7900XTX 显卡了?!

国产RISC-V案例分享,基于全志T113-i异构多核平台!

RISC-V内核是如何与FPGA内核进行资源共享的?

RISC-V内核的32位通用微控制器 GD32VF103芯片简介

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

首个带有“综合”DSP的RISC-V内核支持Linux

首个带有“综合”DSP的RISC-V内核支持Linux

评论