01

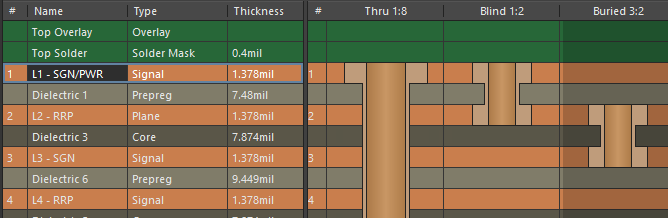

射频板叠层结构

RF PCB单板的叠层结构除了要考虑射频信号线的阻抗以外,还需要考虑散热、电流、器件、EMC、结构和趋肤效应等问题,通常我们在多层印制板分层及堆叠中遵徇以下一些基本原则: A) RF PCB的每层都大面积铺地,没有电源平面,RF布线层的上下相邻两层都应该是地平面。 即使是数模混合板,数字部分可以存在电源平面,但是 RF 区仍然要满足每层都大面积铺地的要求。

B) 对RF双面板来说,顶层为信号层,底层为地平面。 四层RF单板,顶层为信号层,第二层和第四层为地平面,第三层走电源、控制线。特殊情况在第三层可以走一些RF 信号线。更多层的RF单板,以此类推。 C) 对于RF背板来说,上下两表面层都是地面,为了减小过孔及连接器的引起的阻抗不连续性,第二、三、四、五层走数字信号。 而其它靠底面的带状线层都是 底面 信号层。同样,RF 信号层上下相邻两层该是地面,每层都应该大面积铺地。

D) 对于大功率、大电流的射频板应该将RF 主链路放置到顶层并且用较宽的微带线连接。 这样有利于散热和减小能量损耗,减少导线腐蚀误差。

E) 数字部分的电源平面应靠近接地平面,并且安排在接地平面之下。 这样可以利用两金属平板间的电容作电源的平滑电容,同时接地平面还对电源平面上分布的辐射电流起到屏蔽作用。 具体叠层方法和平面分割要求可以参照EDA 设计部颁布的《20050818 印刷电路板设计规范——EMC 要求》,以网上标准为准。

02

射频板布线要求

2.1 转角

射频信号走线如果走直角,拐角处的有效线宽会增大,阻抗不连续而引起反射。故要对转角进行处理,主要为切角和圆角两种方法。 (1) 切角适用于比较小的弯角,切角的适用频率可达10GHz。

(2) 圆弧角的半径应足够大,一般来说,要保证:R>3W。

2.2 微带线布线

PCB顶层走射频信号,射频信号下面的平面层必须是完整的接地平面,形成微带线结构。要保证微带线的结构完整性,有以下要求: (1) 微带线两边的边缘离下方地平面边缘至少要有3W 宽度。且在3W 范围内,不得有非接地的过孔。

(2) 微带线至屏蔽壁距离应保持为2W 以上。(注:W 为线宽)。

(3) 同层内非耦合微带线要做包地铜皮处理并在地铜皮上加地过孔,孔间距小于λ/20,均匀排列整齐。 地铜箔边缘要光滑、平整、禁止尖锐毛刺。建议包地铜皮边缘离微带线边缘大于等于1.5W的宽度或者3H的宽度,H 表示微带衬底介质的厚度。

(4) 禁止 RF 信号走线跨第二层的地平面缝隙。

2.3 带状线布线

射频信号有时要从PCB的中间层穿过,常见的为从第三层走,第二层和第四层必须是完整的接地平面,即偏心带状线结构。应保证带状线的结构完整性须要求:

(1) 带状线两边的边缘离上下地平面边缘至少3W宽度,且在3W范围内,不得有非接地的过孔。

(2) 禁止RF带状线跨上下层的地平面缝隙。

(3) 同层内带状线要做包地铜皮处理并在地铜皮上加地过孔,孔间距小于λ/20,均匀排列整齐。地铜箔边缘要光滑、平整、禁止尖锐毛刺。 建议包地铜皮边缘离带状线边缘大于等于1.5W的宽度或者3H的宽度,H 表示带状线上下介质层总厚度。

(4) 如果带状线要传输大功率信号,为了避免50欧姆线宽过细,通常要将带状线区域的上下两个参考平面的铜皮做挖空处理,挖空宽度为带状线的总介质厚度的5倍以上,如果线宽仍然达不到要求,则再将上下相邻的第二层参考面挖空。

-

连接器

+关注

关注

99文章

15537浏览量

141624 -

布线

+关注

关注

9文章

802浏览量

85311 -

射频板

+关注

关注

0文章

5浏览量

6778

原文标题:细数射频板叠层结构以及布线要求

文章出处:【微信号:gh_454737165c13,微信公众号:Torex产品资讯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB叠层设计避坑指南

PCB叠层设计避坑指南

基于叠层组装和双腔体结构的高密度集成技术

迈向40%效率:新兴四端钙钛矿叠层电池从结构优化到性能提升的技术探索

四端钙钛矿叠层效率突破30.3%,从PVK/Si到全钙钛矿四种主流结构及性能分析

高层数层叠结构PCB的布线策略

效率超30%!双面钙钛矿/晶硅叠层电池的IBC光栅设计与性能优化

揭秘射频PCB设计要求及激光焊锡的应用

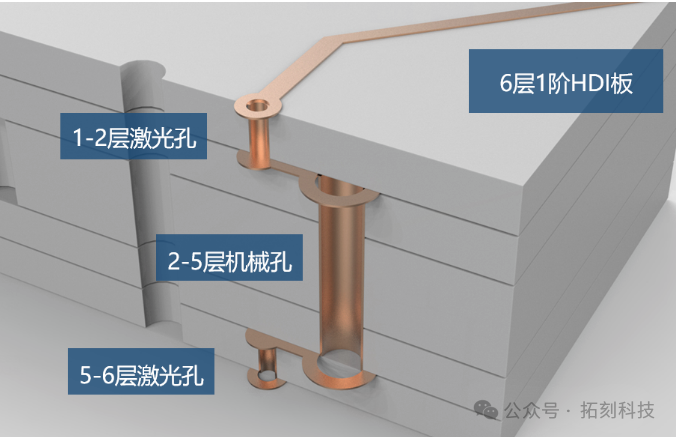

HDI的叠层结构设计

射频板叠层结构及布线要求

射频板叠层结构及布线要求

评论