时序分析在示波器上的实现,可以省去繁琐的人工分析步骤,大大节省工程师反复测试总线时序所花费的时间,无论是产品研发,还是产线测试,相信ZDS4000系列示波器都能为您带来全新的测试体验。

如何获取最新的时序分析功能

支持时序分析的ZDS示波器有ZDS4054 Plus、ZDS4034 Plus、ZDS4024 Plus,目前免费标配了I?C、I?S、SPI、MIPI-RFFE、CAN、Reset、Switch七种协议时序分析。自动分析多个波形中最差情况是否满足标准,可直接筛选某个特定节点并直接生成附带截图的报告。用户可在ZLG致远电子官网示波器资料下载页下载固件进行更新。

测试项目

下方展示I?C、I?S、SPI、MIPI-RFFE、CAN、Reset、Switch具体的测试项,可下拉滑动表格查看。

下拉查看长图

测试界面

时序分析软件测试界面如下图所示,可直接观测波形情况与具体的测试结果。

测量统计

如测试需要长时间进行,并对测试结果进行统计或针对测试结果进行特定操作,可使用测量统计功能。

1、停止条件

停止条件即示波器停止“统计分析”的条件,当测试条件满足预设条件时,时序分析软件会停止统计完成分析工作。

2、失败操作

失败操作即若波形进行测试过程中无法通过测试(Fail)时,将执行的操作。可操作的事件如图所示。

操作事件包括:

声音提示:即当出现测试不通过项时,系统会发出警报声(蜂鸣器)提醒;

导出报表:即当出现测试不通过项时,系统会自动导出当前数据并形成报告。

两项可以同时选择,若一项都不选择,则若出现失败项不做任何提醒。

3、历史统计

当设置好停止条件,失败操作后,点击【历史统计】(运行/停止统计)可对测量结果进行统计,此时将【信息显示】打开,可以看到统计的结果。

结果导出

测试完成后可对所测试的波形和数据进行导出。导出的“网页报表”文件可使用网页打开,导出的“CSV”文件可使用 Excel 打开。

导出结果如图所示:

-

示波器

+关注

关注

113文章

6733浏览量

189791 -

时序分析

+关注

关注

2文章

127浏览量

23968

原文标题:【ZDS示波器高级分析功能】时序分析

文章出处:【微信号:ZLG_zhiyuan,微信公众号:ZLG致远电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

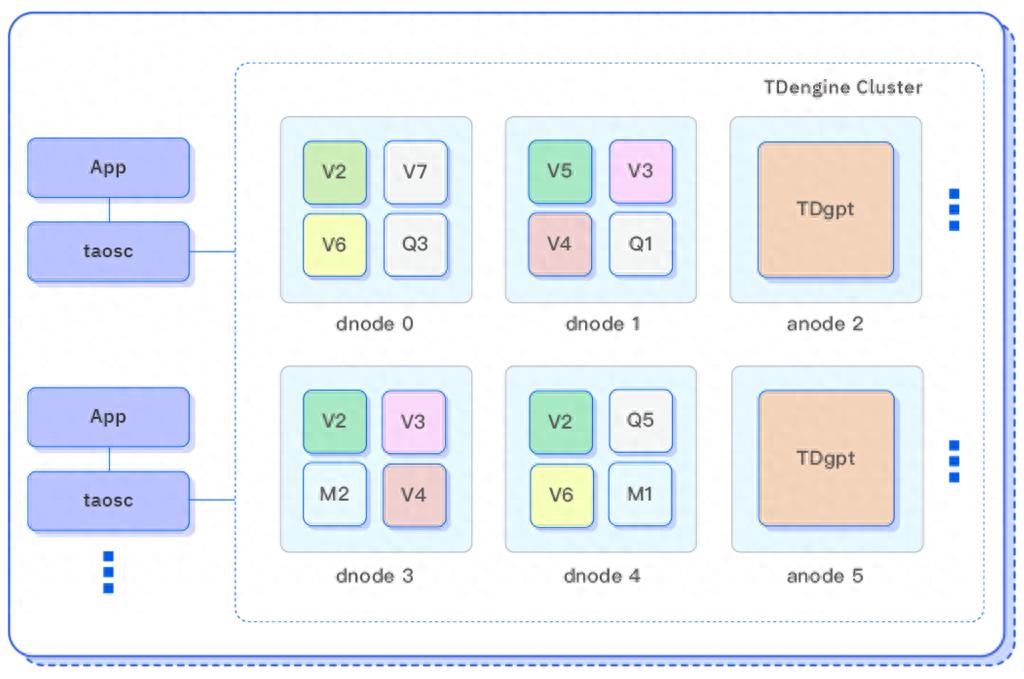

TDengine 发布时序数据分析 AI 智能体 TDgpt,核心代码开源

如何获取最新的时序分析功能

如何获取最新的时序分析功能

评论