全加器逻辑表达式

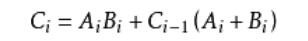

一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

第二个表达式也可来用一个异或门来代替或门对其中两个输入信号进行求和:

其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci。一位全加器可以处理低位进位,并输出本位加自法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

全加器的逻辑功能

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数![]() 和

和![]() ,还有一个来自前面低位送来的进位数

,还有一个来自前面低位送来的进位数![]() .这三个数相加,得出本位和数(全加和数)

.这三个数相加,得出本位和数(全加和数)![]() 和进位数

和进位数![]() .这种就是“全加“,下表为全加器的逻辑状态表。

.这种就是“全加“,下表为全加器的逻辑状态表。

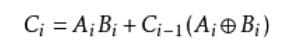

全加器可用两个半加器和一个“或“门组成。

如上图(a)所示。![]() 和

和![]() 在第一个半加器中相加,得出的结果再和

在第一个半加器中相加,得出的结果再和![]() 在第二个半加器中相加,即得出全加和

在第二个半加器中相加,即得出全加和![]() 。两个半加器的进位数通过”或“门输出作为本位的进位数

。两个半加器的进位数通过”或“门输出作为本位的进位数![]() 。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

-

全加器

+关注

关注

10文章

62浏览量

28854

发布评论请先 登录

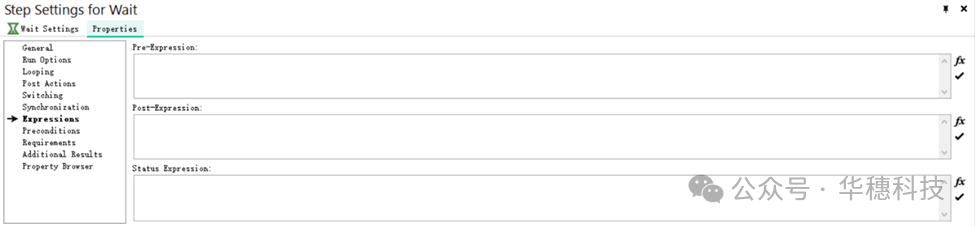

labview如何使用VISA串口资源查找的正则表达式提取串口的资源名称?

干货分享 | 零基础上手!TSMaster图形信号表达式实操指南

Verilog表达式的位宽确定规则

半加器和全加器的区别是什么

半加器和全加器的功能特点

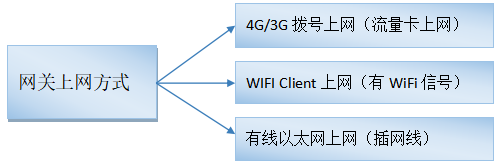

通过工业智能网关实现中间变量表达式的快速配置

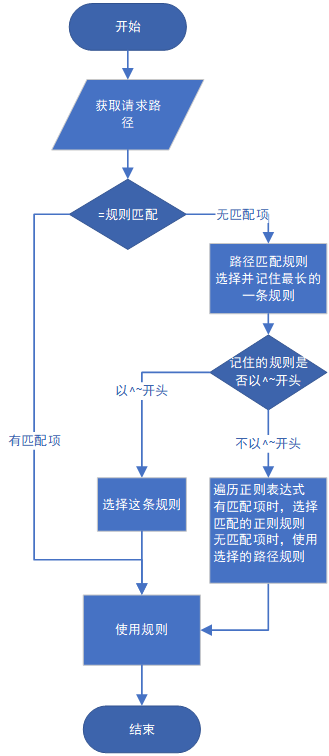

数字逻辑怎么把逻辑图画成电路图

TestStand表达式中常用的语法规则和运算符使用

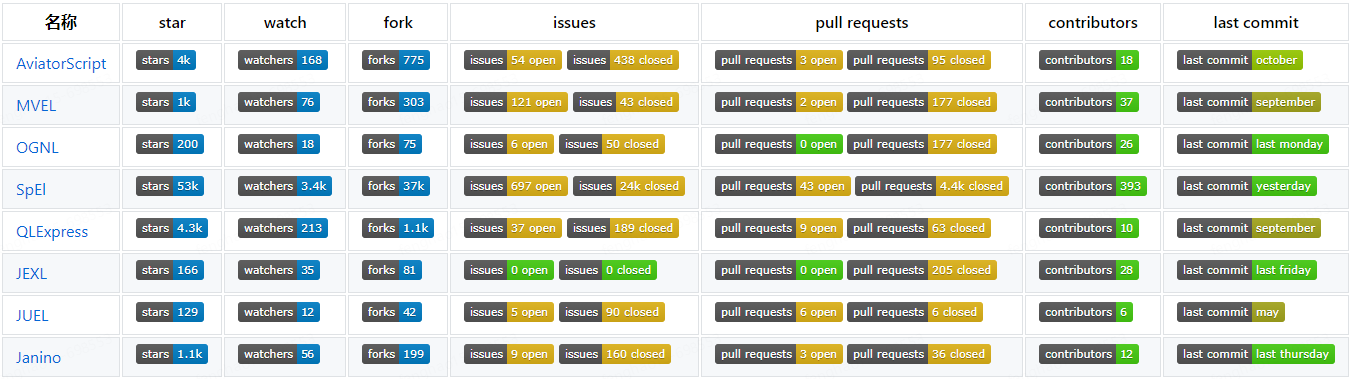

Java表达式引擎选型调研分析

全加器逻辑表达式_全加器的逻辑功能

全加器逻辑表达式_全加器的逻辑功能

评论