缓冲集成项目是快速,简单和自动创建差分对。在不到30秒的时间内,观察板可以创建50对!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

缓冲

+关注

关注

0文章

53浏览量

18044 -

自动

+关注

关注

0文章

121浏览量

26375

发布评论请先 登录

相关推荐

热点推荐

是否可以仅使用 Bootloader Host 来实现可引导加载项目的相同编程结果?

你好

我想使用 Bootloader Host 在我的 CY8CKIT-059 上对 CY8C5888LTI-LP097 芯片进行编程,并将项目类型设置为可引导加载。我的目标是实现与通过使用 SWD

发表于 07-18 07:39

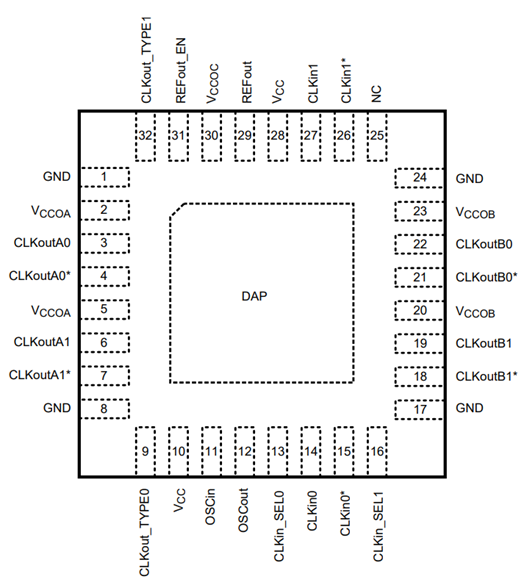

HAC00304QN型低抖动差分时钟缓冲器发布

输出,两个差分输出组可配置为 LVPECL、LVDS或HCSL驱动器,也可被禁用。LVCMOS 输出具有用于在启用或禁用时实现无短脉冲运行的同步使能输入。如果未选择晶体输入,内部振荡器电路会自动禁用

降压式电路的缓冲电路原理和快速设计

摘要

本应用报告首先给出了降压式开关电路(buck)在上管开通瞬间的的一个等效谐振回路模型。根据该模型推导出使得开关振铃最小化的阻容缓冲电路(snubber)的参数计算公式,并结合参数公式给出

发表于 06-05 14:27

Allegro Skill布线功能-添加差分过孔禁布区

在高速PCB设计中,差分过孔之间设置禁止布线区域具有重要意义。首先它能有效减少其他信号线对差分信号的串扰,保持差分对的信号完整性。其次禁止布线区域有助于维持

发表于 05-28 15:19

?384次阅读

LTC6416 2GHz、低噪声、差分16位ADC缓冲器技术手册

LTC6416 是一款差分单位增益缓冲器,专为以极低的输出噪声和卓越的线性 (在超过300MHz 的频率条件下) 来驱动 16 位 ADC 而设计。差分输入阻抗为 12kΩ,因而允许在输入端上使用 1:4 和 1:8 变压器,旨

EE-23:AD1847/ADSP-2181环回示例,使用单个索引寄存器实现SPORT自动缓冲

电子发烧友网站提供《EE-23:AD1847/ADSP-2181环回示例,使用单个索引寄存器实现SPORT自动缓冲.pdf》资料免费下载

发表于 01-14 15:05

?0次下载

可与MES系统集成的数据采集监控平台

可与MES系统集成的数据采集监控平台,在制造业中扮演着至关重要的角色。这类平台通过实时采集各类数据源,对数据进行整合和统一管理,为MES系统提供准确、实时的数据支持,从而帮助企业实现生产过程的数字化

发表于 12-16 15:08

自动化创建UI并解析数据

*附件:32960_auto.rar备注:Main.vi是ui自动化2.1.vi,配置文件为32960.B.ini。

目前可以实现根据配置文件自动化创建控件并布局,且可以

发表于 12-10 08:41

自动化创建UI并解析数据

Labview实现动态增加控件效果 - *附件:32960_auto.rar

备注:Main.vi是ui自动化2.1.vi,配置文件为32960.B.ini。

目前可以实现根据配置文件自动

发表于 11-29 11:26

前端的audio codec输出信号为R/L/GND, 如何变成差分对信号输入TPA3113D2?

请教前端的audio codec输出信号为R/L/GND, 如何变成差分对信号输入TPA3113D2? 是否要另选AMP方案? 输入脚RINN及LINN可以直接串隔直电容连接地平面吗? 谢谢~

发表于 11-06 08:05

缓冲集成项目可实现快速自动创建差分对

缓冲集成项目可实现快速自动创建差分对

评论