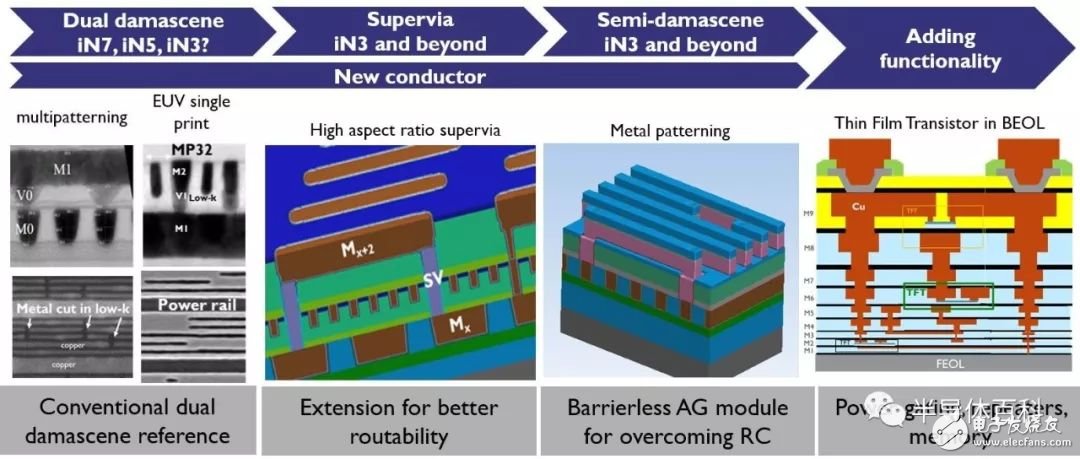

将互连扩展到3nm技术节点及以下需要多项创新。IMEC认为双大马士革中的单次显影EUV,Supervia结构,半大马士革工艺以及后段(BEOL)中的附加功能是未来的方向。IMEC纳米互连项目总监Zsolt Tokei阐述了这些创新 ,这些创新已在ITF USA和最新的IITC会议上公布。

当今的互连技术

金属互连 ,芯片后段(BEOL)中的微小布线,用于分配时钟和其他信号,为各种电子系统组件提供电源和接地,并连接芯片前段(FEOL)的晶体管。互连线由不同的金属层组成:本地(local Mx),中间层(intermediate),半全局(semi-global)和全局(global)线。总层数可以多达15个,而Mx层的典型数量范围在3到6之间。这些层中的每一个都包含(单向)金属线(或轨道)和介电材料。它们通过填充金属的通孔结构垂直互连。由于在在90年代中期引入双大马士革铜制程和低k电介质(例如SiO2,SiCO(H)和气隙,因此铜在逻辑和存储器芯片应用中一直是金属线和通孔的主力金属。

传统的CMOS技术节点缩放,导致互连金属线节距减小。虽然FinFET晶体管的尺寸缩放预计会减慢,但后段金属节距仍然会保持以0.7倍左右的速度缩放,以跟上所需的面积缩放。目前正在生产的最先进的互连技术(即10nm和7nm技术节点)其local M1层,金属节距缩小至36nm,以适应前段的缩放。同时,为了保持后段的性能,业界已经开始采用钴(Co)和气隙(Air gap)来制作金属互连。

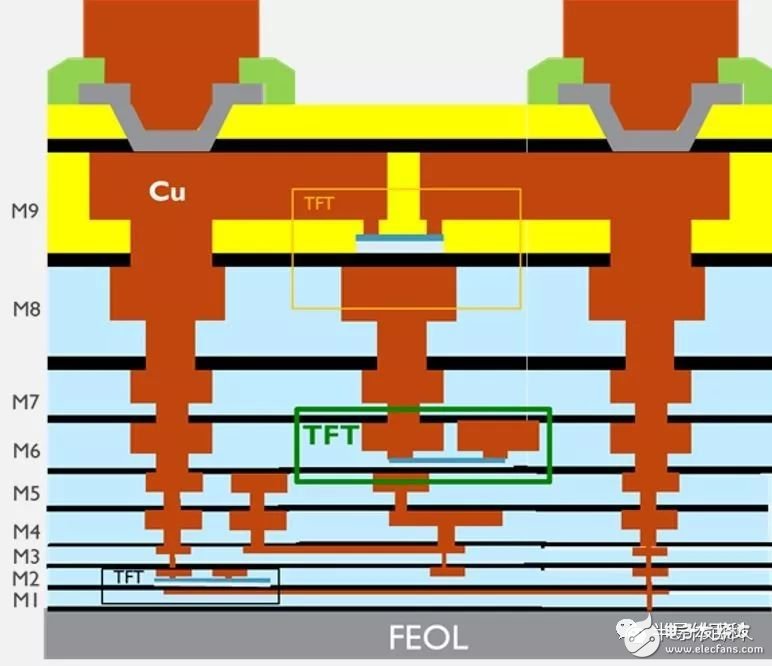

在中间互连层中集成薄膜晶体管(TFT)被认为是为BEOL增加额外功能的另一个机会。在该中间互连层中,通孔密度相对较低,这为诸如TFT等小晶体管提供了空间。这里,它们可用于各种应用,例如电源管理。BEOL中首批采用TFT的技术主要限于物联网应用。

迈向3nm互连

低于5nm技术节点的器件尺寸缩小正变得越来越具有挑战性。这主要是由于前段的电性和工艺漂移限制,以及后段线路中显着的RC延迟和线路拥塞。RC延迟是由金属线的横截面积减小引起的,其导致互连系统的RC变高。这最终导致信号延迟和功耗的大幅增加。这些问题在几个节点之前就开始了,每一代技术都在变得越来越糟。

为了继续超越5nm技术节点的互连扩展,IMEC正在探索各种新的工艺创新,微缩助推器和材料。特别是,用于未来互连的工艺“工具箱”包括在双大马士革工艺中引入单次极紫外(EUV)光刻,与气隙结合的半大马士革工艺,以及诸如Supervia结构的微缩助推器以实现更好的可布线性。所有这些创新都需要新的导体材料,与传统的Cu或Co相比具有更好的品质因数。“工具箱”与BEOL中的TFT集成相结合,可实现各种附加功能。在接下来的部分中,将更详细地讨论这些新颖的互连结构。

用于将互连扩展到3nm及以下的“工具箱”

双大马士革工艺

在转向新的集成工艺之前,半导体行业将尽可能长时间地扩展当前的双大马士革工艺。将双大马士革工艺延伸到较小金属节距的关键是引入单次EUV光刻以图案化最密集的线(M1和M2)和通孔(V1),这降低了工艺复杂性。对于当前浸没式光刻的多重显影,单次显影EUV将实现成本效益且具有更短的工艺流程。这种方法的真正效益将在制作低至少30nm节距的金属线时体现出来。

在IITC2019展会上,IMEC展示了3nm 节点的双大马士革工艺TQV结果。M1层用单次显影EUV工艺制作。为了实现M2 的21nm节距,IMEC提出了一种混合光刻方案,使用193i SAQP来制作线和沟槽,以及单次显影EUV用于制作隔断和通孔。此次TQV实现了无阻挡层的钌(Ru)金属连线方案和介电常数k = 3.0的绝缘介质层。与前几代产品相比,RC获得了30%的改善,而且拥有相同的可靠性。

21nm间距双大马士革试验车的RC特性

目前,IMEC团队正在探索实现16nm金属节距的可行性。这就需要多重显影方案,由于工艺漂移和机械稳定性问题,16nm金属节距依然挑战重重。

半大马士革工艺

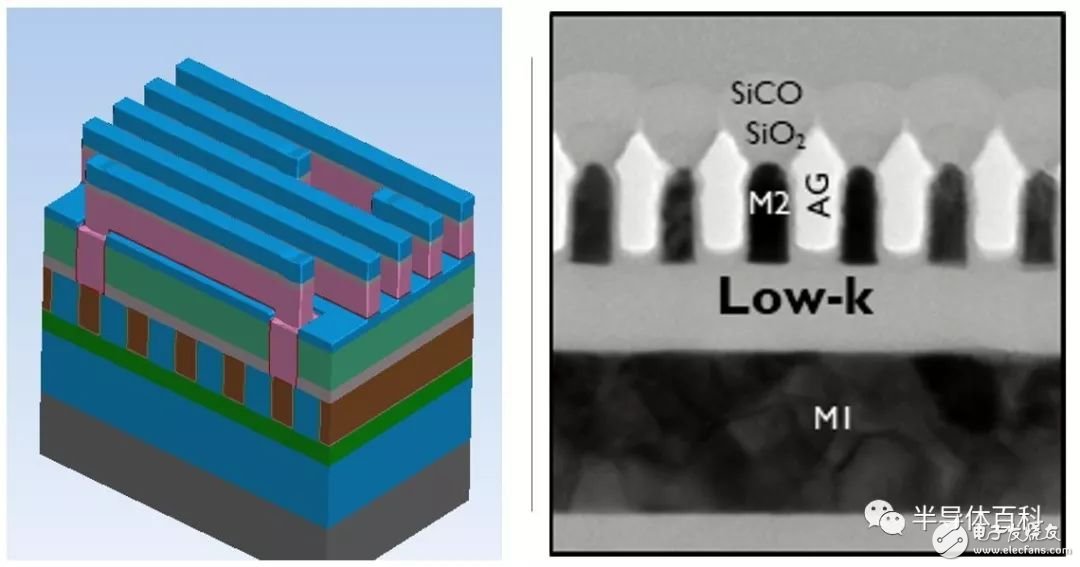

将基于大马士革工艺扩展到16nm金属节距的另一种有趣方法是引入半大马士革工艺。它可以与传统的双大马士革工艺结合使用。双大马士革和半大马士革之间的本质区别在于省略了金属的化学机械抛光(CMP)步骤。

半大马士革开始于通孔开口的光刻并蚀刻介电膜。然后用金属(例如Ru)填充通孔并过填充(意味着继续沉积金属),直到在电介质上形成金属层。然后掩蔽并蚀刻金属以形成金属线。

与传统大马士革工艺相比,半大马士革的真正优势在于能够降低工艺漂移并在金属线之间形成气隙(传统电介质的替代品)。当采用钌(Ru)作为导体时,在电介质和导体之间不需要扩散阻挡层。在传统双大马士革工艺中,在较高纵横比下的电容增加被视为改善互连RC的主要障碍。需要更高的深宽比来降低电阻和工艺漂移,但是它们的积极效果被不希望的电容增加所消除。使用无阻挡层的钌(Ru)金属线搭配气隙的半大马士革工艺可以解决这个问题。

早些时候,IMEC团队展示了其工艺可行性。最近它与EUV单次显影相结合,产生均匀的30nm金属节距线,如下图(右)。

半大马士革工艺:示意图和SEM切片

Supervia实现更好的可布线性

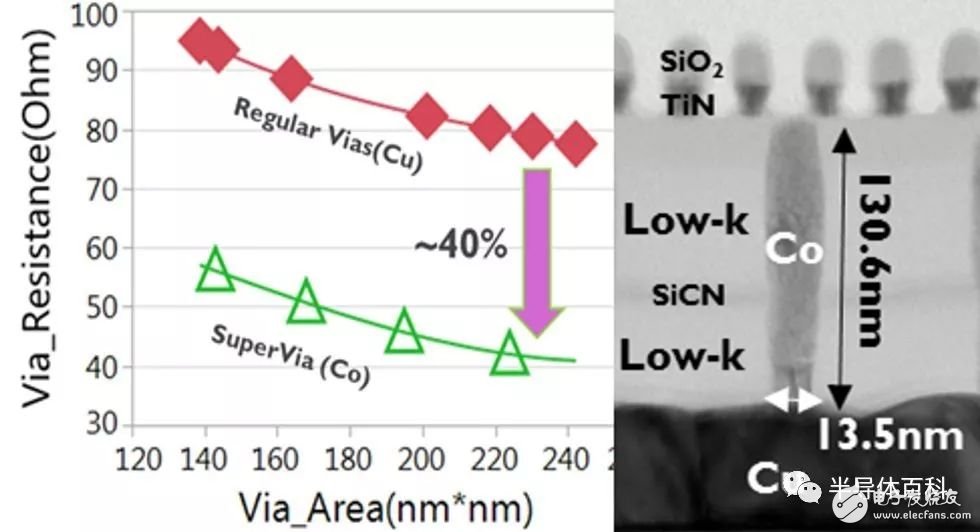

互连领域的下一个游戏规则改变者是Supervia结构,高深宽比的通孔,以最简单的形式连接Mx层和Mx + 2层。Supervia属于缩放助推器系列,用于减少轨道数量,因此可以降低标准逻辑单元的单元高度。

在其最简单的形式中,Supervia通过以自对准方式绕过中间Mx + 1层,提供从Mx到Mx + 2金属层的直接连接,Supervia和常规通孔可以在同一设计中共存。

(左)通孔电阻与面积关系(右)Supervia结构 第一个用例是SRAM结构和掩埋电源轨结构,即埋在芯片前段的电源轨,以帮助释放互连的布线资源。例如,在2019年IITC,IMEC展示了具有高良率和低电阻率的Ru回蚀刻工艺(埋入式电源轨集成的关键工艺)。

为了将Supervia结构扩展到3nm节点之外,IMEC定义了一个Supervia工艺路线图,其中包含第二代(从Mx到Mx + 3和Mx + 4)和第三代(从Mx到Mx+ 5)。这个最终的第三代,也被称为‘Ubervia’,是非常复杂和仍远未实现的。但它可以从Mx直接“跳”到更宽的金属线,从而进一步降低RC。

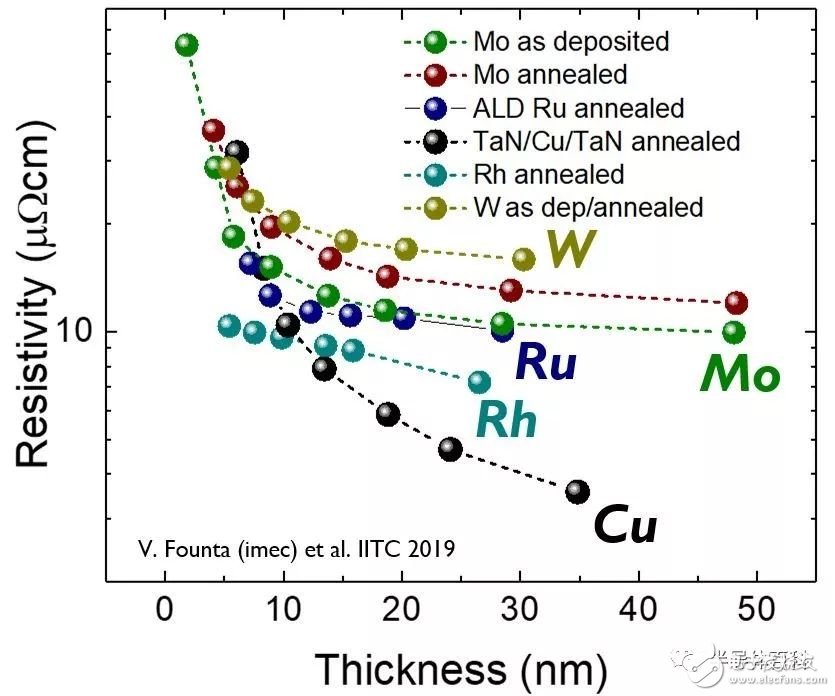

关键促成因素:替代导体

多年来,IMEC一直致力于寻找新金属,以取代传统的Cu,钨(W)和钴(Co)在各种互连中的应用。这些替代导体将是实现上述创新的关键,包括“下一代”双大马士革和半大马士革工艺,以及Supervia结构。

寻求替代金属的第一步:定义品质因数(FOM),以给候选材料进行排名。该FOM定义为体电阻率与金属中载流子平均自由程的乘积。现在科学界广泛认为Cu,W和Co是材料排名的基准点。具有最低FOM的金属是铑(Rh),然后是铂(Pt),铱(Ir),镍(Ni),Ru,钼(Mo)和铬(Cr)。然而,排名不包括成本,退火敏感度或与电介质的粘附性等指标。例如,Ir和Rh对电介质的粘附性非常差,特别是Rh非常昂贵,甚至比金(Au)贵。在实验方面,IMEC证明了Mo是一种非常有前途的互连金属,特别是作为W的潜在替代品。关于替代金属的工作已在2019年IITC上提出。

寻找替代导体:Mo的薄膜研究

该团队还研究了二元和三元化合物作为传统导体的替代品。特别是所谓的“MAX相”,其比纯单质金属有更好的性能。MAX相是由早期过渡金属(M),A族元素(A)和碳或氮(X)组成的分层结构。

最后,还可以通过用石墨烯覆盖连线来降低诸如Ru的金属的电阻率。石墨烯已知具有原子级薄,并且具有高导电性和导热性以及高载流能力。在IITC2019,IMEC证明了制造的石墨烯包覆的Ru线具有较低的电阻率和较高的热稳定性。这些发现为碳/金属互连提供了可能的途径。

向BEOL添加功能

在高级节点芯片的中间M6到M8互连级别,通孔密度相对较低,可提供实现小晶体管的空间。薄膜晶体管足够小且温度兼容,可以完成这项任务,从而为BEOL增加了额外的功能。

BEOL中的TFT:示意图

目标应用是服务器和移动应用的电源管理,双V T逻辑电路,FPGA(具有大型SRAM阵列),用于电压转换的高压I / O,用于神经形态概念的信号缓冲器(buffer)。它也可以在DRAM存储器中找到它的方式,或者用于非易失性存储器的选择器(selector)。

最终的互连梦想是将它们用作中继器,中继器在当前设计中占据了很大一部分面积。但是,由于需要n型和p型TFT,后者对于实际实现来说还达不到要求。BEOL的其他挑战包括可靠性,CMOS工艺技术的成熟度以及成本,尽管在这些“宽松”尺寸下,可以使用简单的单次浸没式光刻技术来提高其成本效益。

IMEC团队最近在300mm晶圆上提供了功能性铟镓锌氧化物(IGZO)TFT的硬件演示,即使在高温下也具有低漏电。

总结

在本文中,imec提出了几种未来的方案,这些方案有望解决RC延迟问题,并将互连扩展到3nm技术节点及更高版本。通过启用新工艺(例如半大马士革),新的缩放助推器(Supervia,以获得更好的可布线性),新材料(例如替代导体和气隙)以及通过添加功能来减小面积和降低成本。

-

CMOS

+关注

关注

58文章

6035浏览量

239158 -

半导体

+关注

关注

335文章

29026浏览量

240059 -

IMEC

+关注

关注

0文章

59浏览量

22605 -

EUV

+关注

关注

8文章

610浏览量

87365

发布评论请先 登录

华工科技携手中科大突破半导体激光退火关键技术

从原理到应用,一文读懂半导体温控技术的奥秘

电机系统节能关键技术及展望

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测

浅谈华为通信大模型的关键技术

揭秘激光锡丝焊接机在电子制造业中的关键技术

实现3nm技术节点需要突破哪些半导体关键技术

实现3nm技术节点需要突破哪些半导体关键技术

评论