格芯指出,新开发出基于ARM架构的3D高密度测试芯片,是采用格芯的12纳米FinFET制程所制造,采用3D的ARM网状互连技术,允许资料更直接的传输到其他内核,极大化的降低延迟性。而这样的架构,这可以降低资料中心、边缘运算以及高端消费者应用程式的延迟,并且提升数据的传输速度。

格芯强调,新开发出基于ARM架构的3D高密度测试芯片,可以进一步在每平方公厘上达成多达100万个3D的连接,使其具有高度可扩展性,并有望延展12纳米制成的寿命。另外,3D封装解决方案(F2F)不仅为设计人员提供了异构逻辑和逻辑/存储器整合的途径,而且可以使用最佳生产节点制造,以达成更低的延迟、更高的频宽,更小芯片尺寸的目标。

格芯表示,因为当前的12纳米制程成熟稳定,因此目前在3D空间上开发芯片更加容易,而不必担心新一代7纳米制程所可能带来的问题。然而,台积电、三星和英特尔能够在比格芯小得多的节点上开发3D芯片,而且也已经相关的报告。而何时推出,就只是时间上的问题。届时,格芯是否能以较低廉的价格优势,进一步与其他晶圆生产厂商竞争,就有待后续的观察。

-

芯片

+关注

关注

460文章

52625浏览量

442826 -

3D封装

+关注

关注

9文章

141浏览量

27880 -

格芯

+关注

关注

2文章

239浏览量

26382

发布评论请先 登录

高密度配线架和中密度的区别

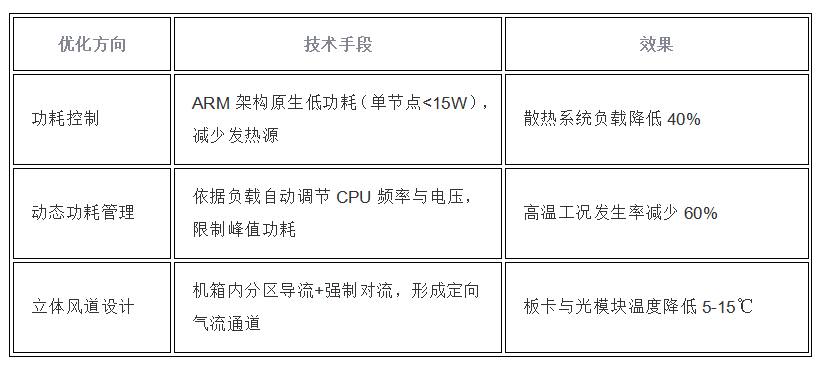

高密度ARM服务器的散热设计

合金电阻稳定性优于其他材料的深度解析

光纤高密度odf是怎么样的

电子产品更稳定?捷多邦的高密度布线如何降低串扰影响?

1u144芯高密度配线架详解

Marvell展示2纳米芯片3D堆叠技术,应对设计复杂性挑战!

高密度3-D封装技术全解析

揭秘高密度有机基板:分类、特性与应用全解析

高密度Interposer封装设计的SI分析

格芯新开发出基于ARM架构的3D高密度测试芯片 成熟稳定性优于7纳米制程芯片

格芯新开发出基于ARM架构的3D高密度测试芯片 成熟稳定性优于7纳米制程芯片

评论