Т»ЦЦёЯЛЩБчЛ®ПЯіЛ·ЁЖчЅб№№

НЖјц + Мфґн + КХІШ(0) + УГ»§ЖАВЫЈЁ0Ј©

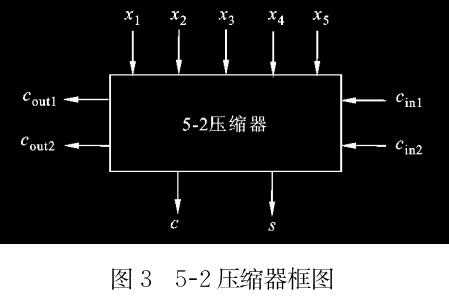

ЎЎЎЎЙијЖБЛТ»ЦЦРВУ±µД32ЎБ32О»ёЯЛЩБчЛ®ПЯіЛ·ЁЖчЅб№№Ј®ёГЅб№№ЛщІЙУГµДРВРНRadix-16 BoothЛг·ЁОьИЎБЛИЯУаBooth±аВлУлёДЅшBooth±аВлµДУЕµгЈ¬ДЬјтµҐЎўїмЛЩµШІъЙъёґФУ±¶КэЈ®ЙијЖНкіЙµДіЛ·ЁЖчЦ»ІъЙъ9ёцІї·Ц»эЈ¬УРР§ЅµµНБЛІї·Ц»эС№ЛхХуБРµД№жДЈУлСУК±Ј®НЁ№э¶Ф5ј¶БчЛ®ПЯ№ШјьВ·ѕ¶ЦРС№ЛхХуБРєН64О»і¬З°ЅшО»ЈЁCLAЈ©јУ·ЁЖчµДУЕ»ЇЙијЖЈ¬јхЙЩБЛіЛ·ЁЖчµДСУК±єНГж»эЈ®ѕПЦіЎїЙ±аіМВЯјЖчјю·ВХжСйЦ¤±нГчЈ¬УлІЙУГRadix-8 BoothЛг·ЁµДіЛ·ЁЖчПа±ИЈ¬ёГіЛ·ЁЖчЛЩ¶ИМбёЯБЛ11%Ј¬УІјюЧКФґјхЙЩБЛ3%Ј®

·ЗіЈєГОТЦ§іЦ^.^

(0) 0%

І»єГОТ·ґ¶Ф

(0) 0%

ПВФШµШЦ·

Т»ЦЦёЯЛЩБчЛ®ПЯіЛ·ЁЖчЅб№№ПВФШ

Па№ШµзЧУЧКБППВФШ

- УЕРгµДVerilog/FPGAїЄФґПоДї-ёЎµгФЛЛгЖчЈЁFPUЈ©ЅйЙЬ 885

- Alpha°лНёГчНјРОµюјУЛг·ЁMatlab+VerilogµДЙијЖКµПЦ 358

- Т»їоТФ32О»ARMCortexTM-M0ґ¦АнЖчДЪєЛОЄ»щґЎµДёЯРФјЫ±И°ІИ«MCU 350

- АіµПЛјФЪУІјюІъЖ·ІгГжНЖіцБЛЎ°Nexus+AvantЎ± 307

- УЕ»ЇµҐЖ¬»ъіМРтґъВлµДІЯВФУл·Ѕ·Ё 242

- »щУЪFPGAµДёЯР§іЛ·ЁЖч 407

- Arm HeliumјјКхµ®ЙъµДУЙАґ ОЄєОІ»Ц±ЅУІЙУГNeonЈї 1128

- verilogФЛЛг·ыµДУЕПИј¶ 1198

- ИзєОАыУГxilinxЖчјюЦРLUTµДЅб№№МШХчЙијЖіЛ·ЁЖчДШЈї 704

- ІјЛ№Лг·ЁЈЁBooth AlgorithmЈ©іЛ·ЁЖчµДVerilogКµПЦ 1308